Отчет по практической работе 8 Реализация заданной логической функции от четырех переменных на мультиплексорах 161, 81, 41, 21

Скачать 0.65 Mb. Скачать 0.65 Mb.

|

МИНИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ Федеральное государственное бюджетное образовательное учреждение высшего образования ”МИРЭА - Российский технологический университет” РТУ МИРЭА  Институт кибернетики Кафедра общей информатики ОТЧЕТ ПО ПРАКТИЧЕСКОЙ РАБОТЕ №8 «Реализация заданной логической функции от четырех переменных на мультиплексорах 16-1, 8-1, 4-1, 2-1» по дисциплине «ИНФОРМАТИКА»

Москва 2021 СОДЕРЖАНИЕ ПОСТАНОВКА ЗАДАЧИ 3 ПРОЕКТИРОВАНИЕ И РЕАЛИЗАЦИЯ 4 Восстановленная таблица истинности 4 Схемы реализующие логическую функцию на мультиплексорах требуемыми способами 5 ВЫВОДЫ 11 СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ 12 1 ПОСТАНОВКА ЗАДАЧИЛогическая функция от четырех переменных задана в 16-теричной векторной форме. Восстановить таблицу истинности. По таблице истинности реализовать в лабораторном комплексе логическую функцию на мультиплексорах следующими способами: используя один мультиплексор 16- 1, используя один мультиплексор 8-1, используя минимальное количество мультиплексоров 4-1, используя минимальную комбинацию мультиплексоров 4-1 и 2-1. F 1 : D33B16 = 1101 0011 0011 10112 (1) 2 ПРОЕКТИРОВАНИЕ И РЕАЛИЗАЦИЯДана логическая функция (1) от четырех переменных в 16-теричной векторной форме. Восстановленная таблица истинностиВосстановим таблицу истинности для нашей функции F1 (таблица 1). Таблица 1 — Таблица истинности для функции F1

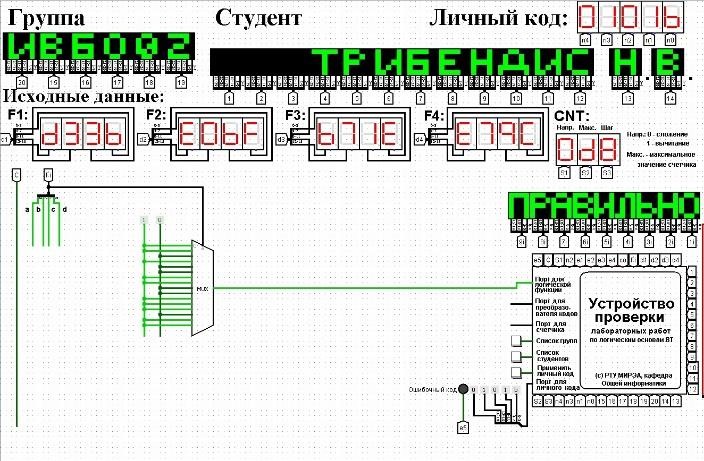

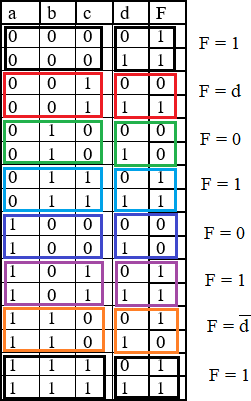

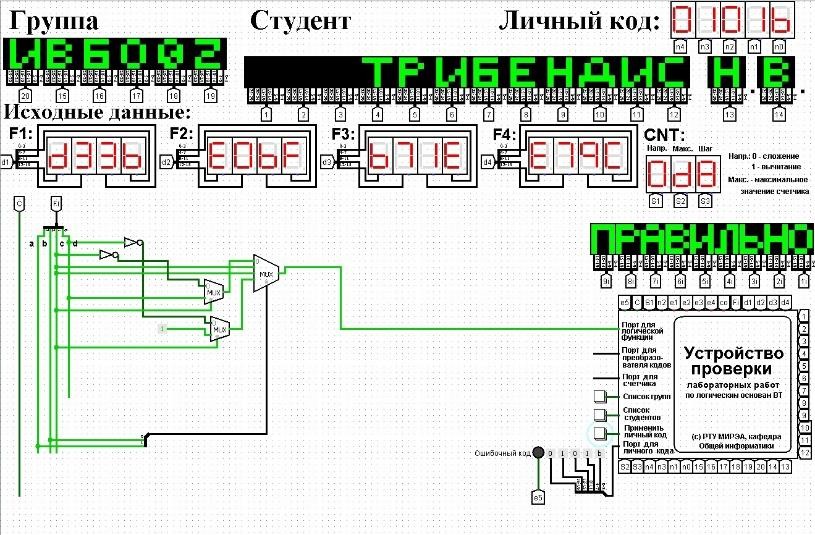

Схемы реализующие логическую функцию на мультиплексорах требуемыми способами Реализуем функцию, используя мультиплексор 16-1. Количество информационных входов мультиплексора соответствует количеству значений логической функции. Поэтому просто подадим значения функции на соответствующие входы. На адресные (выбирающие) входы мультиплексора подадим при помощи шины значения логических переменных. Несмотря на использование шины, следует помнить, что младшая переменная подается на младший адресный вход, а старшая–на старший. Собранная и протестированная схема показана на рис. 1. Тестирование подтвердило правильность работы схемы. Реализуем функцию, используя мультиплексор 16-1. Количество информационных входов мультиплексора соответствует количеству значений логической функции. Поэтому просто подадим значения функции на соответствующие входы. На адресные (выбирающие) входы мультиплексора подадим при помощи шины значения логических переменных. Несмотря на использование шины, следует помнить, что младшая переменная подается на младший адресный вход, а старшая–на старший. Собранная и протестированная схема показана на рис. 1. Тестирование подтвердило правильность работы схемы.Рисунок 1 — Тестирование схемы, реализующей логическую функцию на мультиплексоре 16-1 Далее выполним реализацию заданной логической функции при помощи мультиплексора 8-1. Мультиплексор 8-1 имеет 3 адресных входа, что не позволяет подать на эти входы все 4 логические переменные, как это было сделано в предыдущем случае. Однако мы можем в качестве адресных переменных выбрать любые три из имеющихся, а оставшуюся четвертую рассматривать наравне с логическими константами как элемент исходных данных для информационных входов. Удобнее всего в качестве адресных переменных взять три старшие пе- ременные нашей функции, т.е. a, b, c. Тогда пары наборов, на которых эти  переменные будут иметь одинаковое значение, будут располагаться в соседних строчках таблицы истинности и поэтому можно будет легко увидеть, как значение логической функции для каждой пары наборов соотносится со значением переменной d. Например на рис. 2 видно, что для некоторых строчек F= 𝑑 и F= d. Всего же для разных пар наборов может быть четыре случая: F = 0, F = 1, F = d, F = d. Таким образом, мы перенесли одну переменную в область значения функции и получили таблицу, похожую на таблицу истинности функции от трех переменных. Таблица 2 отображает «сжатую» таблицу истинности.  Рисунок 2 — Взаимосвязь значений функции и значений переменной «d» Таблица 2 — «сжатая» таблица истинности.

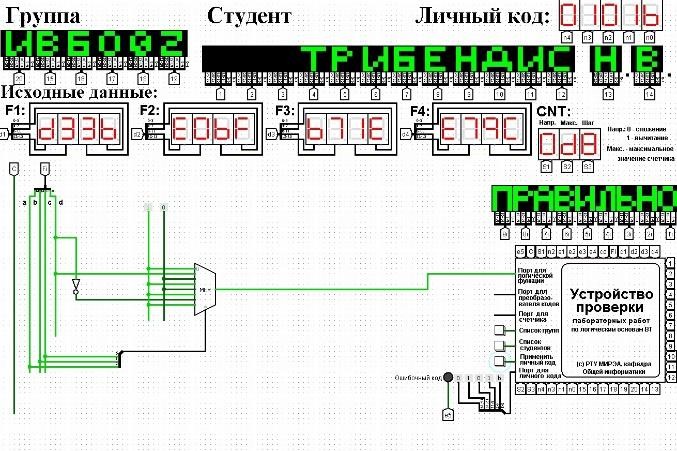

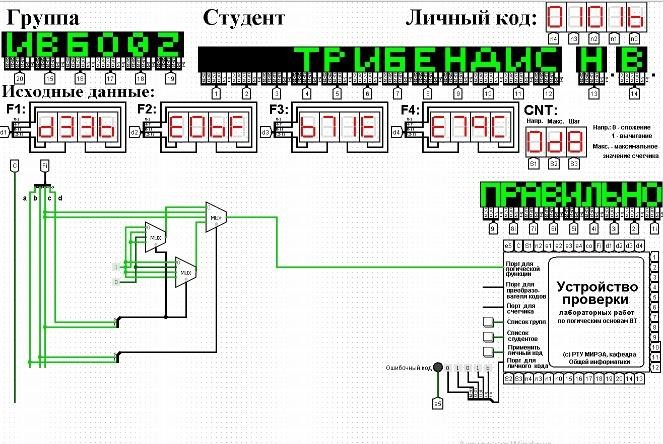

Теперь, рассматривая переменную d наравне с константами 0 и 1 в качестве сигналов для информационных входов мультиплексора 8-1, можно по аналогии с предыдущим случаем выполнить реализацию требуемой функции.  Разместим на рабочей области новый мультиплексор, установим ему количество выбирающих (адресных) входов равным трем, и выполним необходимые соединения (рис. 3). Разместим на рабочей области новый мультиплексор, установим ему количество выбирающих (адресных) входов равным трем, и выполним необходимые соединения (рис. 3).Рисунок 3 — Тестирование схемы, реализующей логическую функцию на мультиплексоре 8-1 Рассмотрим реализацию заданной функции на минимальном количестве мультиплексоров 4-1. Мультиплексор 4-1 имеет 2 адресных входа и 4 информационных. Это означает, что мы должны разбить исходную таблицу истинности на 4 фрагмента, за реализацию каждого из которых в принципе должен отвечать отдельный мультиплексор (назовем его операционным). Однако, необходимо учесть требования минимальности по отношению к количеству используемых мультиплексоров и ставить их только там, где без них нельзя обойтись. Также нам нельзя в рамках данной работы использовать другие логические схемы, за исключением отрицания. По аналогии с реализацией на дешифраторах 2-4, нам обязательно потребуется управляющий мультиплексор, который будет выбирать один из вариантов, предлагаемых операционными мультиплексорами. Разобьем исходную таблицу истинности на зоны ответственности между операционными мультиплексорами, а заодно посмотрим, нельзя ли в некоторых случаях обойтись вообще без операционного мультиплексора (рис. 4).  Рисунок 4 — Разбиение исходной таблицы истинности на зоны ответственности для потенциальных операционных мультиплексоров  Как видно из рис. 4, в трех случаях из четырех без операционного мультиплексора можно вполне обойтись, однако предпоследний фрагмент таблицы требует реализации операционного мультиплексора. С учетом только что сказанного, схема логической функции на минимальном количестве мультиплексоров 4-1 будет такой, как показано на рис. 5. Как видно из рис. 4, в трех случаях из четырех без операционного мультиплексора можно вполне обойтись, однако предпоследний фрагмент таблицы требует реализации операционного мультиплексора. С учетом только что сказанного, схема логической функции на минимальном количестве мультиплексоров 4-1 будет такой, как показано на рис. 5.Рисунок 5 —Тестирование схемы, реализующей логическую функцию на минимальном количестве мультиплексоров 4-1 Тестирование подтвердило правильность работы схемы. Реализуем логическую функцию, используя минимальную комбинацию мультиплексоров 4-1 и 2-1. В качестве отправной точки рассмотрим результаты, полученные в предыдущей реализации. Управляющий мультиплексор нельзя заменить на мультиплексор 2-1, поскольку у него на входах уникальные сигналы, а вот единственный операционный заменить можно, поскольку он имеет дело с константами. Из рис. 4 выпишем отдельно фрагмент таблицыистинности, за который данный мультиплексор отвечает (таблица 4). Таблица 4 – фрагмент таблицы истинности

Из таблицы видно, что когда «с» равно 0, то функция равна не «d», а когда  «с» равно 1, то функция равна 0. Значит, переменную «с» можно рассматривать как адресную для мультиплексора 2-1, а не «d» и 0 будут поданы на его информационные входы. В результате получим схему, изображенную на рис. 6. «с» равно 1, то функция равна 0. Значит, переменную «с» можно рассматривать как адресную для мультиплексора 2-1, а не «d» и 0 будут поданы на его информационные входы. В результате получим схему, изображенную на рис. 6.Рисунок 5 — Тестирование схемы, реализующей логическую функцию на основе минимальной комбинации мультиплексоров 4-1 и 2-1 Тестирование подтвердило правильность работы схемы. 3 ВЫВОДЫВ ходе данной практической работы данная логическая функция была реализована на мультиплексорах тремя способами: используя один мультиплексор 16-1 и 8-1 соответственно, используя минимальное количество мультиплексоров 4-1, используя минимальную комбинацию мультиплексоров 4-1 и 2-1. Была проверена работоспособность схем. 4 СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВСмирнов С.С., Карпов Д.А. Информатика: Методические указания по выполнению практических работ. / С.С. Смирнов, Д.А. Карпов—М., МИРЭА — Российский технологический университет, 2020.–102с. Воронов Г.Б. Лекции по информатике. / Г.Б. Воронов. –М.: МИР- ЭА — Российский технологический университет, 2021.: URL: https://online- edu.mirea.ru/mod/webinars/view.php?id=262229 (дата обращения 21.10.2021) |