Билеты. Позиционные системы счисления (с основанием 2,8,10,16,n) Преобразование из одной системы в другую. Выполнение арифметических операций

Скачать 4.45 Mb. Скачать 4.45 Mb.

|

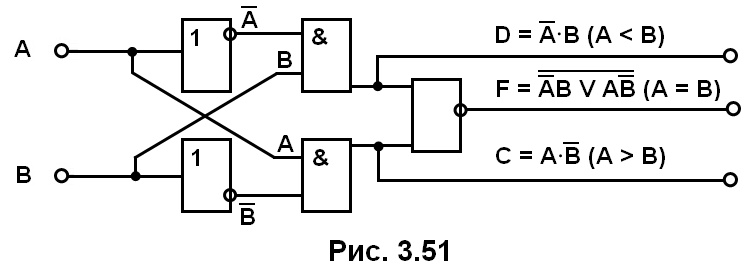

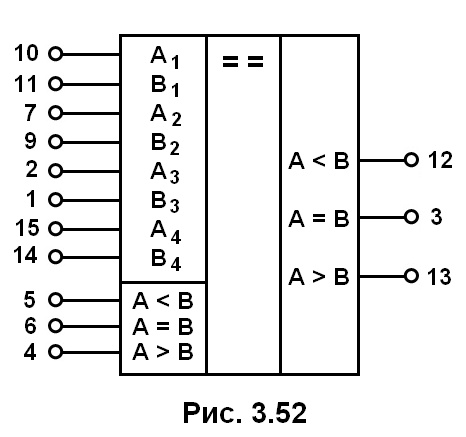

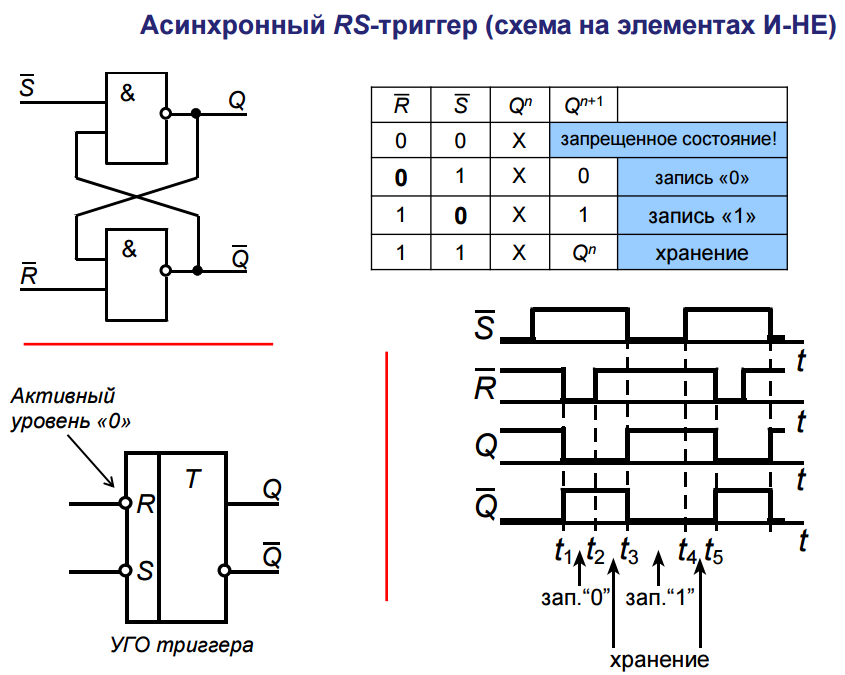

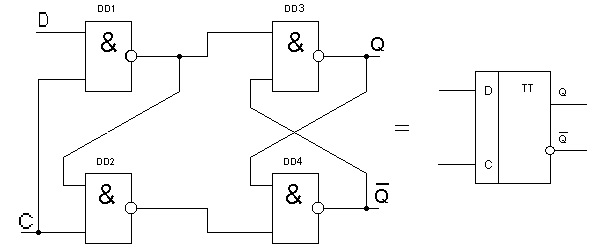

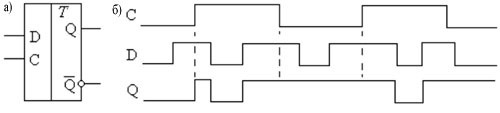

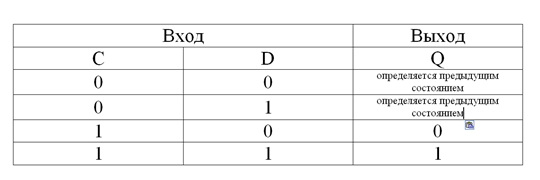

Цифровые компараторыЦифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел A и B с одинаковым количеством разрядов либо вид неравенства A> B или A < B. Цифровые компараторы имеют три выхода. Схема одноразрядного компаратора представляет собой структуру логического элемента «исключающее ИЛИ-НЕ» (рис. 3.51).  Из анализа схемы следует, что если A= B, то F = 1, в противном случае, т. е. при А ≠ В, F = 0. Если А > В, т. е. А = 1, В = 0, то С = 1, а если А < В, т. е. А = 0, В = 1, то D = l. Если попарно равны между собой все разряды двух n-разрядных двоичных чисел, то равны и эти два числа А и В. Применяя цифровой компаратор для каждого разряда, например, четырехзначных чисел, и определяя значения F1, F2, F3, F4 логических переменных на выходах компараторов, факт равенства А = В установим в случае, когда F = F1 · F2 · F3 · F4 = 1. Если же F = 0, то А ≠ В. Неравенство А > В обеспечивается (для четырехразрядного числа) в четырех случаях: или А4 > В4, или А4 = В4 и А3 > В3, или А4 = В4, А3 = В3 и А2 > В2, или А4 = В4, А3 = В3, А2 = В2 и A1 > В1 (где А4 и В4 — старшие разряды чисел А и В). Очевидно, что если поменять местами А1 и B1, то будет выполняться неравенство А < В. Цифровые компараторы выпускают, как правило, в виде самостоятельных микросхем. Так, микросхема К564ИП2 (рис. 3.52) является четырехразрядным компаратором, в котором каждый из одноразрядных компараторов аналогичен рассмотренной ранее схеме. Данная микросхема имеет расширяющие входы А < В, А = В, А > В, что позволяет наращивать разрядность обоих чисел. Для этого компараторы соединяют каскадно или параллельно (пирамидально).  Рассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А < В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А < В, А = В, А > В микросхемы младших разрядов подают соответственно потенциалы U0 и U1 (U0 соответствует логическому 0, a U1 — «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1. Рассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А < В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А < В, А = В, А > В микросхемы младших разрядов подают соответственно потенциалы U0 и U1 (U0 соответствует логическому 0, a U1 — «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1.Микросхемы АЛУ. Условное графическое обозначение. Назначение выводов. Принцип работы. Пояснить принцип действия с помощью временных диаграмм. АЛУ – узел электроно- вычислительных устройств предназначенных для выполнения логических, арифметических операций, операций сравнения  A,B – входы операндов S- входы выбора операций Ci- вход переноса M(mode) – вход задающий тип выполняемых операций(M=1 логические; M=0 арифметические) F – выходы результата G – выход фунции генерации(исп для параллельного переноса при наращ разрядности) H – выход функции прозрачности(исп для параллельного переноса при наращ разрядности) C  o – выходной перенос o – выходной переносA=B – выход сравнения на равенство с открытым коллектором Два многоразрядных операнда (числа, буквы, символы и т.д.), подлежащие обработке в АЛУ, подаются на входы А и В. Результат выполнения операции появляется на выходе F. Вид операции, выполняемой в АЛУ, определяется сигналами, которые подаются на входы S и M. Таким образом при сложении чисел 2 и 3 одно из них подаѐтся на вход А, а второе на - вход В. В этот момент времени на шины S и М подаѐтся двоичное число, которое на естественном языке означает команду (приказ) «Выполнить арифметическое сложение». Результат сложения – число 5 появляется на выходе F. У входов M и S одинаковое назначение – определять вид выполняемой в АЛУ операции. Эти входы разделены лишь с методической целью. Сигнал на входе М (Mode – режим) определяет, какую операцию будет выполнять АЛУ – логическую или арифметическую. Асинхронные RS-триггеры. Условное графическое обозначение. Назначение выводов. RS-триггеры RS-триггер — это триггер с раздельной установкой состояний логического нуля и логической единицы (с раздельным запуском). Он имеет два информационных входа S и R. По входу S триггер устанавливается в состояние Q = 1 ( Q = 0), по входу R — в состояние Q = 0 ( Q =1). Асинхронные RS-триггеры. В асинхронных триггерах срабатывание происходит непосредственно в момент изменения сигнала на информационных входах. Асинхронные -RS-триггеры являются наиболее простыми. В качестве самостоятельного устройства используются редко, но являются основой для построения более сложных систем. S — раздельный вход установки триггера в единичное состояние по прямому выходу Q (Set — установка); Q = 1; R — раздельный вход установки триггера в нулевое состояние по прямому выходу Q (Reset — сброс); Q= 0;     Синхронные RS-триггеры. Условное графическое обозначение. Назначение выводов. Виды синхронизации. Пояснить принцип действия с помощью временных диаграмм. Синхронный RS-триггер снабжён синхронизирующим входом С, который разрешает приём сигналов с информационных входов R и S. Если на синхронизирующий вход С поступает сигнал лог.0, то любые логические сигналы, подаваемые на информационные входы R и S, не влияют на состояние триггера. При подаче на синхронизирующий вход С сигнала лог.1, синхронный RS-триггер работает в режиме асинхронного RS-триггера.   D-триггеры. Условное графическое обозначение. Назначение выводов. Виды синхронизации. Пояснить принцип действия с помощью временных диаграмм. Реализация на основе JK-триггера. Триггер задержки, который используют для создания регистров сдвига и регистров хранения, неотъемлемая часть любого микропроцессора.  Рис. 9. Схема D-тригера Имеет два входа – информационный и синхронизации. При состоянии С=0 тригер устойчив и при этом сигнал на выходе не зависит от сигналов, поступающих на информационный вход. При С=1 на прямом выходе информация будет точно повторять ту информацию, которая подается на вход D. На временной диаграмме приведен принцип работы D-триггера  Рис.10. D-триггер. а) схематическое изображение б) временная диаграмма работы Таблица истинности D-триггера:  Т-триггеры. Условное графическое обозначение. Назначение выводов. Пояснить принцип действия с помощью временных диаграмм. Реализация на основе JK‑триггера. T-триггер — это счетный триггер. У данного триггера имеется только один вход. Принцип работы T-триггера заключается в следующем. После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T триггер как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние.  Условно-графическое обозначение T триггера Временная диаграмма T триггера приведена на рисунке 2. При построении этой временной диаграммы был использован триггер, работающий по заднему фронту синхронизирующего сигнала.  Рисунок 2. Временные диаграммы T триггера Если соединить вместе входы J и K, то JK – триггер превратится в Т – триггер. JK‑триггеры. Условное графическое обозначение. Назначение выводов. Пояснить принцип действия с помощью временных диаграмм. Реализация других типов триггеров с помощью JK‑триггера. JK – триггер – это схема с двумя устойчивыми выходными состояниями и двумя входами J и К   Структура синхронного JK-триггера с входами асинхронной установки (а) и его условное графическое обозначение (б). Приводить временные диаграммы работы JK-триггера не имеет смысла, так как они совпадают с приведёнными ранее временными диаграммами RS- и T-триггера.

Счетчики. Классификация. Реализация на триггерах. Пояснить принцип действия с помощью временных диаграмм. Наращивание разрядности. Счетчиками называют устройства для подсчёта числа поступивших на их вход импульсов (команд), запоминания и хранения результата счёта и выдачи этого результата. По принципу действия(направлению счета): Суммирующие(Зарегетрированное в счетчике число увеличивается) Вычитающие(Зарегестрированное в счетчике число уменьшается) Реверсивные(вычитается и складывается) По логике(последовательности работы) Асинхронные(переключение элементов счетчика происходит последовательно) С  инхронные( переключение элементов одновременное) инхронные( переключение элементов одновременное)А  синхронный суммирующий счетчик: синхронный суммирующий счетчик: Асинхронный вычитающий   Регистры. Классификация. Реализация на триггерах. Пояснить принцип действия с помощью временных диаграмм. Наращивание разрядности. Регистры — это устройства, предназначенные для приема, хранения и передачи информации представленной в виде двоичных слов. В зависимости от функционального назначения: регистры памяти (хранения) регистры сдвига сдвигающие регистры в зависимости от способа ввода и вывода информации параллельные, последовательные комбинированные (последовательно-параллельные) по направлению передачи информации (сдвига) однонаправленные реверсивные. Регистр хранения 3битовый Каждый триггер может хранить один разряд (бит) числа. Вход R служит для установки выходов всех триггеров в нулевое (исходное) состояние перед записью числа, которое подается на входы D0,D1 и D2. При подаче импульса на вход C производится запись информации с этих входов. Информация может храниться сколь угодно долго, пока на вход С не подаются импульсы и подается питание.   Р   егистр сдвига предназначен для преобразования информации путем ее побитного сдвига в ту или иную сторону. Информация в виде логического уровня подается на вход первого (крайнего слева) триггера. При воздействии импульса на входе C присутствующая на входе D информация записывается в первый триггер. При подаче второго импульса информация из первого триггера переписывается во второй триггер, а в первый записывается информация, которая в этот момент присутствует на входе D, и так далее. Таким образом, с подачей каждого синхроимпульса информация в регистре сдвигается вправо на 1 разряд. егистр сдвига предназначен для преобразования информации путем ее побитного сдвига в ту или иную сторону. Информация в виде логического уровня подается на вход первого (крайнего слева) триггера. При воздействии импульса на входе C присутствующая на входе D информация записывается в первый триггер. При подаче второго импульса информация из первого триггера переписывается во второй триггер, а в первый записывается информация, которая в этот момент присутствует на входе D, и так далее. Таким образом, с подачей каждого синхроимпульса информация в регистре сдвигается вправо на 1 разряд.Микросхемы памяти. Классификация. Условное графическое обозначение. Наращивание емкости. |