Билеты. Позиционные системы счисления (с основанием 2,8,10,16,n) Преобразование из одной системы в другую. Выполнение арифметических операций

Скачать 4.45 Mb. Скачать 4.45 Mb.

|

|

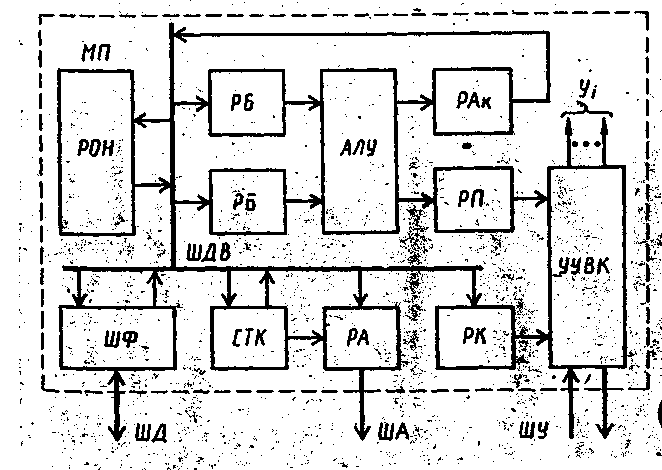

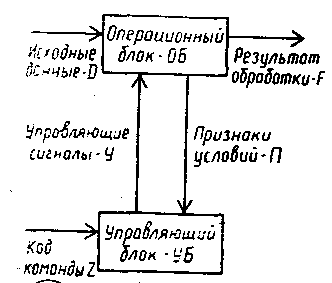

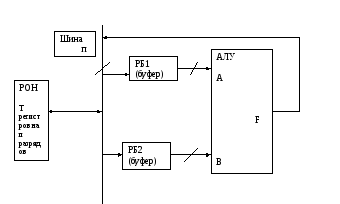

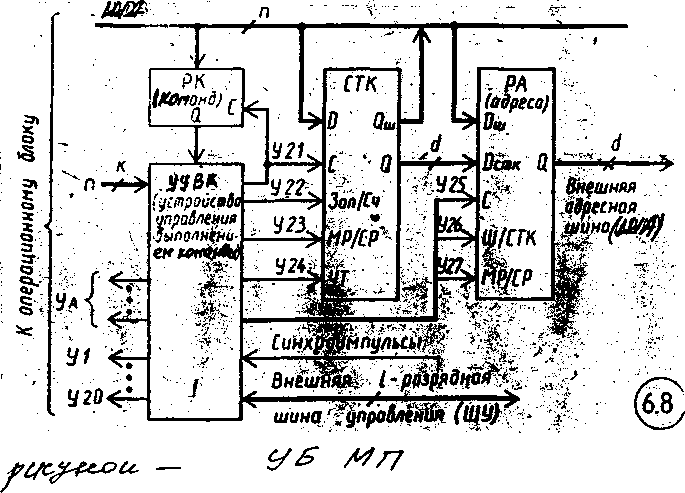

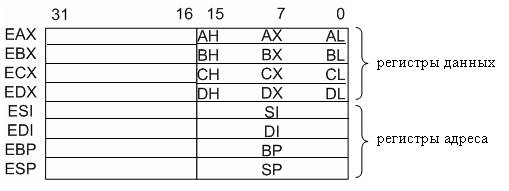

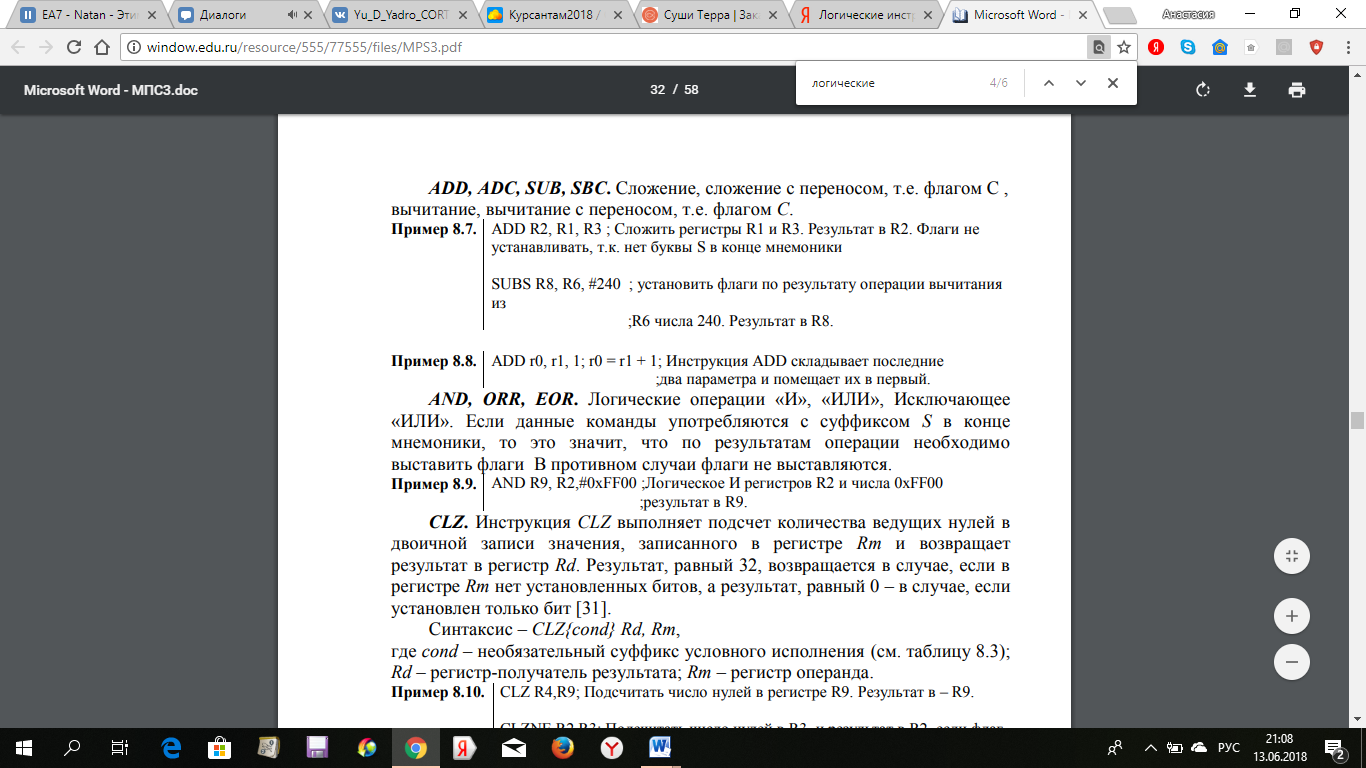

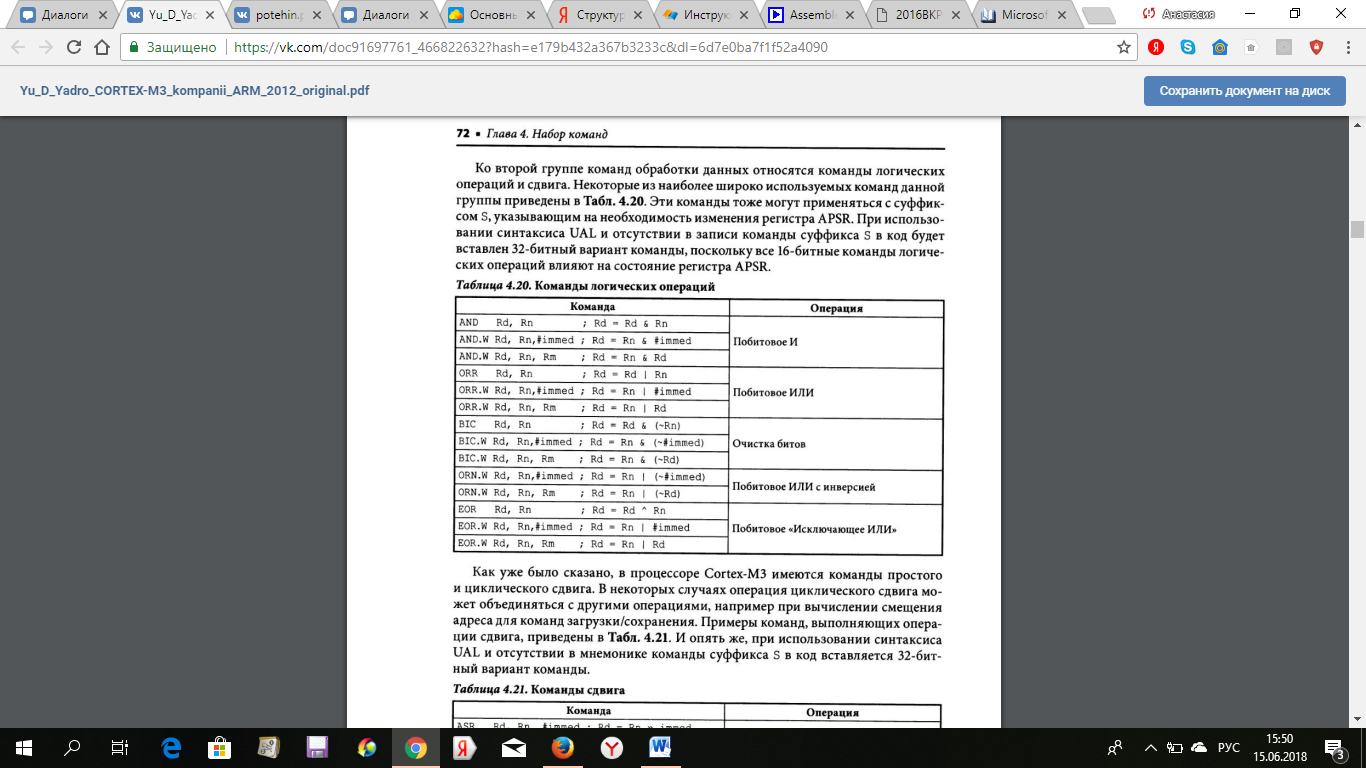

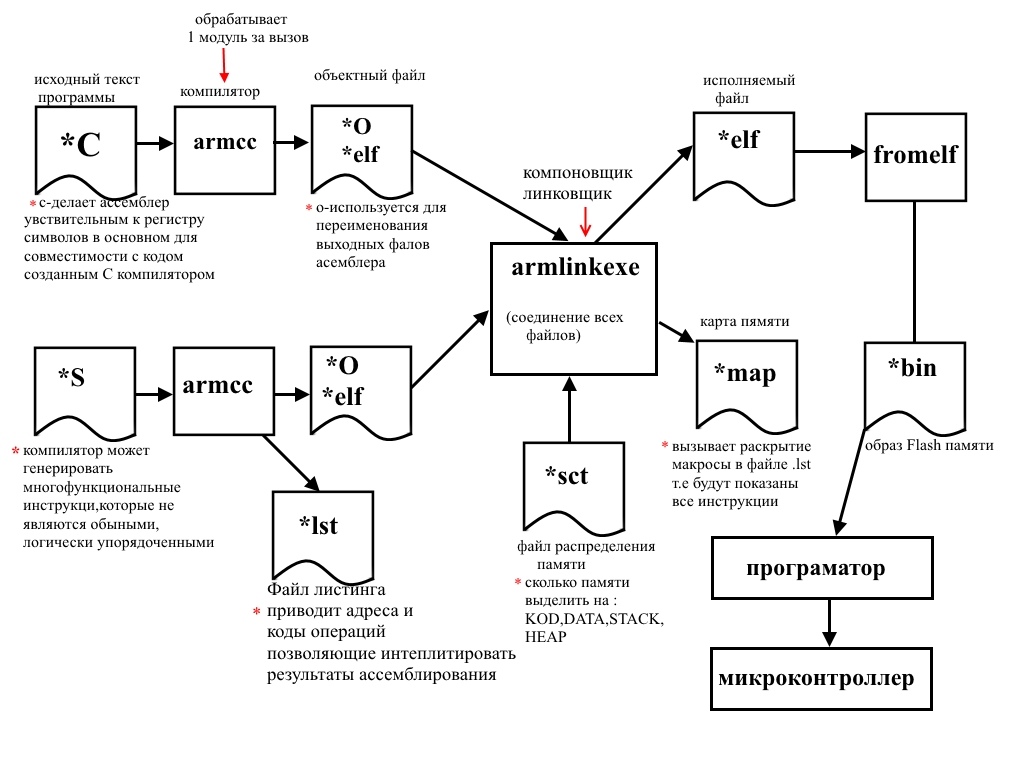

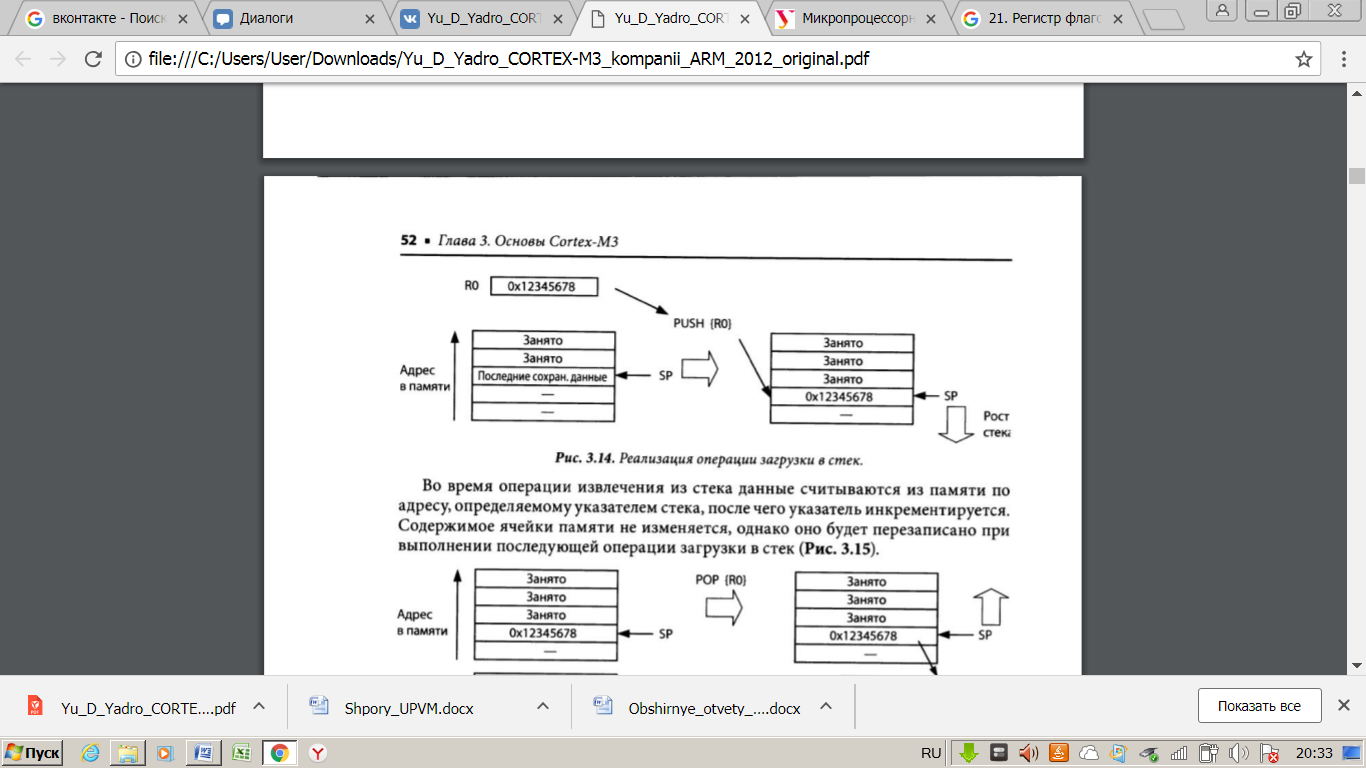

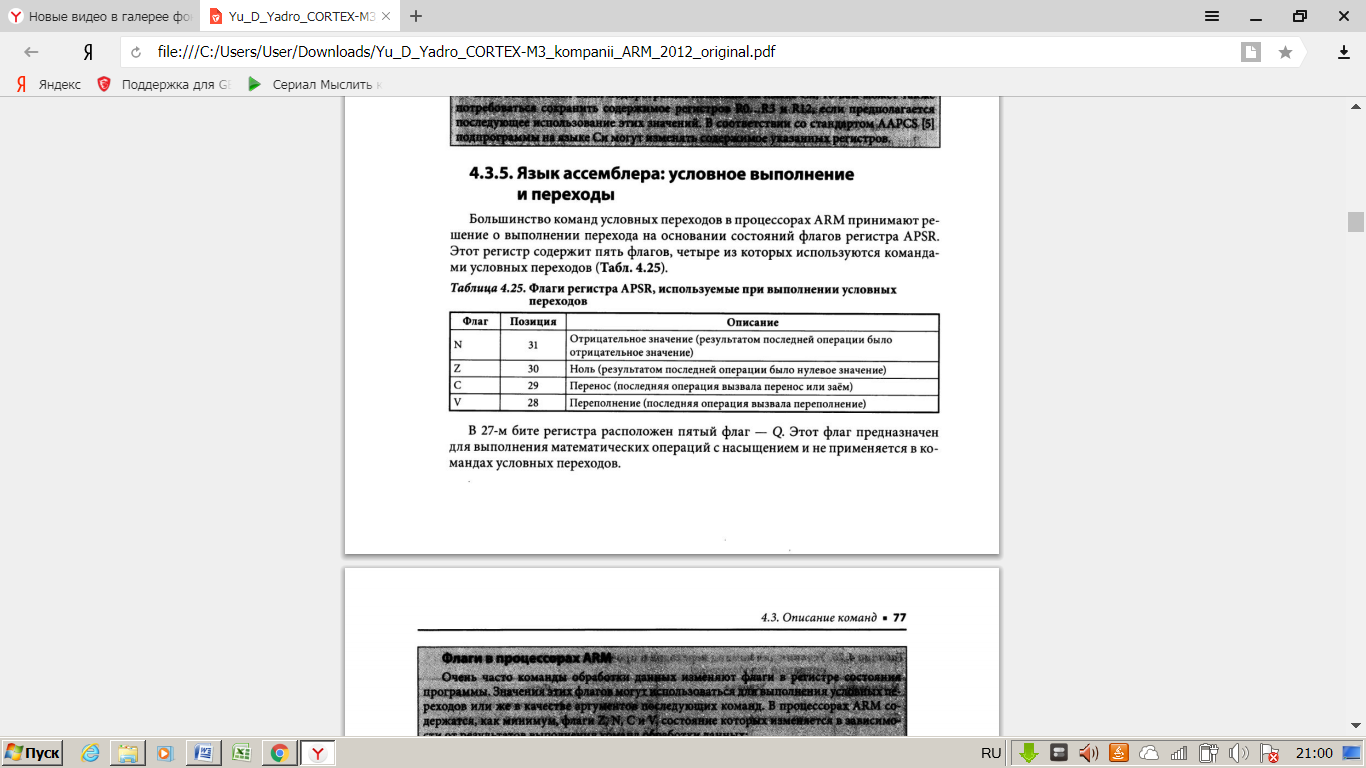

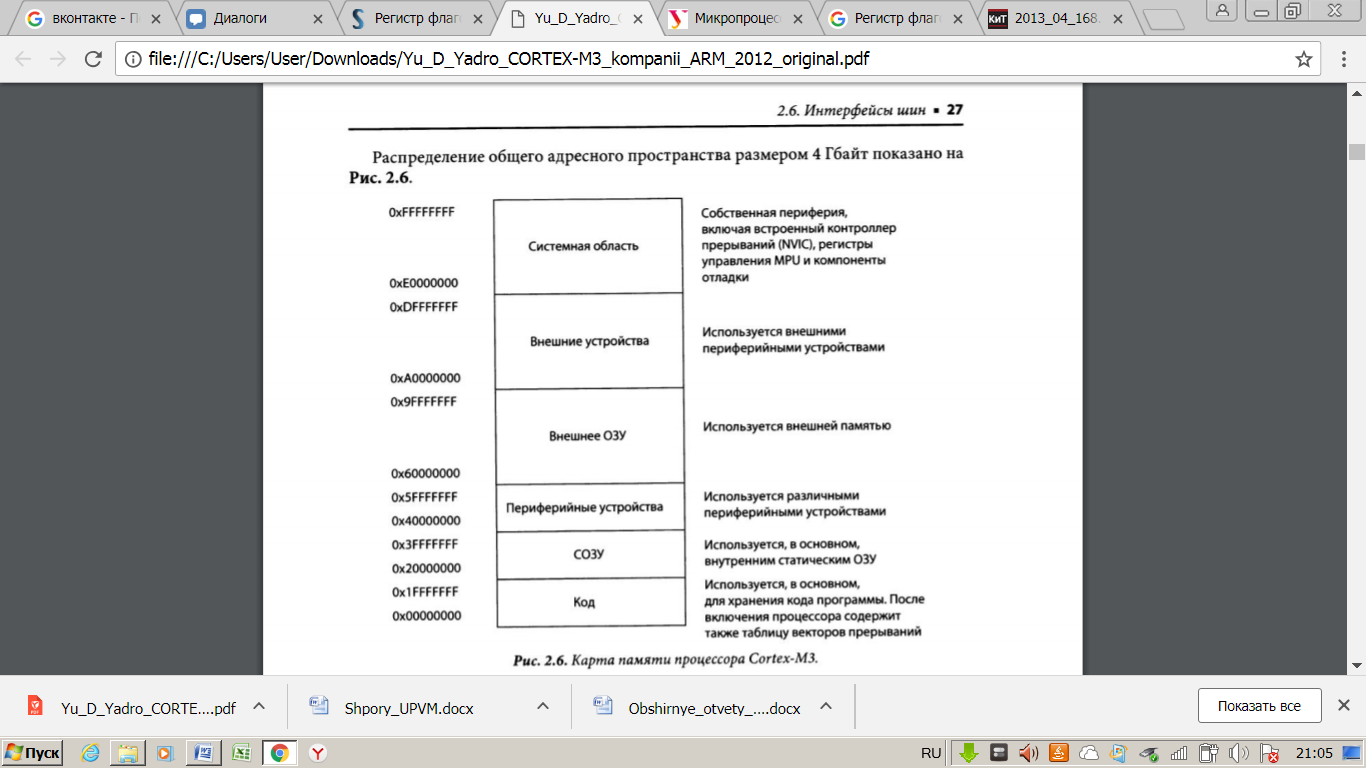

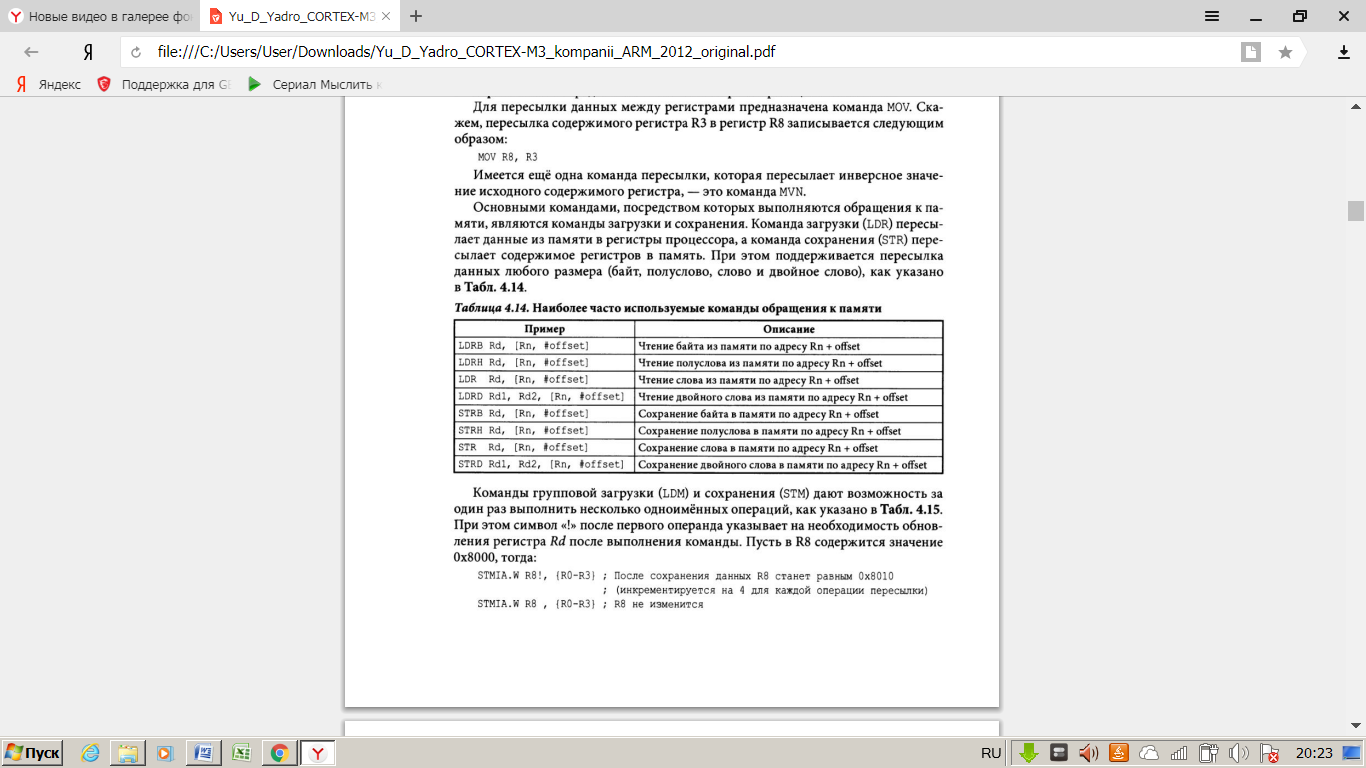

Микросхемы памяти (или просто память, или запоминающие устройства — ЗУ) предназначены для запоминания, хранения массивов информации, проще говоря, наборов, таблиц, групп цифровых кодов. Каждый код хранится в отдельном элементе памяти, называемом ячейкой памяти. два основных типа памяти: ОЗУ (оперативное запоминающее устройство) - почти тоже самое, только данные хранятся там до момента отключения питания, после повторного отключения питания - на микросхемах ОЗУ теряется вся информация  ПЗУ (постоянное запоминающее устройство) место для энергонезависимого хранения данных, по другому EEPROM(репрограммируемое пзу). На микросхемах ПЗУ информация может храниться очень долго, и при отключении питания информация не удаляется.   18) Структурная схема микропроцессора. Основные блоки, их назначения.   Рис. Структура МП. МП образуют два блока- операционный блок и управляющий блок. Управляющий блок воспринимает подкоманду и вырабатывает управляющий сигнал, подаваемый на ОБ, который по этому сигналу принимает исходные данные и выполняет с ними необходимые действия. Результат действия отправляется на шину данных МП. Признаки результата действия отправляются для анализа и принятия решения на УБ. Оба блока состоят из комбинационных и запоминающих устройств. Процесс выполнения команды в ЭВМ происходит за несколько машинных тактов. Например, в первый интервал производятся прием и запоминание одного числа, во втором такте – другого, в третьем такте – нахождение суммы этих чисел и т.д. Каждая из элементарных операций, выполняемых за один такт, называется микрооперацией. Временная последовательность работы процессора определяется программой → командой → микрокомандой (микрооперациями). Интервал времени, за который выполняется микрокоманда, называется машинным тактом, а время, необходимое для выполнения команды, - машинным циклом. ЗУ, входящие в состав процессора, выполнены в виде отдельных быстродействующих регистров и называются местной регистровой памятью. Скорость обращения к этим регистрам значительно больше, чем к основной памяти ЭВМ, и поэтому местную память называют также сверхоперативным запоминающим устройством (СОЗУ). Операционный блок.  Рис. Операционный блок Основой операционного блока (ОБ) микропроцессора является арифметически-логическое устройство (АЛУ), предназначенное для программируемой обработки информации. Помимо АЛУ в состав операционного блока входит часть СОЗУ, представленная группой регистров общего назначения (РОН) и буферными регистрами (РБ). Эти регистры имеют ту же разрядность, что и АЛУ и соединены в одну систему (операционный блок) при помощи общей n-разрядной шины данных. В РОН хранятся числа, подлежащие обработке и результаты обработки. Микрокоманды, выполняемые этим операционным блоком: - запись слова, находящегося на шине данных, в любой регистр общего назначения или буферный регистр; - выборка слова из любого РОН на шину данных; - выполнение одной из 32 арифметическо-логических операций над содержимым двух буферных регистров РБ и запись результата в любой свободный РОН. Управляющий блок микропроцессора выполняет две основные функции: - производит выборку команд программы в необходимом порядке из внешнего ЗУ; - дешифрует выбранную команду и управляет выполнением микроопераций и микрокоманд в течение одного машинного цикла. Для выполнения перечисленных функций в состав управляющего блока входят соответствующие аппаратные средства: счетчик команд (СТК), регистр адреса (РА), регистр команд (РК) и устройство управления выполнением команды (УУВК). Счетчик команд определяет очередность выборки команд из ЗУ. Команды в программе располагаются одна за другой в определенном порядке. Обычно каждая следующая команда имеет адрес, на единицу больший адреса предыдущей команды. Регистр команд (РК) предназначен для хранения кода выполняемой команды. Сменить информацию в этом регистре можно только после выполнения всех микрокоманд, составляющих текущую команду. После выборки команды из ЗУ она поступает в устройство управления выполнением команды УУВК. УУВК состоит из дешифратора команд ДК, устройства памяти микрокоманд ПЗУМК, счетчика микрокоманд СТМК и устройства управления выполнением микрокоманд УУВМК. Дешифратор команд DК расшифровывает код команды с учетом признаков П выполнения логических условий в предыдущем машинном цикле (при выполнении предыдущей команды).  Рисунок – УБ МП. 19) РОНы микропроцессора Cortex-M3.  Восемь 32-хразрядных РОНов предназначены для хранения операндов и адресов, и располагаются в операционном блоке. Младшие разряды РОНов (с 0 по 15) доступны отдельно при использовании имен AX, BX, CX, DX, SI, DI, BP, SP. При операциях с байтами для 4-х верхних регистров можно отдельно обращаться к младшему байту по, именам AL, BL, CL, DL и к старшим байтам по именам АН, ВН, СН, DH. Верхние 4 регистра используются для хранения операнда и позволяют выполнять операции над отдельными байтами, 16-разрядными словами и 32-разрядными двойными словами. Остальные (4 нижних) регистра используются как адресные регистры для хранения 16-разрядных и 32-разрядных адресов. Регистр ESP используется как указатель вершины стека. EBP – используется как базовый регистр. А регистры EDI и ESI используются как индексные регистры (для хранения индексов). В качестве базового и индексного регистров в некоторых случаях может использоваться и регистр данных EBX. 33. Подпрограммы. Назначение, структура, способы передачи входных и выходных параметров. Подпрограмма – отдельная структурная единица, имеющая собственное имя и реализующая вспомогательный алгоритм, который неоднократно используется в основной программе или другой подпрограмме с различными значениями некоторых величин, называемых параметрами. Для того чтобы использовать подпрограмму, ее необходимо описать, а затем в нужном месте основной программы или другой подпрограммы обратиться к ней с конкретными значениями параметров. При вызове подпрограммы (обращении к ней) в начале вычисляется выражения, являющиеся формальными параметрами, затем в стеке выделяется память для хранения формальных параметров в соответствии с их типом и каждому из них присваивается значение фактического параметра. Существует 2 способа передачи параметров – по значению и по адресу. При п.п. по значению в стеке сохраняются копии значений фактических параметров и доступ к исходным значениям их становится невозможным, так что значения в подпрограмме не могут быть изменены. Для передачи по адресу в стеке сохраняются адреса аргументов, и подпрограмма обращается по этим адресам к фактическим параметрам и т.о. можно изменить их первоначальные значения. Формальные параметры делятся на входные и выходные. Значения входных параметров должны быть известны до обращения к подпрограмме. Вх. параметры могут передаваться как по значению, так и по адресу. Входными параметрами могут быть выражения, в том числе константы и переменные. Выходные параметры могут передаваться только по адресу. Описание подпрограммы в языке ассемблер имеет следующую структуру: <имя процедуры> proc <тип процедуры> . . . операторы тела подпрограммы . . . ret [<выражение>] <имя процедуры> endp <тип процедуры> - определяет тип перехода: near (близкий), far (дальний). Если тип не задан, по умолчанию принимается near. Тип перехода near показывает, что тело процедуры описано в том же сегменте, что и её вызов. Тип перехода far обеспечивает вызов процедуры из других сегментов, с другим значением регистра CS. Такие процедуры обычно используются как отдельные объектные модули или в составе библиотек. ret [<выражение>] - выполняет возврат из процедуры в вызывающую программу. В зависимости от типа процедуры, эта команда восстанавливает из стека значение IP (ближний вызов) или CS:IP (дальний вызов). Эта команда не обязана быть последней по тексту процедуры, но является последней по порядку выполнения. Значение <выражение> указывает размер стека в байтах, восстанавливаемого при возврате из процедуры. Восстановление стека необходимо производить при передаче параметров процедуры через стек. Так как работа со стеком выполняется словами, значение <выражение> всегда должно быть кратным двум. Допускается вложение описания подпрограммы внутрь описания другой подпрограммы. 28. Логические инструкции микропроцессора Cortex-M3. Примеры.   30. Этапы создания исполняемого файла для микропроцессора Cortex-M3.  29. Инструкции передачи управления микропроцессора Cortex-M3. Примеры. (можно разбить) передача управления осуществляется с помощью инструкций безусловных и условных переходов, вызовов процедур и прерываний (исключений). Безусловный переход (JMP) может быть как внутрисегментным (ближним или коротким), так и межсегментным (дальним). Адрес перехода может непосредственно указывать в команде, а при косвенной адресации адрес перехода находится в регистре или памяти и может иметь дополнительные слагаемые. Короткий переход (short) может передавать управление только на адрес назначения, удаленный от текущего в пределах от –128 до +127 байт, ближний (near) – в пределах сегмента. При дальнем (far) переходе адрес назначения (непосредственный или косвенный) включает новое значение указателя инструкций и значение (или селектор) сегмента кода, обеспечивая доступ к любой точке памяти (в пределах, разрешенных защитой). Условные переходы в 8086 и 80286 возможны только короткие (8–байтовое смещение), процессоры 386+ допускают переход в пределах 16– или 32–байтного смещения, в зависимости от режима адресации. Условные переходы выполняются по состоянию флагов и/или содержимому регистра CX (ECX). Инструкции циклов комбинируют условный переход с декрементом регистра CX (ECX). Инструкция вызова процедуры (CALL) передает управление в точку перехода, сохраняя адрес следующей за ней инструкции в стеке. По инструкции возврата (RET) этот адрес восстановится в указатель инструкций (и в CS при дальнем вызове). Как и безусловный переход, вызов и возврат могут быть как внутрисегментным (ближним), так и межсегментным, допуская те же режимы адресации. 34. Директивы резервирования памяти. AREA- указывает асемблеру начало новой секции кода или данных. Синтаксис: AREA имя_секции {,атрибут 1}{,атрибут 2} Имя секции обязательный параметр. Атрибуты: CODE- секция содержит машинные инструкции. Секции с атрибутом CODE по умолчанию имеют атрибут READONLY READONLY- указывает что запись в данную секцию запрещена READWRITE- указывает компилятору, что разрещена запись и чтерие секций DATA- секция содержит данные. Секции с атрибутом DATA поумолчанию имеют атрибут READWRITE GROUP=имя_группы- указагие включить данную секцию в группу NOINIT-указывает, что секция данных содержит неинициализированные данные или инициализированные нулями. DCB- резервирование одного (или нескольких байт) и присвоение начального значения. Синтаксис: {метка(имя}DCB выражение1{выражение 2} Пример: Var1 DCB 5 MAS DCB Ox34,28,-23,2_100100110 SYM DCB “Y” DSW- резервирование одного( или нескольких полуслов) выровненных по границе 2-байтного слова и присвоение начального значения Синтаксис: {метка(имя}DSW выражение1{выражение 2} Пример: Var1 DSW 45 DCWU- тоже самое, но без выравнивания SPACE-резервирует блок памяти заполненный нулями FILL- резервирует блок памяти заполненный заданным значением Синтаксис: {метка}SPACE выражение {метка}FILL выражение{, значение{,размер}} Размер=[1,2,4], по-умолчанию=1 (в байтах) DCQ- резервирование одного (или нескольких) 64-слов выровненных по границе 4-байтного слова и присвоение начального значения DCQU- то же самое но без выравнивания Синтаксис: {метка} DCQ значение{, значение} {метка}DCQU значение{, значение} DCD -резервирование одного (или нескольких) 32-слов выровненных по границе 4-байтного слова и присвоение начального значения DCDU-то же самое но без выравнивания Синтаксис: {метка} DCDзначение{, значение} {метка}DCDU значение{, значение} 20.В процессе Cortex-M3 используется модель полного убывающего стека. Указатель стека указывает на последнее значение ,помещенное в стек,и инкретементируется перед выполнением новой операции загрузки в стек.  Во время операции извлечения из стека данные считываются из памяти по адресу, определяемому указателем стека, после чего указатель инкрементируется. Содержимое ячейки памяти не изменятеся ,однако оно будет перезаписано при выполнении последующей операции загрузки в стек. В процессоре Cortex-M3 в качестве указателя стека используется регистр R13. При возникновении прерывания некоторые регистры будут автоматически сохранены в стеке. При возврате из обработчика прерывания эи регистры также автоматически будут восстановлены из стека, а значения указателя стека изменится следующим образом. Два указателя стека: основной MSP и дополнительный PSP. Используемый в настоящей момент указатель определяется битом 1 регистра управления(CONTROL[1]). Если бит (CONTROL[1]) сброшен в 0,то указатель MSP используется в обоих режимах работы процессора. В этом случае и основная программа, и обработчики исключений задействуют под стек одну и ту же область памяти. Такое поведение используется по умолчанию после включения процессора. Если бит CONTROL[1] установлен в 1,то в режиме потока используется указатель PSP.В этом случае основная программа и обработчики прерываний задействуют под стеки разные области памяти. Это позволяет предотвратить порчу стека.( При автоматическом сохранении и восстановлении регистров будет использоваться дополнительный стек,тогда как при стековых операциях внутри обработчиков-основной стек) 21. Регистр, использующийся при выполнении большинства команд, – регистр флагов. Как и раньше, его младшие 16 бит, представлявшие собой весь этот регистр до процессора 80386, называются FLAGS.  CF – флаг переноса. Устанавливается в 1, если результат предыдущей операции не уместился в приёмнике и произошёл перенос из старшего бита или если требуется заём (при вычитании), в противном случае – в 0. PF – флаг чётности. Устанавливается в 1, если младший байт результата предыдущей команды содержит чётное число битов, равных 1, и в 0, если нечётное. Число делится на два без остатка, если его самый младший бит равен нулю, и не делится, когда он равен 1. AF – флаг полупереноса или вспомогательного переноса. Устанавливается в 1, если в результате предыдущей операции произошёл перенос (или заём) из третьего бита в четвёртый. ZF – флаг нуля. Устанавливается в 1, если результат предыдущей команды – ноль. SF – флаг знака. Он всегда равен старшему биту результата. TF – флаг ловушки. Он был предусмотрен для работы отладчиков, не использующих защищённый режим. Установка его в 1 приводит к тому, что после выполнения каждой программной команды управление временно передаётся отладчику (вызывается прерывание 1). IF – флаг прерываний. Сброс этого флага в 0 приводит к тому, что процессор перестаёт обрабатывать прерывания от внешних устройств. DF – флаг направления. Он контролирует поведение команд обработки строк: когда он установлен в 1, строки обрабатываются в сторону уменьшения адресов, когда DF = 0 – наоборот. OF – флаг переполнения. Он устанавливается в 1, если результат предыдущей арифметической операции над числами со знаком выходит за допустимые для них пределы. Флаги IOPL (уровень привилегий ввода-вывода) и NT (вложенная задача) применяются в защищённом режиме. Последний регистр FLAGS – это регистр состояния процессора .Из его 16 разрядов используются только девять. CF– флаг переноса при арифметических операциях, PF– флаг четности результата, AF – флаг дополнительного переноса, ZF– флаг нулевого результата, SF – флаг знака (совпадает со старшим битом результата), TF – флаг пошагового режима (используется при отладке), IF – флаг разрешения аппаратных прерываний, DF– флаг направления при строковых операциях, OF– флаг переполнения. Биты регистра состояния устанавливаются или очищаются в зависимости от результата исполнения предыдущей команды и используются некоторыми командами процессора. 22.В процессоре Cortex-M3 используется фиксированное распределение адресного пространства. Это позволяет обращаться к встроенным периферийным устройствам, таким как контроллер прерываний и компоненты системы отладки, посредством обычных команд доступа к памяти. То есть большинство системных функций можно использовать напрямую из программ, написанных на языке Си. Предоопределенная карта памяти также обеспечивает чрезвычайно высокую скорость работы процессора и облегчает его интеграцию в системы на кристалле.  Кроме того память данных может быть размещена в секции кода,а код программы может запускаться из секции ОЗУ. В системных областях памяти раполагаются контроллер прерываний и компоненты отладки. Эти устройства имеют фиксированные адреса. 23. Имеется контроллер вложенных векторных прерываний. Он тесто связан с ядром процессора и выполняет следующие функции: 1.Поддержка вложенных прерываний 2. поддержка векторных прерываний 3. поддержка динамического изменения приоритетов 4. уменьшение задержки обработки прерывания 5.маскировка прерываний. Контроллер NVIC обеспечивает поддержку вложенных прерываний. Всем внешним прерываниями и большинству системных исключений могут быть назначены различные уровни приоритета. При возникновении прерывания контроллер сранивает его приоритет с приоритетом прерывания, обрабатываемого в данный момент. Если новое прерывание имеет более высокий приоритет, то обработка текущего прерывания приостанавливается и запускается обработчик нового прерывания. Поддержка векторных прерываний. В процессоре Cortex-M3 реализована поддержка векторных прерываний. В случае возникновения разрешенного прерывания стартовый адрес соответствующей процедуры обработки прерывания берется из таблицы векторов, расположенной в памяти. Причем,определение стартового адреса ISR и переход на него осуществляется полностью аппаратно,что ускоряет обслуживание запроса прерывания. 24. Набор инструкций микропроцессора . Классификация. Примеры 1) Команды передачи данных: а) между регистрами и памятью (включая стек), обмен содержимым источника и приемника; б) ввода, вывода, табличного преобразования; в) загрузка исполнительного адреса в РОНы г) передача содержимого регистра F флагов в память, в стек и из стека. 2) Арифметические команды: «+» ADD <Ячейка1/Регистр1>, <Ячейка2/ Регистр2> «-» SUB <Ячейка1/Регистр1>, <Ячейка2/ Регистр2> «×» MUL <операнд> «/» Для беззнаковых чисел применяют: DIV <операнд> Для знаковых чисел используют команду: IDIV <операнд> двоичных чисел со знаком и без знаков (произведение и делимое представляются числами двойной длины), 3) Логические команды и сдвиги: сдвиги на 1 или заданное число разрядов (константа сдвига располагается в CL). AND Логическое И. OR Логическое ИЛИ. XOR Логическое исключающее ИЛИ. 4) Команды передачи управления: переходы, вызовы, возвраты - имеют две разновидности - внутрисегментные ("близкие") и межсегментные ("дальние"). При близких передачах загружается только IP, при дальних - IP и CS. Передачи управления могут быть прямыми (целевой адрес - в команде) или косвенными (целевой адрес вычисляется с использованием стандартных режимов адресации) 25. Следующие типы пересылок: 1. пересылка данных между регистрами общего назначения 2. пересылка данных между памятью и регистром общего назначения 3.пересылка данных между регистром специального назначения и регистром общего назначения 4. пересылка непосредственного значения в регистр общего назначения 5. пересылка непосредственного значения в регистр общего назначения Для пересылки между регистрами предназачена команда MOV. Пересылка из регистра R3 в регистр R8 (MOV R8,R3) Команда MNV-пересылает инверсное значение исходного содержимого регистра LDR-команда загрузки пересылает данные из памяти в регистры процессора STR-команда сохранения, пересылает содержимое регистров в память. (поддерживается пересылка байт,слова,двойное слово) Операция загрузки данных в стек (PUSH)и операция извлечения данных из стека(POP). PUSH {R0,R4-R7,R9};загружаем R0,R4,R6,R7,R9 в стек POP {R2,R3}; извлекаем R2 и R3 из стека  Пример: Пусть R8 содержит значение 0x8000,тогда: STMIA.W R8! ,{R0-R3} ; После сохранения данных R8станет равным 0x8010 STMIA.W R8 , {R0-R3} ;R8 не изменится Групповая загрузка/сохранения LDMIA Rd!, LDR.W R0,[R1,#offset]! ; читаем из памяти по адресу [R1+offset], ; после операции R1становится равным R1+offset Для обращения к регистрам специального назначения команды MSR и MRS. Для загрузки значений команда MOVS. 26. Арифметические операции: «+» ADD <Ячейка1/Регистр1>, <Ячейка2/ Регистр2> «-» SUB <Ячейка1/Регистр1>, <Ячейка2/ Регистр2> «×» MUL <операнд> «/» Для беззнаковых чисел применяют: DIV <операнд> Для знаковых чисел используют команду: IDIV <операнд> Пример: ADD Rd,Rs ADD R1,R5 (сложить 2 регистра) ADD Rd,Rs1,Rs2 (склад-ся 2 регистра и помещается в 3) ADD Rd,Rs,#число 27. Операции сдвига переносят значения битов содержимого регистра влево или вправо на заданное количество позиций- длина сдвига. Сдвиг может выполняться: 1. Непосредственно с помощью инструкций ,при этом результат сдвига заносится в регистр-получатель. 2. во время вычисления значения второго операнда Operand2 команд, при этом результат сдвига используется как один из операндов инструкции.

ASR R7,R8,#9 Арифмитический сдвиг вправо на 9 бит LSLS R1,R2,#3 Логический сдвиг влево на 3 бита с установкой флагов LSR R4,R5,#6 Логический сдвиг вправо на 6 бит ROR R4,R5,R6 Циклический сдвиг вправо на количество бит,указанное в младшем байте регистра R6 RRX R4,R5 Циклический сдвиг вправо через бит переноса |