Преобразователь кодов. Курсовик Гридчин-1. Предприятия 22

Скачать 0.51 Mb. Скачать 0.51 Mb.

|

|

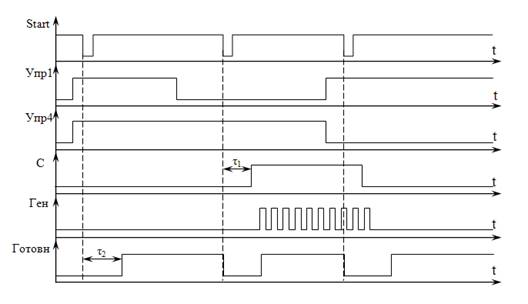

2 Конструкторско-технологическая часть 2.1 Структурная схема По заданию необходимо построить структурную схему преобразователя кодов. Преобразователи кодов изменяют вид кодирования данных. Выходные и входные устройства оперируют с десятичными кодами, вычисления ведутся в двоичных кодах, промежуточной формой представления чисел служит двоично-десятичный код. К преобразователям кодов можно отнести дешифраторы и шифраторы, однако эти устройства выделяют в отдельные классы. Структурная схема преобразователя кода представлена на рисунке 6.  Рисунок 6 - Структурная схема преобразователя кода. Шифратор преобразует одиночный сигнал в n-разрядный двоичный код. Наибольшее применение он находит в устройствах ввода информации для преобразования десятичных чисел двоичную систему счисления. Как видно из таблиц переключений, нужен преобразователь с десятью входами и четырьмя выходами. Исходя из задания, схема должна включать в себя блоки запоминания и дешифрования управляющего кода, блок обработки результата дешифрирования, тактовый генератор. На двоичных выходах счетчика последовательно формируются двоичные комбинации выходного кода для их дальнейшего преобразования. В схеме предусмотрен режим установки в начальное состояние. Для этого на R-вход счетчика подается сигнал сброса со схемы управления. Схема преобразования входного двоичного кода в выходной синтезируется в базисе ИЛИ-НЕ. На ее вход последовательно подаются двоичные комбинации входного кода с выходов счетчика. На выходах получаются двоичные комбинации выходного кода. В схеме управления формируются два управляющих сигнала: «Пуск», «Сброс» от механических переключателей. В схеме управления для подавления дребезга используются триггеры. Схема индикации выходного двоичного кода позволяет наблюдать выходной двоичный код. Индикация осуществляется с помощью светодиодов, число которых равно разрядности выходного кода. Блок запоминания необходим для хранения управляющего числа до прихода нового стартового импульса. Кроме этого данный блок служит своеобразным синхронизатором – по каждому стартовому импульсу в него будет заноситься новое управляющее число, которое передается по 4-х разрядной шине данных. Блок запоминания реализован на 4-х разрядном параллельном регистре. Блок дешифрирования управляющего кода является основным функциональным звеном схемы, позволяя распознать управляющий код. Этот блок реализован на дешифраторе 4х16, так как разрядность управляющего числа – 4. По инвертированному стартовому сигналу, поступающему на входы стробирования дешифратора, на всех его выходах формируется уровень логической единицы. Блок обработки результатов дешифрования формирует сигнал управления в соответствии с заданным алгоритмом. То есть по всем четным числам ≥ 8 посылается сигнал разрешения запуска генератора с частотой Fтакт = 100 МГц. Блок обработки результата дешифрирования управляющего кода реализован на логическом элементе И-НЕ. Быстродействие памяти не слишком критично, так как перебор адресов происходит довольно медленно. За период тактового сигнала (1 мкс) в режиме чтения должен успеть сработать регистр накапливающего сумматора, и память должна успеть выдать читаемый код с задержкой выборки адреса. Совмещенная шина входных или выходных данных памяти требует применения однонаправленного входного буфера, через который в режиме записи на память будут подаваться записываемые в память коды выборок генерируемого сигнала. Блок формирования сигнала готовности к приему нового управляющего кода содержит линию задержки и D-триггер. По стартовому сигналу, поступающему на вход R триггера, на выходе формируется сигнал низкого уровня – неготовность к приему нового управляющего числа. К информационному входу триггера приложено напряжение высокого уровня, а на вход C поступает сигнал с блока обработки результатов дешифрования, по переднему фронту которого на выходе триггера формируется сигнал высокого уровня, что означает готовность к приему нового управляющего числа. Это происходит одновременно с запуском генератора. Если управляющее число нечетное или < 8, то на вход C триггера тактовый сигнал не поступает, и на его выходе сигнал низкого уровня (неготовность к приему). Для этого случая необходима линия задержки, служащая для смещения стартового сигнала во времени, который затем поступает на вход S триггера. Линия задержки должна обеспечивать задержку формирования сигнала готовности, достаточную для появления сигнала на входе управления генератора, по стартовому сигналу. Следует также отметить, что стартовый импульс должен быть сигналом низкого уровня и должен поступать только при сформированном сигнале готовности схемы к приему нового управляющего числа. Необходимо обеспечить, чтобы длительность этого импульса составляла 10-15 нс. Так как согласно алгоритму управления тактовый генератор запускается по всем четным числам ≥ 8, то на его работу влияют только 0-й и 3-й разряды 4-х разрядного управляющего числа. Потому что если 0-й разряд равен 1, то управляющее число нечетное, а если 3-й разряд равен 0, то управляющее число < 8. В схеме разряды управляющего числа соответствуют сигналам: - 0-й разряд – Упр1; - 1-й разряд – Упр2; - 2-й разряд – Упр3; - 3-й разряд – Упр4. Таким образом, когда Упр1=0 и Упр4=1 при любых сигналах Упр2 и Упр3 запускается генератор. Временные диаграммы построены для сигналов: - start – стартовый сигнал; - упр1 – 0-й разряд управляющего числа; - упр4 – 3-й разряд управляющего числа; - с – сигнал с выхода блока обработки результатов дешифрования; - ген – сигнал с выхода генератора; - готовн – сигнал готовности к приему нового управляющего числа. τ1 – задержка формирования сигнала на выходе блока обработки результатов дешифрования. τ2 – задержка формирования сигнала готовности к приему нового управляющего числа, сформированная линией задержки. Диаграмма работы схемы управления на дешифраторе представлена на рисунке 7.  Рисунок 7. Диаграмма работы схемы управления на дешифраторе. 2.2 Синтез схемы формирования входного двоичного кода и схемы преобразователя кодов Схема формирования входного двоичного кода представляет собой счетчик. Счетчик синтезируется на триггерах. Исходные данные для синтеза: - входной двоичный код: код Грея; - серия микросхем: 561; - базис: ИЛИ-НЕ. Последовательность синтеза: Выбираем в заданной серии микросхем JK-триггер, - К561ТВ1. Приведем таблицу переходов JK-триггера. Таблица переходов JK-триггера представлена в таблице 2. Таблица 2 - Таблица переходов JK-триггера.

Строим карты Карно для J1, K1, J2, K2, J3, K3, J4, K4 По картам Карно записываем логические выражения в форме МКНФ для J1, K1, J2, K2, J3, K3, J4, K4. Переводим логические выражения в базис ИЛИ-НЕ, используя тождество двойного отрицания и формулы де Моргана. Схема формирования входного двоичного кода строится на основе счетчика. На двоичных выходах счетчика последовательно формируются двоичные комбинации выходного кода для их дальнейшего преобразования. Логические выражения в форме МКНФ для определяется по формуле  При подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное, то есть выполняется операция инверсии, чем он отличается от RS-триггеров с доопределённым состоянием, которые строго переходят в логический ноль или единицу, независимо от предыдущего состояния. Вход J аналогичен входу S у RS-триггера. Вход K аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. По полученным логическим выражениям выбираем в серии К561 следующие микросхемы: К561ЛЕ10, К561ЛЕ5, К561ЛЕ6. Схема преобразователя кода строится на логических элементах в базисе заданном по варианту (ИЛИ-НЕ). Исходные данные для синтеза: - входной двоичный код: код Грея; - выходной двоичный код: «8421»; - серия микросхем: 561; - базис: ИЛИ-НЕ. Таблица состояний преобразователя представлена в таблице 3. Таблица 3 - Таблица состояний преобразователя.

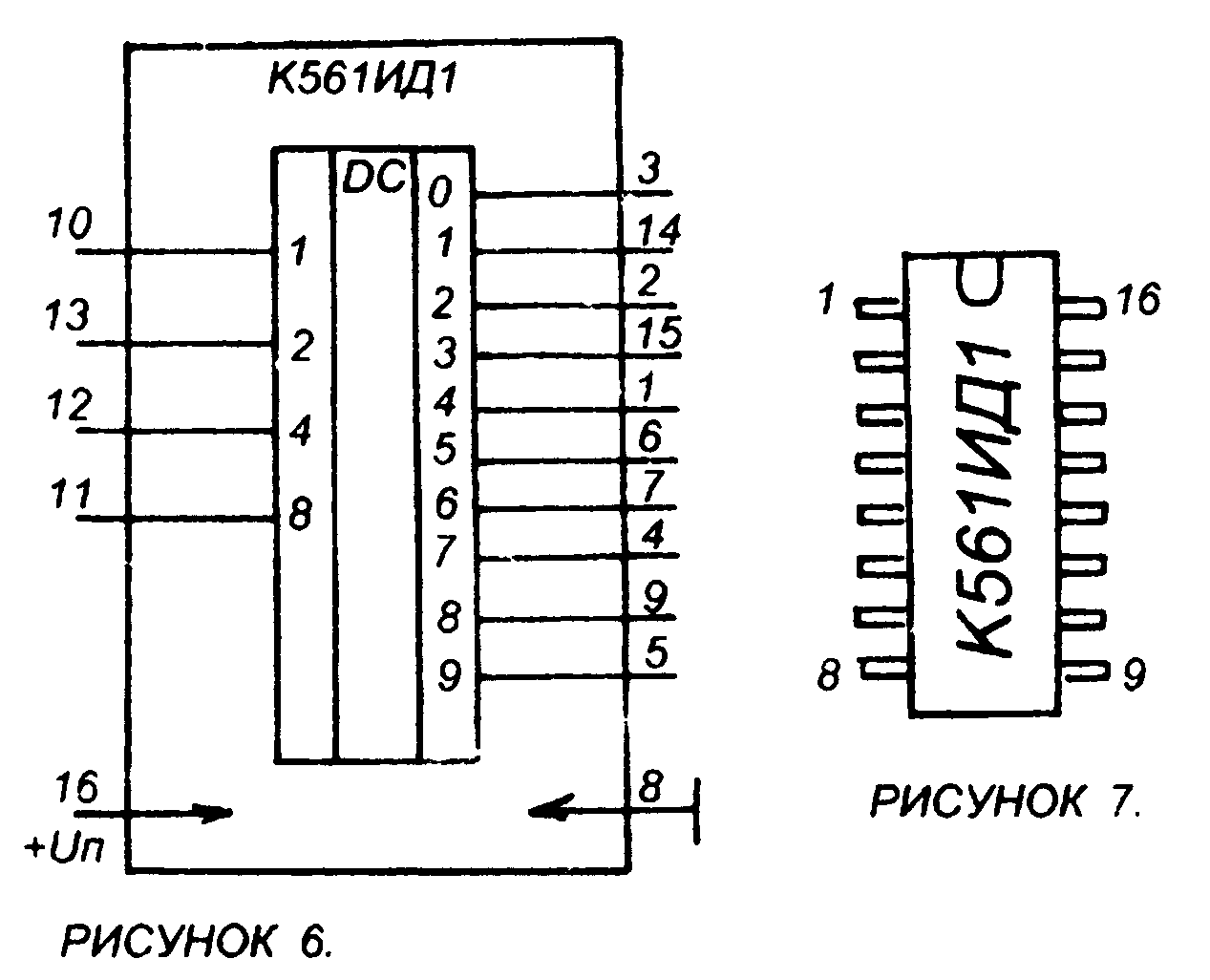

2.3 Выбор схемы управления и схемы индикации десятичного эквивалента преобразуемого кода Схема управления предназначена для формирования двух управляющих сигналов “Пуск" и “Сброс”. Для этой цепи используем механический переключатель. При однократной установке ключа S1 в положение I формируется сигнал “Сброс”, который подается на R-выходы триггеров в отдельных блоках устройства и устанавливает триггеры в начальное состояние. При однократной установке ключа S1 в положение II на С - входы поступает одиночный сигнал и формируется первое значение входного кода, которое затем преобразуется в выходной код. Как известно, непосредственная передача сигнала от механических контактов на входы интегральных микросхем допустима не всегда из-за так называемого дребезга - многократного неконтролируемого замыкания и размыкания контактов в момент их переключения. На входы установки и сброса триггеров непосредственная подача сигналов допустима, а на счетные входы счетчиков - нет. При возврате ключа S1 в исходное положение на один из входов элемента DD1.1 подается активный уровень, на выходе элемента устанавливается уровень лог. 0, а на выходе элемента DD1.2 уровень лог. 1, таким образом, формируется отрицательный перепад, который не воспринимается прямыми входами триггеров. При вторичном нажатии кнопки S1 процесс повторяется и формируется следующее значение выходного кода. Выберем следующие микросхемы: К561ИД1 - в качестве дешифратора. Эта микросхема представляет собой универсальный дешифратор, позволяющий преобразовать четырехразрядный двоично-десятичный код в десятичный. Микросхема позволяет непосредственно подключать к своим выходам светодиоды. Все входы и выходы микросхемы - прямые. Схема дешифратора К561ИД1 представлена на рисунке 8.  Рисунок 8. Схема дешифратора К561ИД1. На входы установки и сброса триггеров непосредственная подача сигналов допустима, а на счетные входы счетчиков – нет. В качестве элемента подавляющего «дребезг» используется триггер. Схема индикации предназначена для контроля, двоичный эквивалент какого десятичного числа преобразуется в данный момент. Как известно непосредственная передача сигналов от механических контактов к входам интегральных микросхем допустима не всегда, из-за наличия так называемого «дребезга контактов» - многократного неконтролируемого замыкания и размыкания контактов в момент их переключения. В данном случае для схемы индикации понадобится только дешифратор, т.к. выходной код 8421 является наиболее распространенным и дешифруется большинством промышленных дешифраторов. Исходные данные для анализа – это десятичное число 6. Проставим двоичный эквивалент в разработанной принципиальной электрической схеме на все входы узла преобразователя входного кода в выходной и выполним подробный анализ работы этого узла. Отсчет входов элементов ведется сверху вниз по принципиальной схеме. Входы элемента DD9.1 - 0, 1, 0, 0; выход - 0. Входы элемента DD3.3 - 1, 1, 1; выход - 0. Входы элемента DD10.1 - 0, 0, 1; выход - 0. Входы элемента DD10.2 - 1, 0, 1; выход - 0. Входы элемента DD7.2 - 1, 1; выход - 0. Входы элемента DD7.3 - 0, 0; выход - 1. Входы элемента DD10.3 - 1, 0, 0; выход - 0. Сигнал Y2 равен 0. Входы элемента DD7.4 - 1, 1; выход - 0. Входы элемента DD11.1 - 0, 0; выход - 1. Сигнал Y3 равен 1. Входы элемента DD9.2 - 0, 0, 0, 0; выход - 1. Входы элемента DD5.5 - 1; выход - 0. Входы элемента DD11.4 - 0, 0; выход - 1. Сигнал Y1 равен 1. Сигнал Y4 равен 0. Вывод: при входном сигнале 0111 на узле преобразователя кода с прямыми входами и выходами, выходной сигнал равен 0101, что соответствует таблице функционирования устройства (таблица 3) - устройство работает правильно. Из этого можно сделать вывод, что микросхема К561ИД1 отлично подходит для преобразования входного четырехразрядного двоично-десятичного кода в десятичный или четырехразрядного двоичного в октальный. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||