Образец. 33425_Образец_оформления. Содержание 3 Алгоритмы планирования 12

Скачать 1.18 Mb. Скачать 1.18 Mb.

|

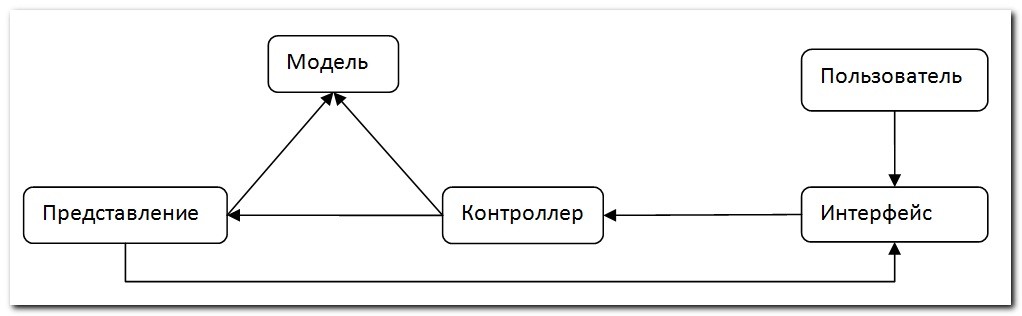

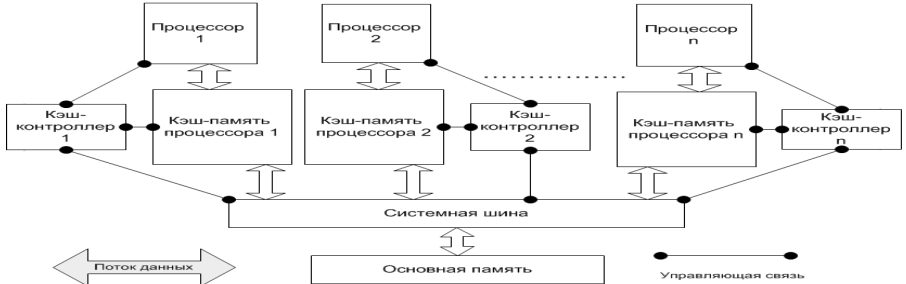

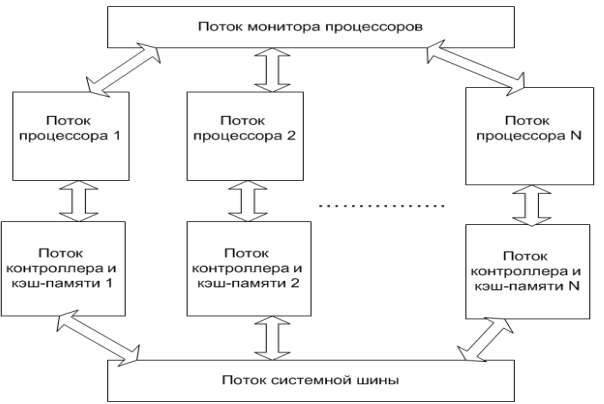

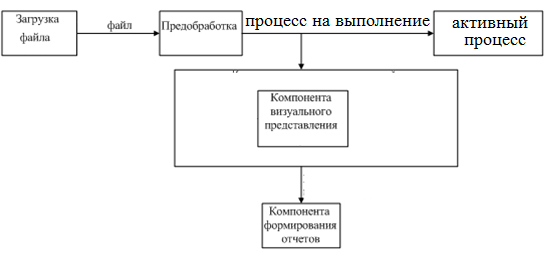

3.2 Моделирование модулей и их описаниеВ качестве объекта исследования рассмотрим мультипроцессор с общей (разделяемой) памятью на основе общей системной шины. Обобщенная структура моделируемой системы представлена на рис. 26. Кэш–память каждого отдельного процессора в общем случае является многоуровневой [17, с. 82]. Зависимость между организацией кэш–памяти мультипроцессора и производительностью всей системы целесообразно представить в виде некоторой функции G = F(Y1, Y2), где Y1 и Y2 – векторы входных параметров модели, G – вектор выходных параметров (показателей эффективности системы). Параметры моделирования целесообразно разделить на два вектора, поскольку часть из них представляют собой характеристики аппаратуры (и являются постоянными, независимо от задачи, выполняемой системой), а часть – показателями, зависящими от решаемой задачи (то есть какими–либо характеристиками программы, выполняемой мультипроцессором в конкретный момент времени). Структура мультипроцессора с общей памятью представлена на рисунке 26.  Рисунок 26 – Структура мультипроцессора с общей памятью В имитационной модели присутствуют 4 типа объектов, которые взаимодействуют между собой: процессоры, кэш–контроллеры, кэш–память и системная шина (рисунок 27). Каждый процессор имеет собственную кэш–память и кэш–контроллер. Единственная системная шина служит связующим звеном между кэшами процессоров.  Рисунок 27 – Структура имитационной модели мультипроцессора Каждый процессор в модели представляет собой генератор операций. Операции процессора, не связанные с обращением к памяти, выполняются в течение одного такта дискретного времени и фактически не моделируются (для таких операций имеет значение только время загрузки процессора, а не характер операции). Время выполнения такой операции принимается за единицу дискретного времени, длительность любой другой (связанной с обращением к памяти) операции занимает время в несколько тактов. Кэш–контроллер обрабатывает запросы процессора к памяти и реализует часть логики моделирования протоколов когерентности. В случае промаха или операции записи в кэш, которая потенциально может привести к несоответствию данных в различных кэшах, контроллер выставляет соответствующий запрос на системную шину. В случае операции, которая не может привести к нарушению когерентности, контроллер прибавляет к счетчику холостых тактов вызывающего процессора время обработки запроса, после чего операция считается выполненной и процессор продолжает работу. Системная шина последовательно обрабатывает запросы из очереди, реализуя логику моделируемого протокола когерентности. Программная реализация системы предполагает параллельное моделирование каждого объекта в отдельном потоке команд (рисунок 28).  Рисунок 28 – Структура программной реализации имитационной модели мультипроцессора с общей памятью 3.3 Формат входных и выходных данныхDesktop–приложение а также интерфейс спроектированы на основе паттерна Модель–Представление–Контроллер, или по–английски Model–View–Controller (рис. 29). Для реализации был выбран язык программирования С# в силу того, что есть возможность использования написанных классов для переноса приложения на любой интерфейс.

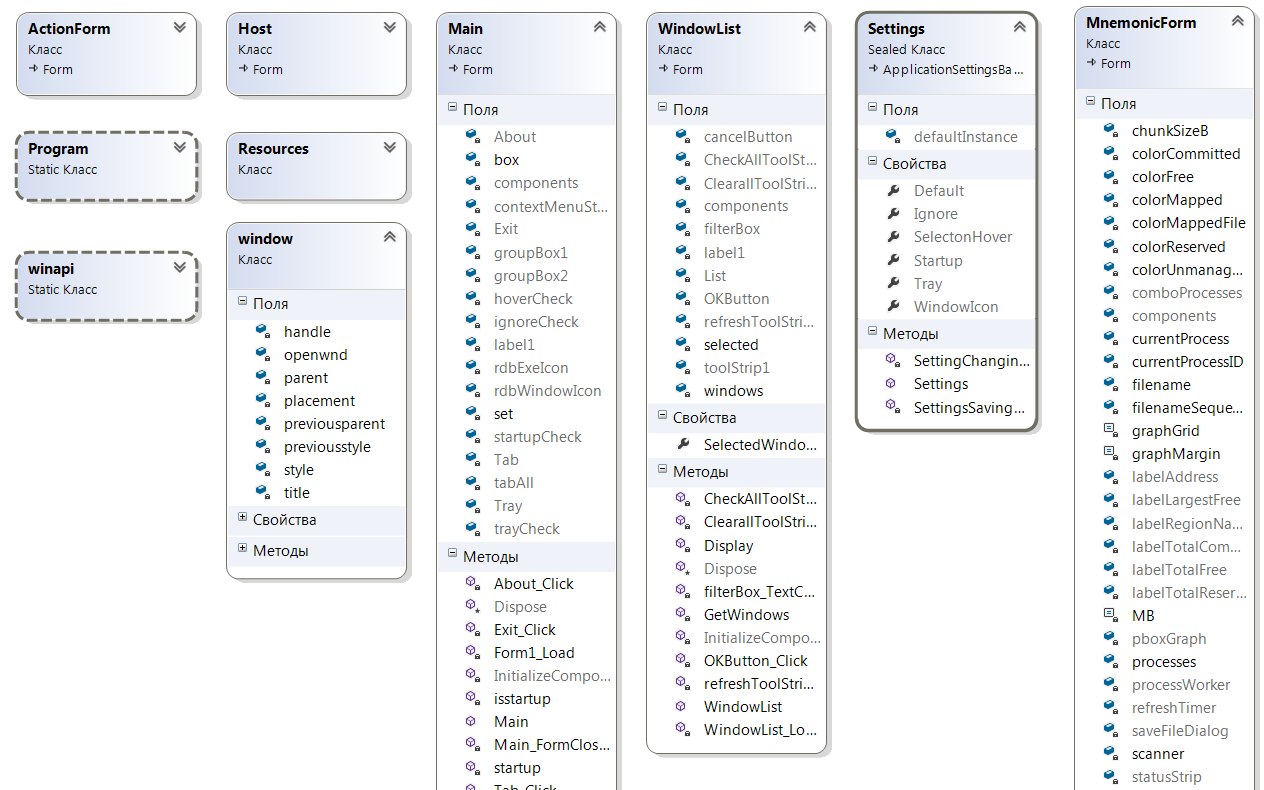

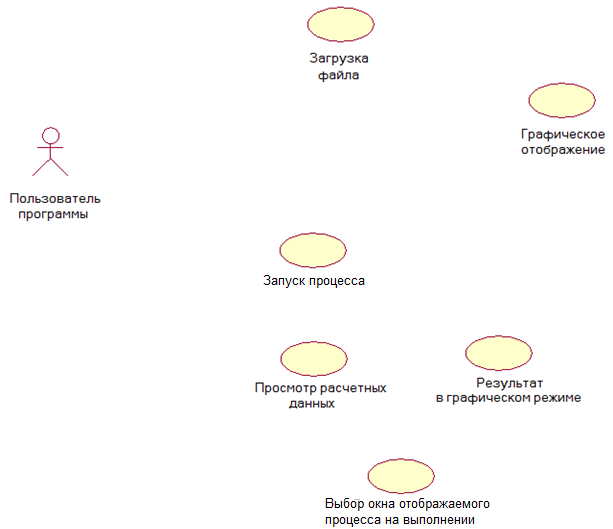

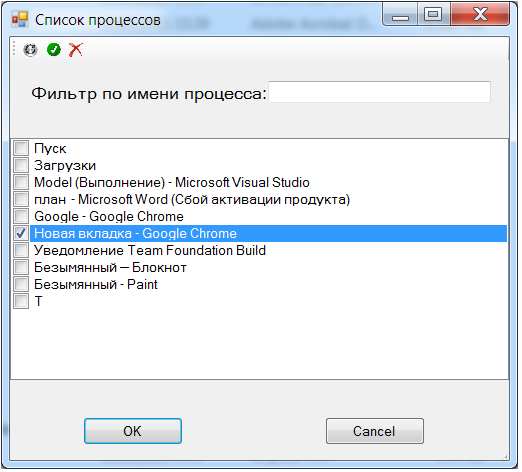

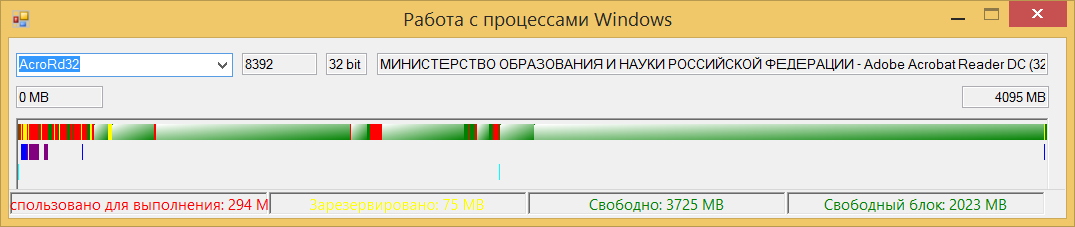

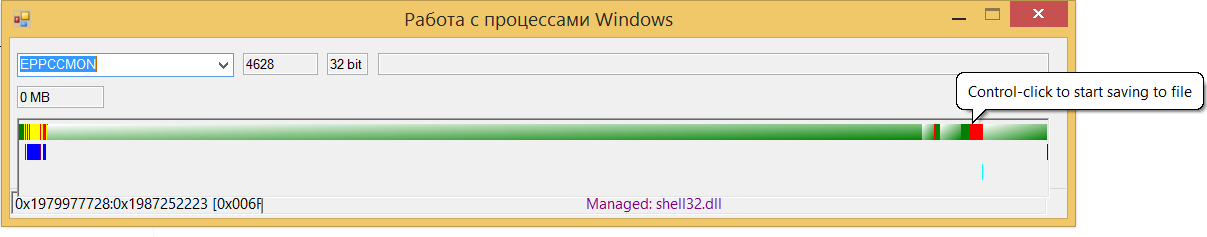

Рисунок 29 – Desktop–приложение и интерфейс спроектированы на основе паттерна Модель–Представление–Контроллер или по–английски Model–View–Controller В ходе решения поставленной задачи, были разработаны несколько классов решения задачи на C#. TList * SList – список сегментов. int Size – размер оперативной памяти. int iSeg – индекс сегмента. int accAdr – адрес доступа. Методы: void AddSeg(Segment *pSeg)– добавить сегмент; void SetSize(int val)– установить размер оперативной памяти; int GetSize()– получить размер оперативной памяти; void Access(int iS, int adr)– функция доступа к сегменту; class Process – представляет собой класс процесса; CRangeCoder – класс, реализующий арифметическое кодирование целых чисел. 3.4 Модульная структура программного средстваСтруктура программной системы моделирования структуризации адресного пространства состоит из следующих основных программных модулей: Форма Main.cs – модуль, содержащий средства выполнения загрузки процессов и потоков в оперативную память, с возможностью проведения масштабирования и отображения оболочки управления приложением. Форма MnemoticForm.cs – программная форма для визуализации занимаемого сегмента памяти для выбранного процесса, с отображением статистических сведений. На форме представлены основные элементы управления приложением, окно отображения содержимого файла–процесса, окна статистических сведений, кнопки активации действий.. Содержимое классов модуля структуризации оперативной памяти приведено на рис. 30.  Рисунок 30 – Диаграмма классов модуля моделирования Концептуальная схема представляет собой обобщенные функциональные и информационные компоненты проектируемого программного продукта, принципы их взаимодействия между собой, с пользователем и внешней средой. По результатам вышеописанной работы была спроектирована концептуальная схема системы постановки процессов на выполнение и структуризации оперативной памяти, которая показана на рис. 31, где показаны две концептуальные части – компонента обработки данных, поступивших в систему и компонента анализа идентифицированных характеристик.  Рисунок 31 – Концептуальная схема разрабатываемой программной системы Приложение представляет собой программное средство для обработки запросов одного пользователя, поэтому основным элементов диаграммы прецендентов является только он. Остальные возможные режимы работы представлены на рис. 32.         Рисунок 32 – IDEF0–схема системы моделирования памяти 3.5 Описание интерфейса программного продуктаРабота с программой начинается после запуска файла model.exe на выполнение. На экране появляется главная форма управления приложением (рис. 33)  Рисунок 33 – Главное окно программы после запуска Первым этапом является открытие файла с процессом и указание параметров отображения. Эти настройки выполняются после нажатия кнопки «ОК». Для каждого процесса предусмотрено вывод информации о занимаемой памяти и сегментами адресации. Внешний вид окон представлен на рис. 34–35.  Рисунок 34 – Выбор процесса  Рисунок 35 – Результат исследования распределения памяти После выбора отображения процесса, исполняемый поток открывается в главном окне, в котором выполняется его исполнительный код с использованием выделенного адресного пространства. Результат отображения указанного процесса представлено на рис. 36:  Рисунок 36 – Вывод процессов на экран ЗАКЛЮЧЕНИЕВ данном курсовом проекте было разработано программный способ управления и отображения процессов операционной системы. Созданное программное обеспечение является исследовательским, оно направлено на изучение и анализ методов структуризации адресного пространства. С его помощью могут быть получены экспериментальные данные, используемые в процессах распределения оперативной памяти. Конечным программным продуктом может являться оболочка, представляющая в значительной мере автоматизированный интерфейс для проведения преобразования таблицы виртуальных адресов, таблицы привилегий процессов и механизма выделения ресурсов оперативной памяти. В процессе выполнения работы были использованы следующие алгоритмы: моделирования работы подсистемы адресного пространства; отображение статистических параметров используемой оперативной памяти для загруженных процессов; операции масштабирования процессов и потоков в оперативной памяти. Моделирование работы системы памяти мультипроцессора сводится к нескольким действиям: это поиск блоков в справочнике кэш–памяти, изменения тегов и состояний в соответствующих справочниках и наращивании счетчиков полезных и холостых тактов. Выполнение каждой операции системой памяти приводит к соответствующему увеличению счетчика холостых тактов процессора (даже если это операция физически не осуществляется, например, обращение к основной памяти). СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВАвдеев Н. А. Реализация VHDL–функций пакета NUMERIC_STD логическими схемами // Информационные технологии. — 2016. — № 1. — С. 9–18. Авдеев Н.А. Пакет NUMERIC_STD языка VHDL // Информационные технологии. — 2015. — № 9. – С. 154–160. Армстронг Дж. Р. Моделирование цифровых систем на языке VHDL. — М.: Мир, 2015. — 175 с. Бабак В.П. VHDL: Справочное пособие по основам языка. – М.: Додэка–XXI, 2015. – 224 с. Бибило П.Н. Логическое перепроектирование схем, реализованных на FPGA, в схемы на базовых матричных кристаллах //Информационные технологии. – 2014. — №1. – С.10–17. Бибило П.Н. Основы языка VHDL. Второе издание. — М.: Солон–Р, 2015. – 224 с. Бибило П.Н. Проектирование конечных автоматов в САПР WebPack ISE фирмы Xilinx // Информационные технологии. – 2014. — №3. – С. 8–13. Бибило П.Н. Синтез логических схем с использованием языка VHDL. — М.: Солон–Р, 2015. — 384 с. Бибило П.Н. Системы проектирования интегральных схем на основе языка VHDL. StateCAD, ModelSim, LeonardoSpectrum. — М.: СОЛОН–Пресс, 2015. — 384 с. Бибило П.Н. VHDL. Эффективное использование при проектировании цифровых систем. – М.: СОЛОН–Пресс, 2016. – 344 с. Будилов В. Интернет–программирование на Java. – СПб.: БХВ–Петербург, 2013. – 128 с. Гарнаев А.Ю. Web–программирование на Java и JavaScript. – СПб.: БХВ–Петербург, 2015. – 193 с. Кораблев В. Самоучитель Visual C++.NET. – СПб.: BHV, 2013. – 528 с. Либерти Д. Программирование на C++. – СПб.: Символ–Плюс, 2014. – 688 с. Майо Дж. C++ Builder. Быстрый старт. – М.: Бином, 2015. – 384 с. Мала С. Вэйвлеты в обработке сигналов. – М.: Мир, 2013. – 671 с. Местецкий Л.М. Математические методы распознавания образов. – М.: Омега, 2015. – 487 с. Микелсен К. Язык программирования C++. Лекции и упражнения. – Киев: ДиаСофт, 2014. – 656 с. Новиков Л.В. Основы вейвлет–анализа сигналов. – СПб.: МОДУС, 2013. – 152 с. Петухов А.П. Введение в теорию базисов всплесков. – СПб.: СПбГТУ, 2015. – 132 с. Петцольд Ч. Программирование для MS Windows на C++. – М.: Русская Редакция, 2013. – 624 с. Петцольд Ч. Программирование для MS Windows на C++. – М.: Русская Редакция, 2016. – 576 с. Таха Х. Введение в исследование операций. – М.: Вильямс, 2015. – 568 с. |