Триггеры1. Триггеры Триггером

Скачать 427.29 Kb. Скачать 427.29 Kb.

|

|

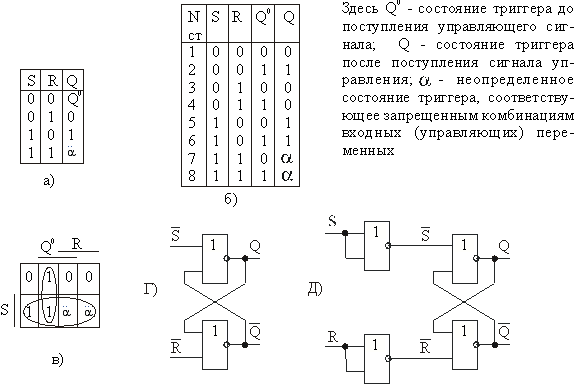

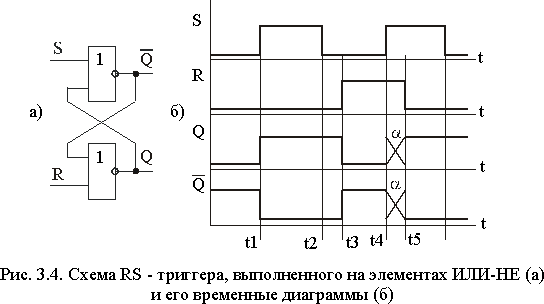

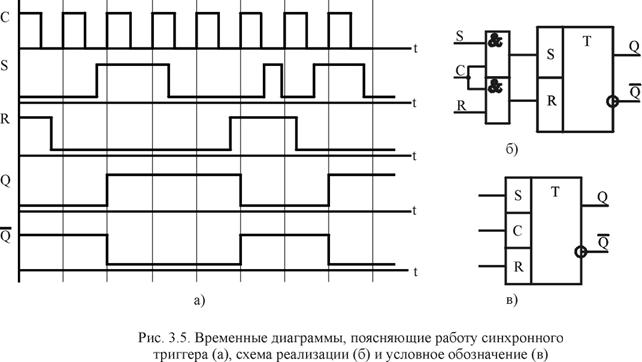

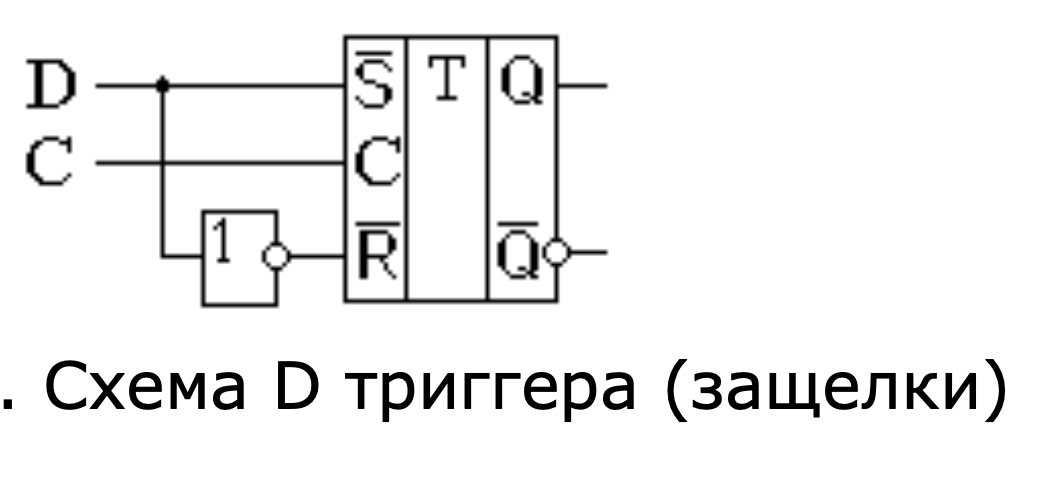

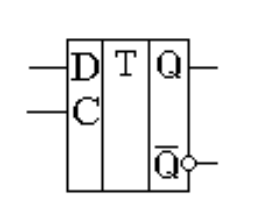

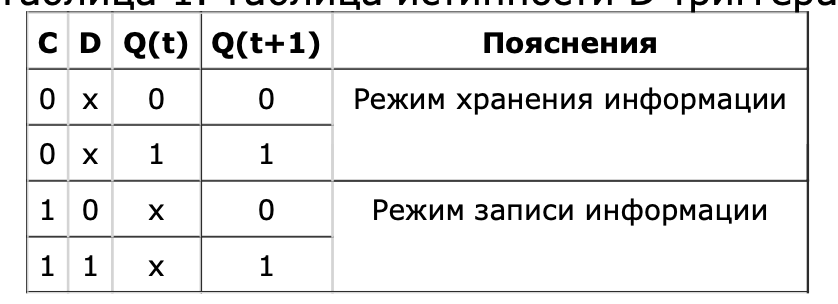

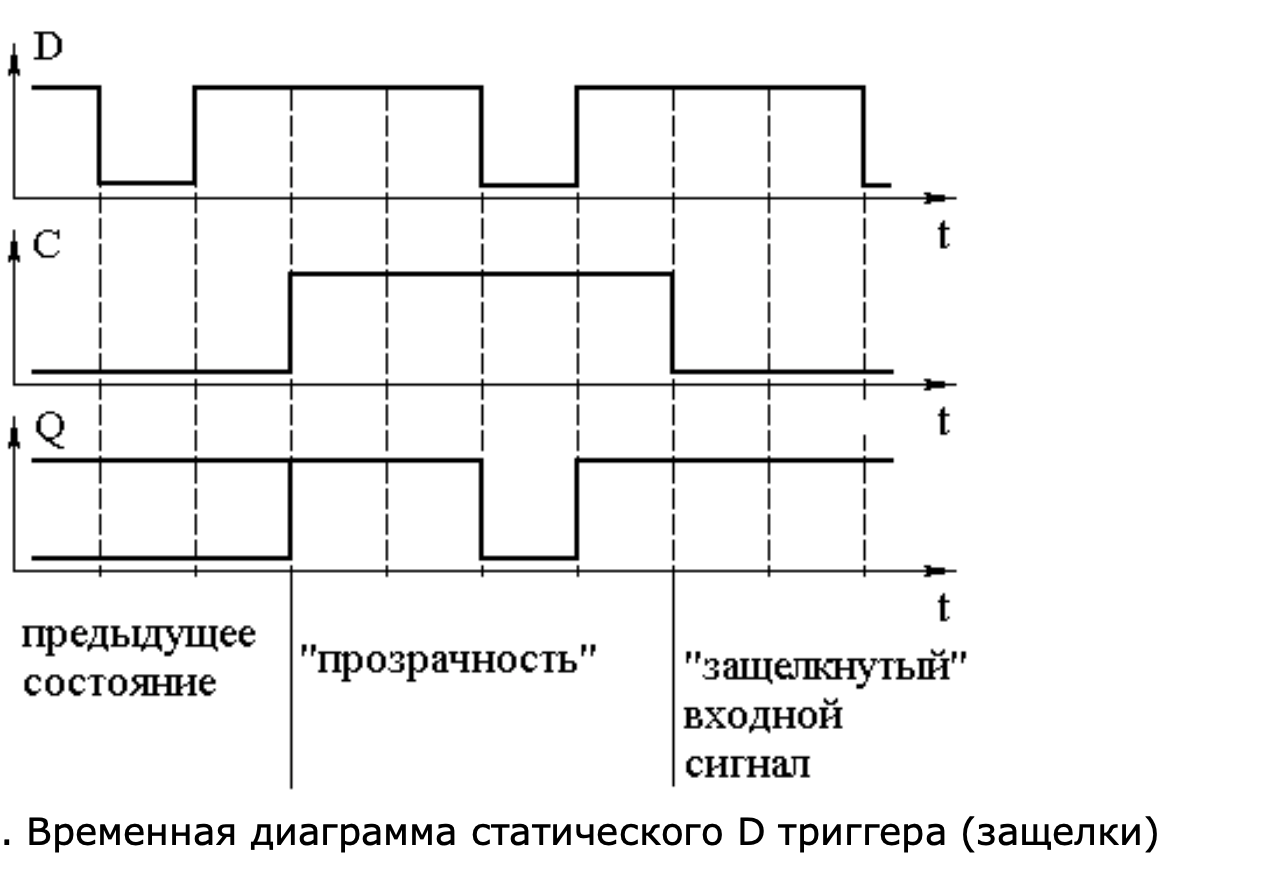

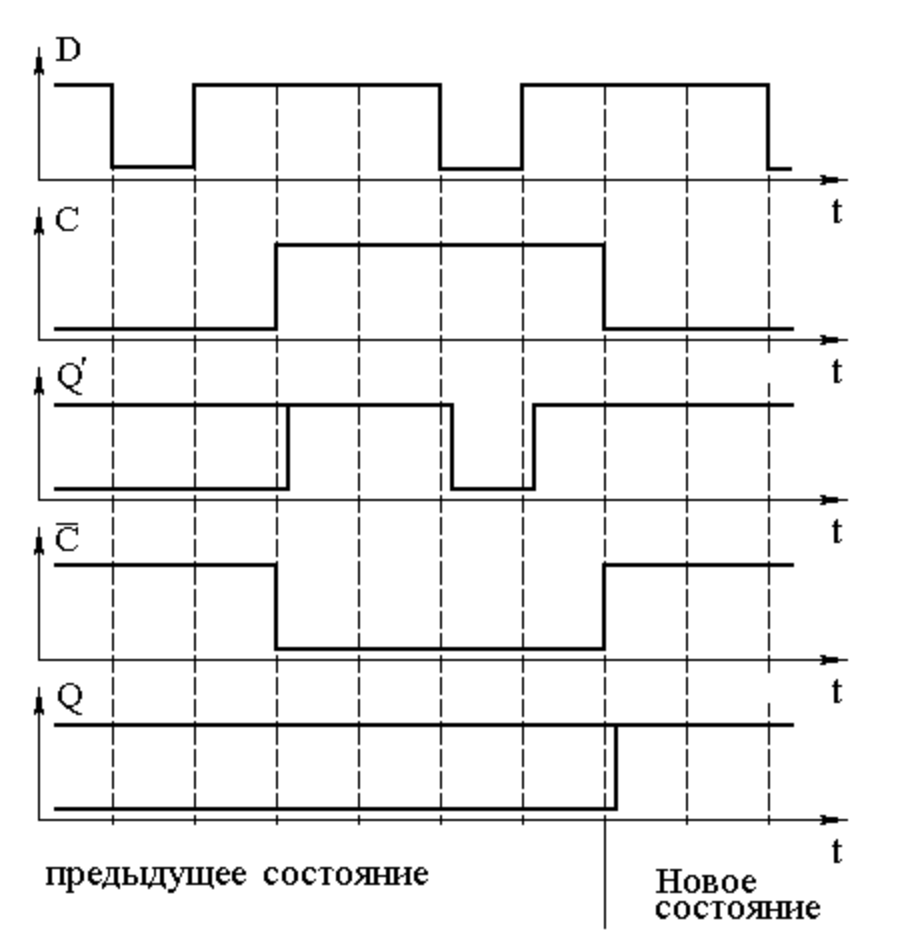

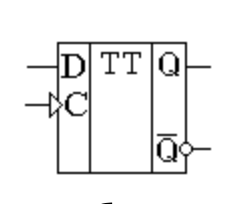

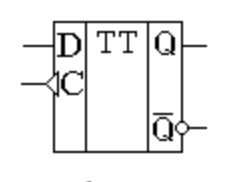

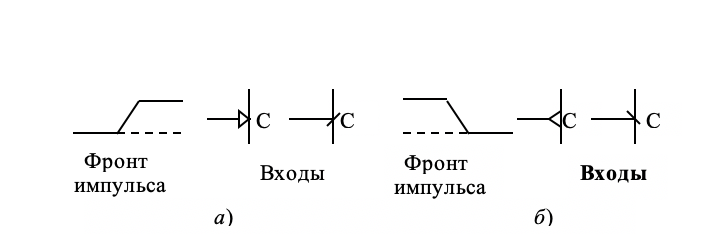

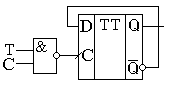

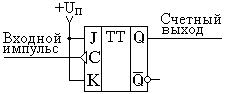

Триггеры Триггером называют устройство, которое может находиться в одном из двух устойчивых состояний, например, включен – «1», выключен – «0» и регенеративно (скачком) переходить из одного состояния в другое. Триггер снабжается двумя выходами: прямым Q и инверсным Q Способность триггера фиксировать на любое время свое текущее состояние наделяет его свойством памяти. Вследствие чего триггер является простейшим последовательностным устройством (в дальнейшем будем именовать устройствами последовательного действия), поскольку его состояние в новом такте определяется не только комбинацией входных сигналов, но и исходным, текущим состоянием. Триггеры являются одним из самых распространенных схемотехнических элементов в цифровой и вычислительной технике и широко применяются в виде самостоятельных изделий и в качестве базовых элементов для построения регистров, счетчиков, запоминающих устройств. Триггеры существенно различаются между собой по схемному исполнению, выполняемым функциям, способам управления, электрическим параметрам. Классификация триггеров Классифицировать триггеры можно по способу приема информации, принципу построения и по функциональным возможностям. По способу приема информации триггеры делятся на асинхронные и синхронные. Асинхронные триггеры воспринимают управляющие, информационные сигналы в момент их поступления на вход триггера и реагируют на них вплоть до момента их снятия. Синхронные триггеры реагируют на установленные информационные сигналы лишь при наличии специального тактирующего сигнала на управляющем входе С (вход синхронизации). Синхронные триггеры со статическим управлением принимают информационные сигналы при подаче на вход С уровня лог.1 (прямой С-вход) или уровня лог. 0 (инверсный С-вход). Триггеры с динамическим управлением воспринимают информационные сигналы в момент перехода тактирующего сигнала на входе С из 0 в 1(0/1) или из 1 в 0 (1/0). По принципу построения триггеры со статическим управлением можно разделить на одноступенчатые и двухступенчатые. Одноступенчатые триггеры имеют в своем составе одну ступень запоминания информации (одну элементарную триггерную ячейку) и схему управления. Двухступенчатые триггеры имеют две последовательно включенные запоминающие ячейки, запись информации вначале производится в первую ячейку (ступень), а затем переписывается во вторую (выходную) ступень. По функциональным возможностям различаются: – триггеры с раздельным управлением по входам R и S (RS-триггеры); – триггеры с приемом информации по входу D (D-триггеры); – триггеры со счетным входом (T-триггеры); – универсальные триггеры с информационными входами J и K (JK-триггеры). Обозначения и назначения входов триггеров: R (от англ. Reset) – раздельный вход установки в состояние 0 (сброс); S (от англ. Set) – раздельный вход установки в состояние 1 (включение); К (от англ. Kill) – внезапное отключение, управление нулем; J (от англ. Jerk) – внезапное включение, управление единицей; Т – счетный вход; D (от англ. Delay – задержка, Data – данные) – информационный вход установки триггера в состояние, соответствующее логическому уровню на этом входе; С (от англ. Clock) – исполнительный, управляющий (синхронизирующий) вход, вход тактовых импульсов; V – разрешающий управляющий вход. Основными техническими характеристиками триггера являются: быстродействие, потребляемая мощность, напряжение питания, помехоустойчивость, уровни входных и выходных сигналов, функциональные возможности. Для обозначения функциональных возможностей триггеров в интегральном исполнении используется следующая маркировка: TR – RS-триггер, TB – JK-триггер, TM – D-триггер. Триггеры относятся к цифровым автоматам. В отличие от комбинационных схем состояние на выходе триггера в данный момент времени определяется не только состояниями на входах триггера в этот же момент времени, но и предыдущим состоянием триггера. Цифровые автоматы, к которым относятся триггеры, иногда называют последовательными схемами. Триггеры строились по самым разнообразным электрическим схемам. В последнее время триггеры обычно конструируют, используя логические элементы. RS - триггер Важным методом, используемым для описания функционирования RS- триггера, является метод таблиц состояний (таблиц переходов). Таблица состояний (рис. 3.3.а) RS-триггера в сокращенной форме (эту таблицу называют также управляющей таблицей, таблицей функционирования) содержит два входных сигнала (сигналы R и S) и один выходной сигнал Q (функция). Хотя триггеры имеют два выхода - один прямой Q, а другой - инверсный `Q, в описании триггера и в таблице состояний указывают лишь состояние прямого выхода Q. Из таблицы состояний триггера видно, что при подаче на вход R уровня лог. «1» триггер принимает состояние логического «0», а при подаче управляющего сигнала «1» на вход S - состояние «1». Следует отметить также, что если до подачи управляющего сигнала, например, на вход R, триггер находился в состоянии логического «0», его состояние не изменится и после подачи сигнала «1» на вход R. Если на обоих входах триггера имеются уровни логического «0»- это состояние соответствует режиму хранения и триггер сохраняет предыдущее состояние. В таблице это состояние обозначено условно Q0. При подаче на входы R и S одновременно уровня «1» триггер будет находиться в неопределенном (или неправильном) состоянии, поэтому такое сочетание сигналов R и S называется запрещенной комбинацией управляющих сигналов и в таблице состояний обозначается буквой a. Сокращенная таблица состояний триггера отражает лишь динамику изменения состояния триггера и не учитывает свойство триггера запоминать единицу информации. Полная таблица состояний триггера должна учитывать влияние (на процесс управления) значения предыдущего состояния триггера Q0. Причем Q0 представляется как входная переменная. Полная таблица состояний RS -триггера приведена на рис. 3.3, б. Таблицу состояний строят так же, как и таблицу истинности. Анализ таблицы показывает, что только в ситуациях, описываемых строками 4 и 5, происходит изменение состояния триггера.  Рис. 3.3. RS - триггер: а) - упрощенная таблица состояний; б) полная таблицапереходов; в) Карта Карно; г) RS - триггер, управляемый сигналом низкого уровня ( Рассмотрим строку 4. После того, как подается сигнал на вход R, триггер сбрасывается, т.е. переходит из состояния “1” в состояние “0”. Рассмотрим строку 5. Триггер устанавливается, т.е. переходит из состояния “0” в состояние “1”, в результате подачи сигнала “1” на вход S. Для строк 1 и 2 сигналы S =01* и R=0, и, следовательно, никаких изменений в состоянии триггера не происходит. Для строки 3 сигнал R=1, и этот сигнал в нормальных условиях должен сбросить триггер, но так как триггер уже “сброшен” и Q = 0, то сигнал R = 1 не изменяет его состояние. Аналогично для строки 6 сигнал S = 1, и этот сигнал в обычных условиях будет устанавливать триггер в “1”, но Q = 1, и, следовательно, состояние триггера останется без изменений до поступления следующего сигнала R. Особенность RS-триггера заключается в том, что при подаче одновременно на входы R и S сигнала, соответствующего логической 1, состояние триггера становится неопределенным: на обоих выходах Q и `Q установится уровень “1”, а после снятия со входов управляющих сигналов, в силу случайных причин, триггер может установиться в состояние “0” либо “1”. Очевидно, что для нормальной работы триггера необходимо исключить указанное сочетание входных сигналов, приводящее к неопределенному состоянию, что можно осуществить, предусмотрев выполнения запрещающего условия R × S=0. Из таблицы состояний может быть получено уравнение, описывающее поведение триггера. Это уравнение носит название характеристического уравнения триггера. Оно показывает, как меняется состояние триггера в зависимости от текущих значений состояния и входов. Для получения упрощенного аналитического выражения, описывающего поведение RS-триггера, построим карту Карно и проведем соответствующие контуры (рис. 3.3, в). Полученное характеристическое уравнение триггера имеет вид Применив закон де Моргана преобразуем полученные выражение в базис И-НЕ: Схема RS- триггера, реализованного в выбранном базисе, приведена на рис. 3.3, г. Из формулы RS - триггера видно, что при реализации его в базисе И-НЕ, триггер управляется сигналами низкого уровня, т.е. уровня лог. "0" (если не предусмотрены инверторы). Для приведения поведения триггера, выполненного на элементах И-HE, в соответствие с таблицей состояний сигналы S и R необходимо инвертировать. Из анализа схемы рис. 3.3, г очевидно, что простой RS триггер можно сконструировать, соединив “крест-накрест” два элемента И-НЕ. Входные линии триггера обозначены как Схема RS-триггера, реализовнная в базисе И-HЕ в соответствии с таблицей состояний, приведена на рис. 3.3, д. Для построения RS -триггера на элементах ИЛИ-НЕ приведем формулу триггера в базис ИЛИ-НЕ Схема RS -триггера, выполненная на элементах базиса ИЛИ-HЕ, приведена на рис. 3.4, а. Временные диаграммы, поясняющие работу RS-триггера, приведены на рис. 3.4, б. Из временных диаграмм (рис. 3.4, б) следует, что рассмотренные выше RS-триггеры опрокидываются, т.е. управляются сигналами R и S, в любой момент времени. В тех случаях, когда длительности управляющих сигналов не синхронизированы (не согласованы), триггер может находиться в неопределенном состоянии (интервалы времени t4, t5), и поэтому такие триггеры называют асинхронными.  Триггер, построенный на базе элементов ИЛИ-НЕ, называют также дизьюнктивной бистабильной ячейкой. Бистабильные ячейки, помимо самостоятельного применения, входят в качестве составного узла в триггеры других типов. Синхронный RS -триггер. Синхронные триггеры снабжаются дополнительным входом, по которому поступает синхронизирующий (тактирующий) сигнал. При этом изменение состояния триггера происходит (при наличии управляющего сигнала) только в те моменты времени, когда на специальный синхровход триггера поступает тактирующий импульс (рис 3.5, а). Синхронный RS-триггер строится в соответствии с рис. 3.5, б, а его условное изображение на принципиальных и функциональных схемах приведено на рис. 3.5, в. Синхронизирующий вход обозначается буквой С.  Входные сигналы S и R являются информационными, а на входе С - синхронизирующими, по ним происходит переключение триггера. Следует отметить, что для надежной работы триггера необходимо, чтобы длительность переключающего сигнала (синхронизирующего сигнала) на входе С была не меньше времени переключения триггера. Временем переключения (срабатывания, установки) триггера называется время, которое проходит от момента изменения входных сигналов до соответствующего изменения состояния выходов и определяющееся задержками распространения сигнала логическими элементами, входящими в состав триггера. Статический D триггер В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке 1.  Рисунок 1. Схема D триггера (защелки)  Рисунок 2. Условно-графическое обозначение D триггера (защелки) D-триггер (от английского DELAY) называют информационным триггером, также триггером задержки. Конкретное значение задержки определяется частотой следования импульсов синхронизации. D - триггер бывает только синхронным. Он может управляться (переключаться) как уровнем тактирующего импульса, так и его фронтом. Для триггера типа D, состояние в интервале времени между сигналом на входной линии и следующим состоянием триггера формируется проще, чем для любого другого типа. Таблица истинности D триггера достаточно проста, она приведена в таблице 1. Как видно из этой таблицы, этот триггер способен запоминать по синхросигналу и хранить один бит информации. Таблица 1. Таблица истинности D триггера  Во всех рассмотренных ранее схемах синхронных триггеров синхросигнал работает по уровню, поэтому триггеры называются триггерами, работающими по уровню или статическими триггерами. Ещё одно название статических D триггеров, пришедшее из иностранной литературы — триггеры-защёлки (latch). Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рисунке 8.  Рисунок 8. Временная диаграмма статического D триггера (защелки) Для формирования подобной временной диаграммы уже недостаточно механических ключей на входе схемы и логических пробников на светодиодах. Для формирования входных сигналов потребуются генераторы импульсов, а для наблюдения временных диаграмм к выходу схемы следует подключить многоканальный осциллограф. По временной диаграмме, приведенной на рисунке 8 видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера. Входное напряжение запоминается в статическом D триггере только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы "защелкиваются" в этот момент, отсюда и название — триггер-защелка. Принципиально в схеме статического D триггера входной переходной процесс (опасные гонки) может беспрепятственно проходить на выход D триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту. Динамический D триггерОсновным недостатком простейшего D-триггера (защелки), рассмотренного в предыдущей статье, является наличие режима "прозрачности". Пока на входе синхронизации присутствует высокий потенциал, триггер записывает входную информацию. Для того, чтобы избежать прохождения входного сигнала на выход схемы приходится на вход триггера подавать очень узкие импульсы. Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеальном случае длительность фронта импульса равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять требования к длительности тактового сигнала. Динамический D триггер, запоминающий входную информацию по фронту, может быть построен из двух статических D триггеров. Сигнал синхронизации C будем подавать на статические D триггеры в противофазе. Схема триггера, запоминающего входную двоичную информацию по фронту, приведена на рисунке 1.  Рисунок 1. Схема динамического D триггера, работающего по фронту Рассмотрим работу схемы, приведенной на рисунке 1 подробнее. Для этого воспользуемся временными диаграммами, показанными на рисунке 2. На этих временных диаграммах обозначение Q' соответствует сигналу на выходе первого статического D триггера. Так как на вход синхронизации второго статического D триггера тактовый сигнал поступает через инвертор, то когда первый триггер находится в режиме хранения, второй пропускает сигнал на выход схемы. И наоборот, когда первый D триггер пропускает сигнал с входа схемы на свой выход, то второй находится в режиме хранения.  Рисунок 2. Временные диаграммы динамического D триггера Обратите внимание, что сигнал на выходе всей схемы D триггера в целом не зависит от сигнала на входе "D". Если первый D триггер пропускает сигнал данных со своего входа на выход, то второй статический D триггер в это время находится в режиме хранения и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться. В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 1 запоминается только в момент изменения сигнала на синхронизирующем входе "C" с единичного потенциала на нулевой. Это полезно не только с точки зрения формирования синхронизирующего сигнала. На динамических D триггерах, в отличие от статических, можно строить последовательные регистры и счетчики. В англоязычной литературе только такие схемы называют D триггерами. Условно-графическое обозначение динамического D триггера, запоминающего информацию по фронту тактового сигнала, приведено на рисунке 3.  Рисунок 3. Условно-графическое обозначение динамического D триггера То, что динамический D триггер запоминает входной сигнал по фронту, отображается на условно-графическом обозначении треугольником, изображённым на выводе входа синхронизации. Если запоминание сигнала по входу D происходит по спадающему фронту, то треугольник разворачивают в другую сторону (вершиной ко входу C). То, что внутри динамического триггера находится два статических триггера, отображается в среднем поле условно-графического изображения двойной буквой T.  Рисунок 4. Условно-графическое обозначение динамического D триггера с запоминанием по заднему фронту Иногда при изображении динамического входа используют другое обозначение, по какому фронту триггер (или триггеры) изменяет своё состояние. В этом случае используется обозначение входа, как это показано на рисунке 4.  Рисунок 5. Альтернативное обозначение динамических входов На рисунке 5а обозначен динамический вход, работающий по переднему (нарастающему) фронту сигнала. На рисунке 5б обозначен динамический вход, работающий по заднему (спадающему) фронту сигнала. T-триггеры T-триггер — это счетный триггер. У данного триггера имеется только один вход. Принцип работы T-триггера заключается в следующем. После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T триггер как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние. T-триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному ранее D триггеру. Использование двух триггеров позволяет избежать неопределенного состояния схемы при разрешающем потенциале на входе синхронизации "C", так как счетные триггеры строятся при помощи схем с обратной связью T триггер можно синтезировать из любого двухступенчатого триггера. При этом не важно ТТЛ или КМОП технология используется. Рассмотрим пример синтеза T триггера из динамического D триггера. Для того чтобы превратить D триггер в счётный, необходимо ввести цепь обратной связи с инверсного выхода этого триггера на вход, как показано на рисунке 1.  Рисунок 1. Схема T триггера, построенная на основе D триггера Временная диаграмма T триггера приведена на рисунке 2. При построении этой временной диаграммы был использован триггер, работающий по заднему фронту синхронизирующего сигнала.  Рисунок 2. Временные диаграммы T триггера Т-триггеры используются при построении схем различных счётчиков, поэтому в составе БИС различного назначения обычно есть готовые модули этих триггеров. Условно-графическое обозначение T триггера приведено на рисунке 3.  Рисунок 3. Условно-графическое обозначение T триггера Существует еще одно представление T триггера. При разработке схем синхронных двоичных счетчиков важно осуществлять одновременную запись во все его триггеры. В этом случае вход T триггера служит только для разрешения изменения состояния на противоположное, а синхронизация производится отдельным входом "C". Подобная схема T триггера приведена на рисунке 4.  Рисунок 4. Схема синхронного T триггера, построенная на основе D триггера Подобная схема счетного триггера может быть реализована и на JK триггере. Принципиальная схема синхронного T-триггера, выполненная на JK-триггере показана на рисунке 5.  Рисунок 5. Схема синхронного T триггера, построенная на основе JK триггера Временная диаграмма синхронного T триггера приведена на рисунке 5, а его условно-графическое обозначение — на рисунке 6.  Рисунок 6. Временные диаграммы синхронного T триггера  Рисунок 7. Условно-графическое обозначение синхронного T триггера Выводы T-триггеры широко применяются в схемах деления и умножения частоты. Без них было бы невозможна реализация синтезаторов частот, которые применяются в качестве задающих генераторов в передатчиках и гетеродинов в приемниках раций, мобильных телефонов или GSM навигаторов. Не менее важна роль T-триггеров в формировании тактовой частоты цифровых микросхем, таких как центральные процессоры компьютеров, планшетов или цифровых фотоаппаратов. |