1.2 структурное проектирование. 1. 2 Структурное проектирование

Скачать 175.5 Kb. Скачать 175.5 Kb.

|

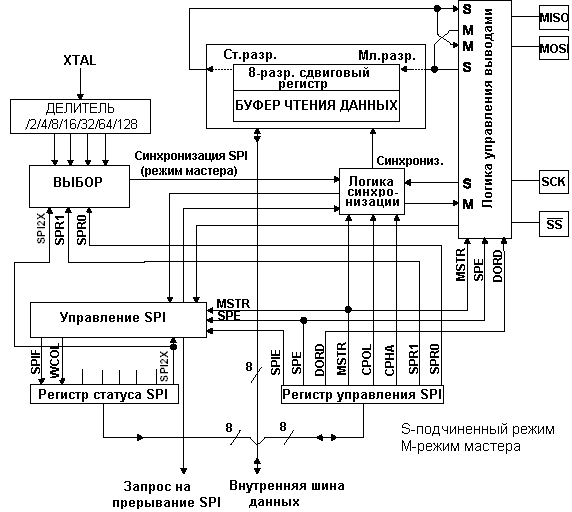

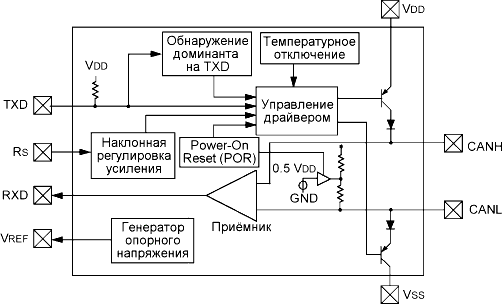

1.2 Структурное проектирование На основе представленной электрической структурной схемы при дальнейшем проектировании будет разработана и внедрена схема электрическая принципиальная, как максимально предметная реализация схемы электрической структурной. Структурная схема разрабатываемого устройства безусловно может быть представлена как совокупность нескольких функциональных блоков, соединённых в единую схему между собой. Программно-аппаратный терминал с CAN-шиной предназначен для максимально быстрой и безопасной передачи информации, от компьютера по интерфейсу RS232, в память подключенного устройства по интерфейсу CAN-bus, и обратно. Согласно предоставленному техническому заданию, программно-аппаратный терминал будут разработан в виде автономного самостоятельного устройства, обеспеченного микроконтроллером, который непосредственно будет осуществлять связь между имеющимися интерфейсами. На рисунке 2.1 показана структурная схема разрабатываемого устройства. В структуре силового преобразователя имеются следующие условные блоки: микроконтроллер; контроллер CAN-bus; приемопередатчик CAN-bus; подключенные устройства CAN-bus; приемопередатчики RS232; ПЭВМ; блок питания +5V.  Рисунок 2.1 – Структурная схема разрабатываемого устройства ПЭВМ, к которой непосредственно подключается модернизируемый терминал, предназначен для осуществления передачи информации непосредственно в присоединенные устройства. К присоединенным устройствам терминал подключается непосредственно через интерфейс CAN-bus. Контроллер CAN-bus необходим для обеспечения надежной и бесперебойной связи приемопередатчика CAN-bus с микроконтроллером и наоборот. Контроллер CAN-bus осуществляет взаимодействие посредством соединения с микроконтроллером с помощью шины SPI. Интерфейс SPI – является синхронным последовательным интерфейсом – целеое его назначение обеспечение организации обмена между двумя устройствами, причем одно из них будет всегда являться инициатором обмена (master), а второе будет являться пассивным (slave). Основные используемые характеристики SPI интерфейса: полнодуплексный 3-х проводной используется синхронный обмен данными; режим работы применяется ведущий или ведомый; обмен данными с возможными передаваемыми первыми старшим или младшим битами; четыре программируемые скорости обмена данными; флаг прерывания по окончании передачи данных. Структурная схема SPI интерфейса показана на рисунке 2.2.  Рисунок 2.2 – Структурная схема SPI интерфейса По факту имеющийся вывод PB1(SCK) является выходом тактового сигнала ведущего микроконтроллера и входом тактового сигнала ведомого микроконтроллера. По записи ведущим CPU данных в SPI регистр приступает к выполнению работы тактовый генератор SPI, записанные данные при этом сдвигаются через вывод выхода PB2(MOSI) имеющегося ведущего микроконтроллера на вывод входа PB2 (MOSI) ведомого микроконтроллера. Обратим внимание, что после сдвига одного байта тактовый генератор SPI останавливается, устанавливая флаг окончания передачи (SPIF). Если в регистре SPCR будет установлен бит разрешения прерывания SPI (SPIE), то произойдет запрос прерывания. Вход выбора ведомого PB0 (SS), для выбора индивидуального SPI устройства в качестве ведомого, устанавливается на низкий уровень. При установке высокого уровня на выводе PB0 (SS) порт SPI деактивируется и вывод PB2(MOSI) может быть использован в качестве вывода входа. Режим ведущий/ведомый может быть установлен и программным способом установкой или очисткой бита MSTR в регистре управления SPI. Важно знать, что сдвиг — это не то же самое, что и вращение, то есть биты, сдвигающиеся на один конец, не появляются с другого. Сдвинутые биты теряются, а с другого конца появляются нули. В том случае, если вправо сдвигается отрицательное число, слева появляются единицы (поддерживается знаковый бит). Операции битового сдвига могут быть полезны при декодировании информации от внешних устройств и для чтения информации о статусе. Операторы битового сдвига могут также использоваться для выполнения быстрого умножения и деления целых чисел. Сдвиг влево равносилен умножению на 2, а сдвиг вправо - делению на 2. Два сдвиговых регистра ведущего и ведомого микроконтроллеров можно рассматривать как один единый разнесенный 16-разрядный циклический сдвиговый регистр. При сдвиге данных из ведущего микроконтроллера в ведомый одновременно всегда происходит сдвиг данных из ведомого микроконтроллера в ведущий, то есть в течение одного цикла сдвига происходит обмен данными между ведущим и ведомым микроконтроллерами. Назначение приемопередатчика CAN-bus предназначено для преобразования последовательного потока данных передаваемых от микроконтроллера в дифференциальный сигнал и наоборот. Структурная схема приемопередатчика CAN показана на рисунке 2.3.  Рисунок 2.3 – Структурная схема приемопередатчика CAN-bus Приемопередатчик RS232 необходим для преобразования уровней сигнала последовательного потока данных микроконтроллера в сигнал интерфейса RS232 и наоборот. Микроконтроллер является центральным ключевым звеном в рабочем устройстве. На него возложено выполнение функциональных задач по обеспечению реализации моста между интерфейсом CAN-bus и RS232. Микроконтроллер будет выполнять данные функции приема и передачи данных между двумя физическими интерфейсами, преобразуя форматы кадров и поддерживая протоколы передачи данных. Для того чтобы обеспечить минимальное количество дополнительных элементов, целесообразно выбрать микроконтроллер, который будет выполнять процесс интеграции в себе максимально полноценно запрашиваемых функций. Выполнив изучение представленной на рынке производителями номенклатуры микроконтроллеров, предложено остановить свой выбор на микроконтроллере семейства AVR фирмы ATMEL. AVR-архитектура объединяет в себе мощный гарвардский RISC-процессор с обеспеченным раздельным доступом к памяти программ и данных, в функции имеется тридцать два регистра общего назначения, каждый из которых может работать как регистр-аккумулятор, и развитую систему команд фиксированной 16-бит длины. Регистровый файл так же доступен как часть памяти данных. Шесть из 32 регистров можно использовать как три 16-разрядных указателя в адресном пространстве данных, что дает возможность использовать высокоэффективную адресную арифметику. Один из трехадресных указателей (регистр Z) можно использовать для адресации таблиц в памяти программ. Один из трехадресных указателей (регистр Z) можно использовать для адресации таблиц в памяти программ. Большинство команд как правило выполняются за один машинный такт с одновременным обязательным исполнением текущей и выборкой последующей команды, что обеспечивает максимальную производительность до 1 миллиона операций в секунду на каждый 1 МГц тактовой частоты. При помощи команд относительных переходов и вызова подпрограмм осуществляется доступ ко всему адресному пространству. При обработке прерываний и вызове подпрограмм адрес возврата запоминается в стеке. Стек размещается в памяти данных общего назначения, соответственно размер стека ограничен только размером доступной памяти данных и ее использованием в программе. Имеются в составе встроенные аналоговый компаратор, сторожевой таймер, порты SPI и UART, таймеры/счетчики. Диапазон напряжений питания от 1,8 В до 6,0 В. Блок питания обеспечивает напряжение питания +5В. Именно такое напряжение необходимо для питания большинства микросхем, используемых в данном устройстве.           Изм. Лист № докум. Подпись Дата Лист 210201.65-2015 ДП-ПЗ |