ЛР 1,2. Изучение работы восьмиразрядных микропроцессоров

Скачать 0.64 Mb. Скачать 0.64 Mb.

|

|

МИНОБРНАУКИ РОССИИ Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В.И. Ульянова (Ленина) Кафедра ЭУТ отчет по лабораторной работе №1,2 по дисциплине «Современные проблемы электроники и микропроцессорные системы в приборостроении» Тема: Изучение работы восьмиразрядных микропроцессоров (Intel 8085 и Z80)

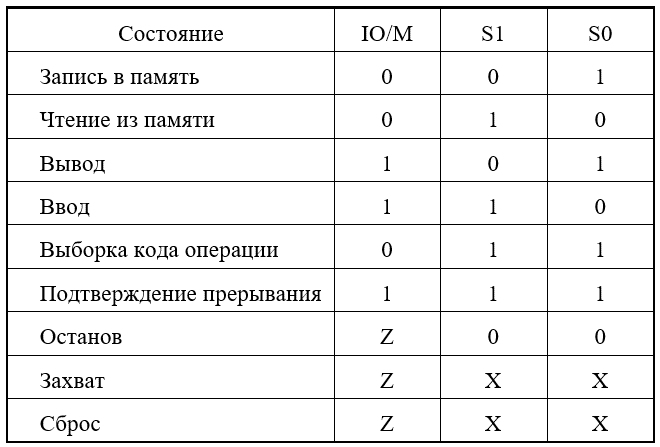

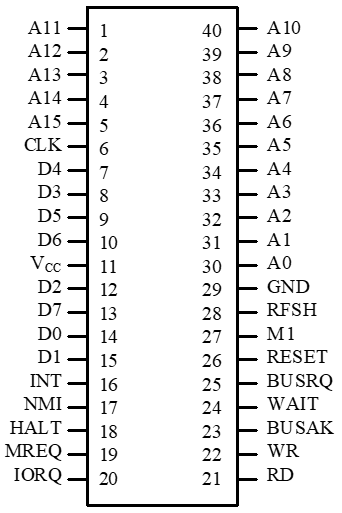

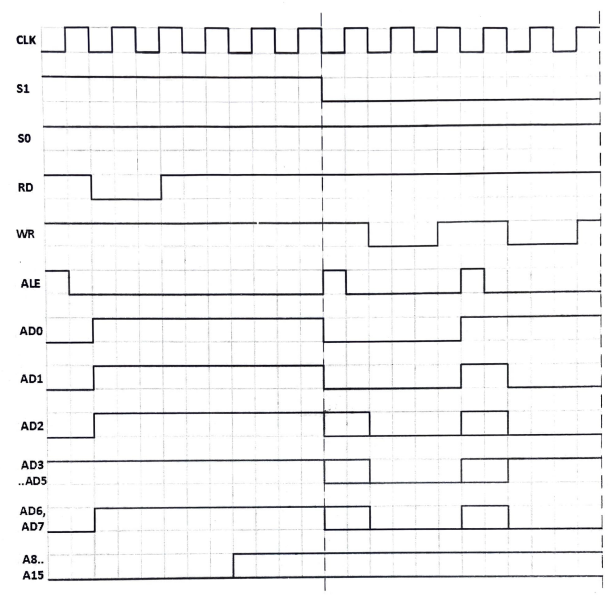

Санкт-Петербург 2022 Цель работы. Ознакомиться с функционированием восьмиразрядных микропроцессоров на примере выполнения команд микропроцессороами Intel 8085 и Z80. Основные теоретические положения. Микропроцессор Intel 8085 является типичным представителем серии восьмиразрядных однокристальных микропроцессоров, предназначенных для построения различных вычислительных и управляющих устройств. В отличие от своего предшественника – Intel 8080 – он использует одно напряжение питания +5 В, имеет встроенный тактовый генератор, более расширенную систему прерываний. Система команд Intel 8085 полностью повторяет систему команд Intel 8080 (см. прил. 2) с добавлением двух команд. Схема расположения выводов Intel 8085 представлена на рисунке 1.  Рисунок 1 - Схема расположения выводов Intel 8085. Рисунок 1 - Схема расположения выводов Intel 8085.Здесь AD0–AD7 – мультиплексированная шина данных и 8 младших разрядов адреса; A8–A15 – старшие 8 разрядов шины адреса; ALE – разрешение фиксации адреса; S0, S1, IO/M – состояния машинного цикла (таблица 1). Т  аблица 1 – логические значения выводов S0, S1 и IO/M при различных состояниях машинного цикла. RD – управление чтением; WR – управление записью; READY – вход сигнала, низкий уровень которого задерживает работу процессора на целое число циклов; HOLD – вход сигнала запроса использования шин адреса и данных; HLDA – выход сигнала, высокий уровень которого указывает, что процессор освободит шины в следующем цикле; INTR, RST5.5, RST6.5, RST7.5, TRAP – входы сигналов прерываний; INTA – выходной сигнал подтверждения прерывания; RESET IN – вход сигнала сброса (устанавливает счетчик команд в нуль и сбрасывает триггеры разрешения прерывания и подтверждения захвата); RESET OUT – выход сигнала, указывающего на то, что произведен сброс центрального процессора; X1 X2 – входы для подключения частотозадающих LC- или RC‑цепей или кварцевого резонатора или внешнего генератора; CLK – выход тактовых импульсов; SID – линия последовательных входных данных; SOD – линия последовательных выходных данных; VCC – питание + 5 В; GND – земля. Микропроцессор Z80 является типичным представителем серии восьмиразрядных однокристальных микропроцессоров, предназначенных для построения различных вычислительных и управляющих устройств. Схема расположения выводов Z80 представлена на рисунке 2.  Рисунок 2 - Схема расположения выводов Z80. Рисунок 2 - Схема расположения выводов Z80.Здесь D0–D7 – восьмиразрядная шина данных; A0–A15 – шестнадцатиразрядная шина адреса; M1 – (машинный цикл 1) низкий уровень указывает, что процессор находится в состоянии выборки кода операции; MREQ, IORQ – состояния машинного цикла (операции чтения/записи памяти M или внешних устройств IO); RD – управление чтением; WR – управление записью; WAIT – вход сигнала, низкий уровень которого задерживает работу процессора на целое число циклов; BUSRQ – вход сигнала запроса использования шин адреса и данных; BUSAK – выход сигнала, высокий уровень которого указывает, что процессор перевел шины в состояние высокого импеданса; INT, NMI – входы сигналов прерываний; HALT – выходной сигнал, указывающий на то, что выполнена команда останова; RESET – вход сигнала сброса (устанавливает счетчик команд в нуль и сбрасывает триггеры разрешения прерывания и подтверждения захвата); RFSH – выход сигнала, указывающего на то, что младшие 7 разрядов адресной шины несут адрес регенерации ОЗУ; CLK – вход для подключения внешнего генератора; VCC – питание + 5 В; GND – земля. Описание лабораторного стенда Схема стенда процессора Intel 8085 представлена на рисунке 3.  Рисунок 3 – Схема стенда (Intel 8085). Рисунок 3 – Схема стенда (Intel 8085).Здесь CPU – микропроцессор Intel 8085, линии шины данных которого AD0–AD7 через резисторы R1–R8 подсоединены к шине питания + 5 В. Высокий уровень на входных линиях CPU (READY, RESET IN, TRAP, INTR, RST5.5, RST6.5, RST7.5, HOLD) также получен путем подсоединения их через резисторы к шине питания. Вывод S1 подведен к клемме “СИНХР.” для синхронизации осциллографа. Сигнал тактовой частоты вырабатывается внутренним генератором микропроцессора, для чего к входам Х1, Х2 подключен кварцевый резонатор Q. Сброс CPU осуществляется нажатием кнопки К (подача нулевого уровня на вход RESET IN).  Схема стенда процессора Z80 представлена на рисунке 4. Схема стенда процессора Z80 представлена на рисунке 4.Рисунок 4 – Схема стенда (Z80). Протокол наблюдений На рисунках 5 и 6 представлены временные диаграммы сигналов CLK, S1, S0, RD, WR, ALE, AD0-AD7, A8-A15 для процессора Intel 8085 (рисунок 5) и временные диаграммы сигналов CLK, M1, RD, WR, D0-D7, A0-A15 для процессора Z80 (рисунок 6).  Рисунок 5 – Временные диаграммы сигналов процессора Intel-8085 Рисунок 5 – Временные диаграммы сигналов процессора Intel-8085 Рисунок 5 – Временные диаграммы сигналов процессора Z80 Рисунок 5 – Временные диаграммы сигналов процессора Z80Обработка результатов Проанализируем временную диаграмму процессора Intel 8085. Временная диаграмма содержит в себе 12 полных тактов. Количество машинных циклов (МЦ) видно по значениям сигнала ALE. ALE — это сигнал включения фиксации адреса. Он поднимается до высокого значения в течение первого состояния машинного цикла и включает младшие 8 битов адреса, если его значение равно 1, в противном случае активируется шина данных. Сигналы шины адреса данных появляются с задержкой на полтакта. ALE равняется 1 в 1, 7 и 10 тактах. Таким образом, на временной диаграмме представлено 3 МЦ. Первый МЦ состоит из 6 тактов, второй из 3 тактов и третий из 3 тактов. По сигналам S0 И S1 видно, что в первом МЦ происходит выработка кода операции (S0= S1=1), а во 2 и 3 МЦ происходит запись данных в память (S1=0, S0=1). Рассмотрим подробнее первый МЦ. При высоком уровне сигнала ALE на мультиплексированной шине данных AD0-AD7 и шине адреса A8-A15 находится адрес начала отсчета считывания (0000 0000 0011 10002). При изменении уровня сигнала управляющей шины ALE на низкий на AD0-AD7 появляются данные (1111 11112 = FFh), которые будут считаны. Считывание данных происходит при низком уровне сигнала RD. Сигнал FFh соответствует команде RST 7 - запуск программы с адреса 38h. Рассмотрим подробнее второй и третий МЦ. При высоком уровне сигнала ALE на мультиплексированной шине AD0-AD7 и шине адреса A8-A15 находится адрес места записи данных в память (адреса записи определить невозможно). При изменении уровня сигнала управляющей шины ALE на низкий на AD0-AD7 появляются данные, которые будут записаны в память (0000 00002 – данные для второго МЦ, 1111 10012 – данные для третьего МЦ). Проанализируем временную диаграмму процессора Z80. Временная диаграмма состоит из 11 тактов. При низком уровне сигнала M1 происходит чтение кода операции. Содержимое счётчика команд PC (адрес кода операции в памяти) подается на шину адреса непосредственно в начале машинного цикла. Через полтакта включается сигнал RD и позволяет передать данные из памяти на шину данных ЦП. По нарастающему фронту третьего такта данные вводятся в ЦП. Этот же фронт используется и для выключения сигнала RD. Во время третьего и четвёртого тактов происходит дешифрация и выполнение извлеченной команды внутри МП. Одновременно с этим производится регенерация динамической памяти: на 7 младших битов шины адреса подается адрес регенерации. Во время регенерации сигнал RD не формируется, чтобы избежать передачи данный из различных областей памяти на шину данных. На восьмиразрядной шине данных D0-D7 находится значение – 1111 11112, что соответствует команде RST 7 - запуск программы с адреса 38h. RST 7. Команда записывается с указанием непосредственного адреса обращения к подпрограмме (RST 38h). Таким образом первый МЦ состоит из 5 тактов. Во втором и третьем МЦ происходит запись данных в память. Длительность этих циклов – по 3 такта. В цикле записи линия WR активизируется, когда данные на шине данных уже стабилизировались, т.е. этот сигнал непосредственно используется как импульс записи для всех типов полупроводниковой памяти. Он выключается на полтакта до изменения содержимого ША и ШД, что удовлетворяет параметрам всех типов полупроводниковых ОЗУ. Данные для записи во втором цикле – 0000 0000, в третьем цикле – 0011 10012 Адрес, по которому ведётся запись определить невозможно. Вывод В ходе лабораторной работы было проведено ознакомление с функционированием восьмиразрядных микропроцессоров на примере выполнения команд микропроцессорами Intel 8085 и Z80. Были проанализированы временные диаграммы работы микропроцессоров. Ответы на вопросы Процессор (микропроцессор) – устройство, отвечающее за выполнение арифметических, логических операций и операций управления, записанных в машинном коде), реализованный в виде одной микросхемы или комплекта из нескольких специализированных микросхем. 1.2) Основные функциональные узлы МП: арифметико-логическое устройство, устройство управления и синхронизации, запоминающее устройство, регистры, шины передачи данных и команд. 2) Процессор имеет специальные ячейки, которые называются регистрами. Именно в регистрах помещаются команды, которые выполняются процессором, а также данные, которыми оперируют команды. Работа процессора состоит в выборе из памяти в определенной последовательности команд и данных и их выполнении. На этом и базируется выполнение программ. 3) Шина адреса предназначена для передачи по ней адреса того устройства (или той ячейки памяти), к которому обращается процессор. Шина данных предназначена для передачи данных между узлами МП. Шина управления служит для направления потока данных, передаваемых по шине данных. 4) Мультиплексная шина адрес-данные выполняет функции шин адреса и данных в различные моменты времени. Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. 5) Выставляют и принимают сигналы на шинах соответствующие регистры. 6) Программа – набор команд, последовательно исполняемых (выполняемых) процессором. Команда — элементарная инструкция, действие, операция, выполняемые вычислительным устройством (процессором). Код операции - часть машинного языка, называемая инструкцией и определяющая операцию, которая должна быть выполнена. 7) Группы команд - 1) пересылки информации, 2) арифметических операций; 3) логических операций; 4) ветвления; 5) управления. 8) Группу команд управления образуют команды, управляющие процедурами ввода-вывода информации, операциями со стеком, и команды проверки текущего состояния процессора. 9) Указатель стека (стек-поинт) – это регистр, который указывает на верхнюю ячейку стека, следующую за последней заполненной ячейкой, куда должны быть записаны новые данные. 10) Командный цикл - Действия по выбору из памяти и выполнению одной команды. 11) Командный цикл состоит из машинных циклов, которые занимают по времени определённое количество тактов. 12) Выполнение команды в лр. 1 и лр. 2 состоит из трёх машинных циклов. 13) В данных машинных циклах выполняется команда RST 7, которая выполняет повторный запуск команды из адреса 38h. |