Электроника. Контрольная работа по курсу электроника

Скачать 0.55 Mb. Скачать 0.55 Mb.

|

|

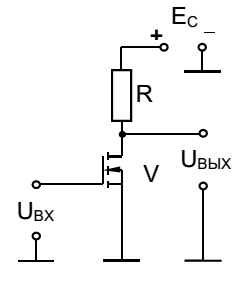

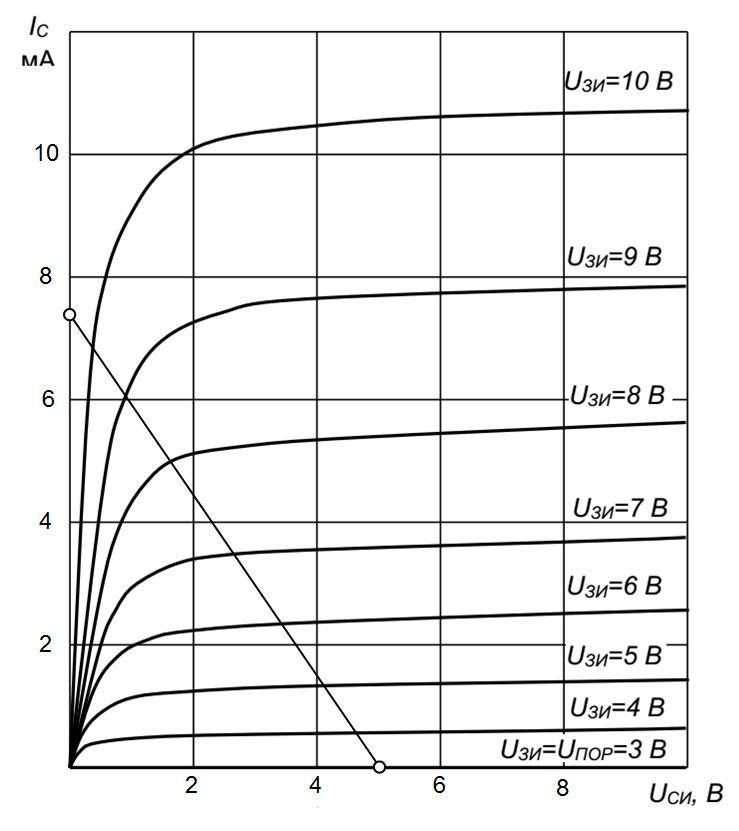

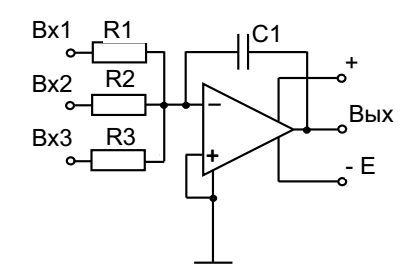

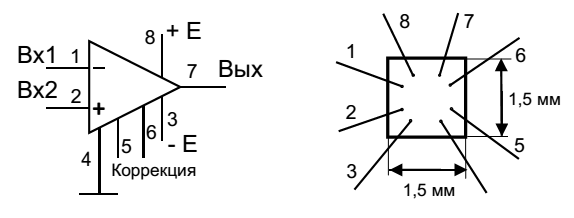

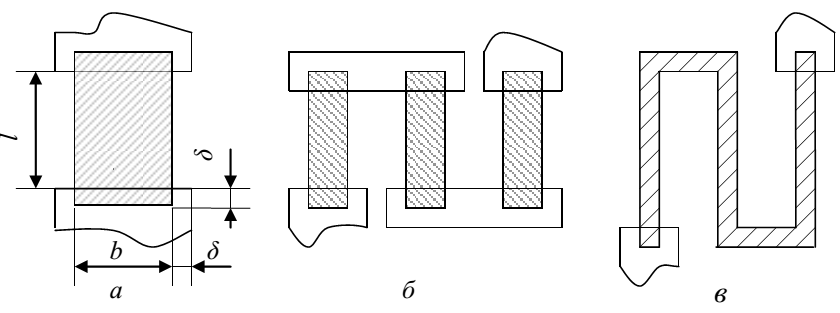

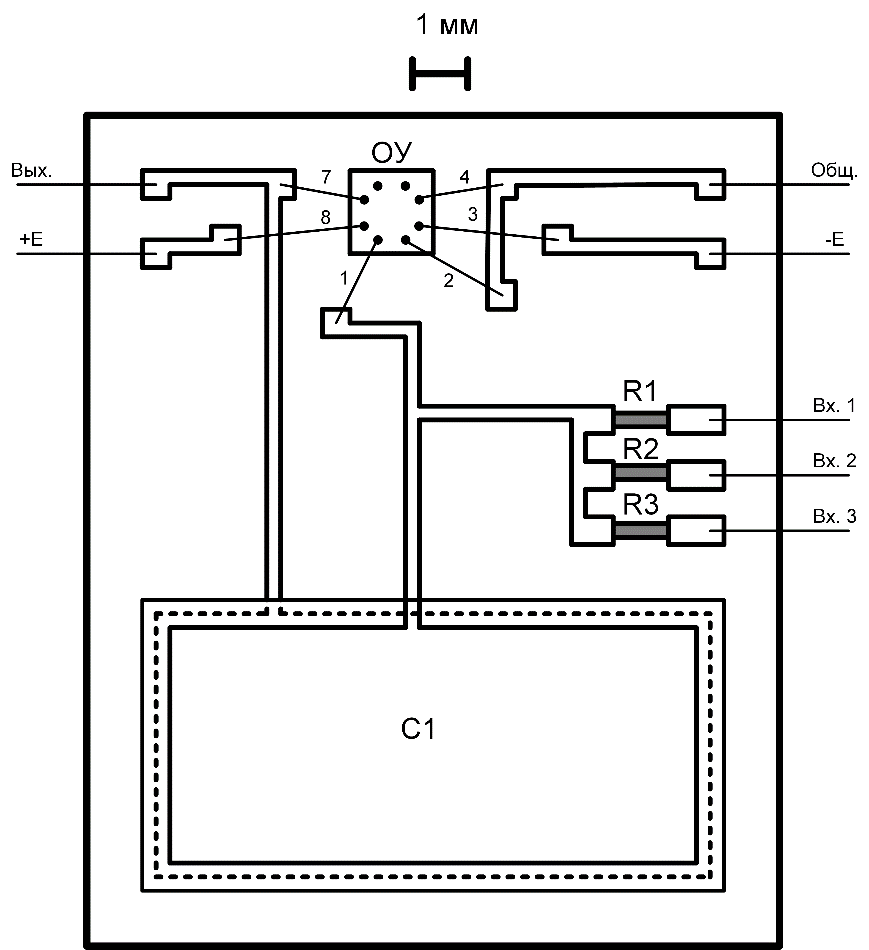

Контрольная работа по курсу «ЭЛЕКТРОНИКА» (вариант 18) Задание 1 Задача 1.2 Схема электронного ключа на МДП-транзисторе изображена на рисунке 1.  Рисунок 1 – Схема электронного ключа Заданы параметры схемы: Величина напряжения источника питания: EC=5,0 В. Сопротивление в цепи стока полевого транзистора: RC=0,68 кОм. Масштабный коэффициент: N=2. Выходные характеристики n-канального МДП-транзистора приведены на рисунке 2.  Рисунок 2 – Выходные характеристики n-канального МДП-транзистора В задании требуется: Построить статическую передаточную характеристику ключа. Определить основные параметры ключа: уровни логических нуля U0 и единицы U1, логического перепада UЛ, минимальные уровни отпирающей и запирающей помехи U0П и U1П, коэффициент помехоустойчивости КП. Описать принцип действия ключа. Решение Полевой транзистор в схеме электронного ключа (рисунок 1) является активным элементом, сопротивление электрическому току между электродами сток-исток которого зависит от величины напряжения между выводами исток-затвор. Резистор в цепи стока предназначен для ограничения величины тока стока при открытом транзисторе. На семействе выходных характеристик полевого транзистора (рисунок 2) строим нагрузочную прямую, предварительно определив координаты точек пересечения нагрузочной прямой с осями координат: Для каждой точки пересечения нагрузочной прямой с выходными характеристиками определяем входные и выходные напряжения для транзистора и заносим их в таблицу 1. Таблица 1 – Координаты точек пересечения

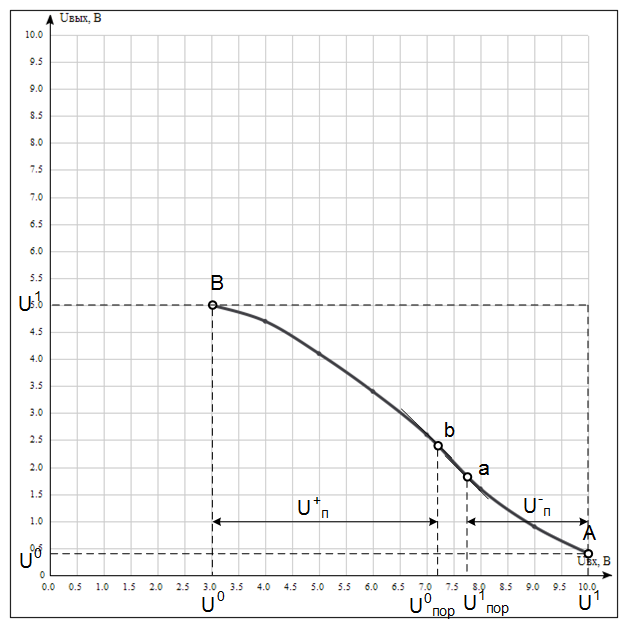

Используя данные таблицы строим передаточную характеристику транзисторного ключа – рисунок 3.  Рисунок 3 – Передаточная характеристика транзисторного ключа Анализируя полученные передаточную характеристику получаем значения параметров электронного ключа. Уровни напряжений, соответствующие логическому нулю и единице: Величина логического перепада выходных уровней: Пороговые значения входного напряжения: Максимальные величины отрицательной и положительной помех: Коэффициент помехоустойчивости ключа:  Электронные ключи характеризуются 2 устойчивыми состояниями: открыт и закрыт. Под состоянием закрыт подразумевается сравнительно большое внутреннее сопротивление активного элемента, входящего в состав электронного ключа. Под состоянием открыт имеют ввиду относительно малое внутреннее сопротивление активного элемента. Другими словами, можно сказать, что активный элемент работает в ключевом режиме, когда он либо открыт, либо закрыт, а промежуточное состояние практически отсутствует. Для полевого транзистора варьируется сопротивление между электродами исток-сток в зависимости от напряжения, приложенного между электродами затвор-исток. В транзисторе с индуцированным n-каналом при наличии напряжения между выводами исток-сток и нулевом напряжении на затворе проводящий канал между стоком и истоком отсутствует. При подаче на затвор положительного напряжения относительно истока возникает поперечное электрическое поле, направленное перпендикулярно поверхности полупроводника, которое выталкивает из приповерхностного слоя дырки и притягивает электроны. Концентрация электронов в приповерхностном слое начинает расти. При росте входного напряжения до величины порогового напряжения концентрация электронов и дырок равны, а при входном напряжении большем чем пороговое напряжение концентрация электронов в приповерхностном слое превышает концентрацию дырок. При этом на поверхности полупроводника формируется (индуцируется) канал с электронной проводимостью. Толщина канала, а значит и его сопротивление, зависят от величины приложенного положительного напряжения к затвору транзистора. Переход транзистора из открытого состояние в закрытое протекает в обратной последовательности. Когда транзистор открыт, т.е. в режиме насыщения, его сопротивление межу выводами сток-исток стремится к нулю. Когда транзистор закрыт, т.е. в режиме отсечки, его сопротивление между выводами сток-исток стремится к бесконечности. Задание 2 На рисунке 4 приведена схема суммирующего интегратора на основе операционного усилителя (ОУ).  Рисунок 4 – Схема суммирующего интегратора Параметры элементов схемы: R1= R2= R3=10 кОм, С1=30 нФ. Способ напыления тонких пленок – катодное напыление. Обозначение выводов и размеры бескорпусного операционного усилителя изображены на рисунке 5.  Рисунок 5 – Обозначение выводов и размеры бескорпусного ОУ В задании требуется разработать топологию тонкопленочной гибридной интегральной схемы, реализующей данное устройство на основе бескорпусного ОУ и нарисовать в чертеж топологии масштабе 10:1. Решение В качестве материала резистивной пленки выбираем сплав РС3710 с удельным сопротивлением: Выбор обусловлен заданным способом напыления тонких пленок и номинальными значениями резисторов заданной схемы. Определяем значение коэффициента формы для каждого резистора: Анализ полученных значений позволяет выбрать конфигурации резисторов в интегральной схеме – рисунок 6.  Рисунок 6 – Конфигурации пленочных резисторов: а – прямоугольной формы, б – в виде нескольких полосок, в – меандр Для R1, R2 и R3 выбираем конфигурацию прямоугольной формы. Определяем размеры пленочных резисторов, исходя из условий, что минимальная ширина bmin=0,1 мм и минимальная длина lmin=0,5 мм. Для всех резисторов выбираем ширину b=0,2 мм, тогда: В качестве диэлектрика пленочного конденсатора выбираем окись тантала с удельной емкостью C0=100000 пФ/см2. Тогда верхней обкладки конденсатора: Предварительно предположим, что верхняя обкладка конденсатора будет иметь прямоугольную форму, с размерами 5 мм на 6 мм. Тогда площадь нижней обкладки и площадь, занимаемая на подложке всей ёмкостью: Общее количество контактных площадок для интегральной схемы: Площадь на подложке, необходимая для размещения контактных площадок: Площадь для размещения резисторов: Площадь для размещения операционного усилителя: Суммарная площадь элементов схемы: Необходимая площадь подложки: Окончательно выбираем подложку с размерами 12 мм на 10 мм. Топология проектируемой гибридной интегральной микросхемы приведена на рисунке 7.  Рисунок 7 – Топология гибридной интегральной схемы, реализующей суммирующий интегратор |