микропроцессор. 1 Микропроцессорные системы управления электротехническими объе. Курсовая работа Пояснительная записка студент г. 631861 Авилова Л. А. Проверил проф. Орлов А. Б. Тула 2008

Скачать 0.72 Mb. Скачать 0.72 Mb.

|

|

Министерство образования РФ Тульский государственный университет Кафедра «Автоматизированные станочные системы» Курс: «Общая электротехника и электроника» Курсовая работа Пояснительная записка Выполнил: студент г.631861 Авилова Л.А. Проверил: проф. Орлов А.Б. Тула 2008 Содержание

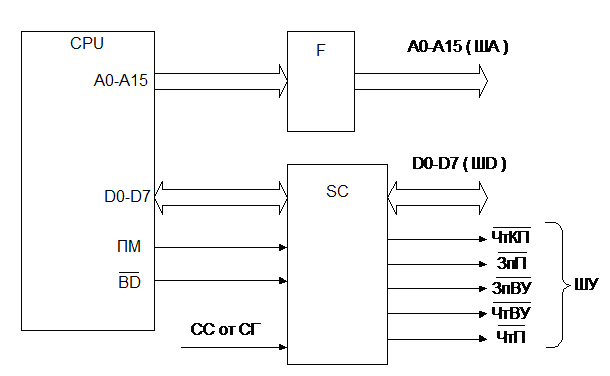

Введение Широкое внедрение в промышленность роботов и гибких производств потребовало существенного расширения и повышения эффективности системы подготовки и переподготовки специалистов в этой области. Создание систем управления роботами и гибкими автоматизированными производствами базируется на средствах вычислительной техники, в первую очередь на больших интегральных схемах и микропроцессорных вычислительных машинах микро-ЭВМ. Поэтому одним из направлений подготовки специалистов по системам управления роботами является изучение принципов работы и методов проектирования устройств управления, построенных на базе выпускаемых промышленностью микропроцессорных наборов и микроЭВМ. Успехи в области микроэлектроники открывают новые возможности для автоматизации производственных процессов, машин, оборудования и приборов на базе микропроцессоров (МП). Микропроцессоры представляют собой устройства обработки цифровой информации, конструктивно выполненные в виде больших интегральных схем (БИС). В основу курсовой работы положено проектирование систем на базе одной серии БИС - БИС КР580. Этот выбор обусловлен следующими причинами: 1. Микропроцессорный комплект БИС КР580 является комплектом общего назначения и используется в управляющей, информационной, измерительной, связной, медицинской, бытовой и другой аппаратуре самого различного применения. 2. Комплект БИС серии КР580 представляет собой один из первых отечественных микропроцессорных комплектов. К настоящему времени уже накоплен достаточный опыт построения аппаратуры на его основе. Объем производства МП и микроЭВМ постоянно возрастает, улучшаются их технические характеристики и снижается стоимость. Благодаря реализованной в них возможности программного управления они обладают свойствами универсальных устройств цифрового управления. Это способствует массовому применению МП и микроЭВМ в народном хозяйстве для цифровой обработки данных и управления различными объектами и процессами. Принцип работы ЭП ПТ и общие требования В комплект ЭП ПТ входит тахогенератор ТГ, который закреплен на валу ЭД. Выходное напряжение ТГ, которое пропорционально частоте вращения вала ЭД, используется для ее контроля. Для управления ЭП ПТ применяются МП контроллеры, которые должны в зависимости от требуемой частоты вращения задавать управляющее напряжение Uупр и контролировать фактическую ее величину по уровню постоянного напряжения, снимаемого с тахогенератора Uтг (рис. 1).  Электропривод постоянного тока ЭД ТГ           Интерфейсный модуль     Процессорный модуль         Микропроцессорный контроллер Рис. 1 Структура электропривода постоянного тока с микропроцессорным управлением В состав МП контроллера входят два модуля: процессорный и интерфейсный. Процессорный модуль осуществляет отработку управляющих программ для реализации алгоритма управления ЭП ПГ. Интерфейсный модуль обеспечивает связь процессорного модуля с электроприводом: преобразование цифровых сигналов в аналоговые и наоборот, промежуточное хранение данных и фиксацию управляющих сигналов. Проектируемый МП контроллер должен обеспечить следующий алгоритм работы ЭП ПТ. Перед пуском ЭД, т.е. перед подачей Uупр, МП контроллер проверяет наличие сигнала "Готовность", поступающего с электропривода (наличие питающего напряжения, снятие различных блокировок и т.д.). При отсутствии данного сигнала МП контроллер не производит пуск ЭД и должен выдать сигнал "Сбой" на световой индикатор. Если сигнал "Готовность" присутствует, то процессорный модуль МП контроллера выдает в интерфейсный модуль цифровой эквивалент Uупр, который цифро-аналоговым преобразователем преобразуется в аналоговую величину. После подачи Uупр на электродвигатель ИП контроллер осуществляет программным способом определенную по времени задержку, необходимую для разгона ЭД до заданной частоты вращения, а затем вводит цифровой эквивалент напряжения ТГ. Преобразование аналоговой величины Uтг в цифровую осуществляется в интерфейсном модуле аналого-цифровым преобразователем. После ввода Uтг МП контроллер приступает к сравниванию ее величины с yровнем Uупр. Если уровень Uтг соответствует Uупр, то пуск произошел в нормальном режиме. Если соответствия нет, то имеет место нештатная ситуация, например, перегрузка ЭД. В этом случае МП контроллер выдает нулевой уровень Uупр (останов ЭД) и сигнал "Сбой", который индицируется светодиодом в интерфейсном модуле. При пуске ЭД могут возникнуть различные аварийные ситуации. При наличии сигнала "Авария" МП контроллер должен прервать подпрограмму пуска, остановить ЭД и выдать сигнал "Сбой". Проектирование блока ЦП В его состав блока ЦП кроме ЦП и системного генератора СГ (на рис. не показан) входят: - однонаправленный буфер шины адреса (БШA); - двунаправленный буфер шины данных (БШД) ; - регистр RG словосостояния ЦП; - логическая схема формирования шины управления (ШУ); Включение БША должно быть таким, чтобы все 16 разрядов ША передавались с его входа на выход. Так как ШД двунаправленная, то направлением передачи информации через ВИД необходимо управлять. Это осуществляет сигнал "Прием" (ПМ). При уровне лог.1 сигналы с ШД через БШД должны передаваться в ЦП, а при лог.0 - из ЦП в ШД. В начале каждого машинного цикла микропроцессора на ШД выдается восьмиразрядное словосостояние ЦП, отдельные разряды которого используются для формирования сигналов ШУ.  Рис.2 Структурная система блока ЦП с применением системного контролера Словосостояние ЦП определяет действия выполняемые микропроцессором в данном машинном цикле чтение/запись ЗУ, чтение/ запись внешних устройств (ВУ) и т.д. Словосостояние фиксируется в регистре RG по сигналу "Строб состояния" (СС) от системного генератора и хранится в нем до окончания машинного цикла. Логическая схема служит для формирования следующих управляющих сигналов ШУ: - ЧтКП - чтение контроллера прерывания; - ЗпП - запись в память; - ЗпВУ - запись во внешнее устройство; - ЧтВУ - чтение с внешнего устройства; - ЧтП - чтение из памяти. Сигналы ПМ и ВД ("Выдача") в логической схеме используются для стробирования управляющих сигналов. Схема подключения СГ к ЦП стандартная и приведена в приложении. Кварцевый резонатор BQ 1 обеспечивает возбуждение генератора. Интегрирующая цепочка RC служит для первоначального сброса СГ и ЦП при включении питания, а кнопка SB1 - для принудительного сброса. На входе "Готовность" IT присутствует уровень лог.1, т.к. предполагается, что быстродействие ЗУ и ВУ соизмеримо с быстродействием ЦП. Другой вариант построения блока ЦП представлен на рис.2. Здесь вместо БШД и логической схемы используется микросхема системного контроллера СК, объединяющая их в одном корпусе. Стробирование СК при записи словосостояния осуществляется сигналом СС, поступающим с СГ. Проектирование блока ЗУ Разработку блока ЗУ рассмотрим на примере. Пусть требуется спроектировать блок ЗУ со следующими параметрами: - объем ОЗУ - 8Кб - организация микросхем ОЗУ – 2Кб х 8 - объем ПЗУ - 2Кб - организация микросхем ПЗУ – 0,5Кб х 8 Это означает, что ОЗУ должно иметь объем 8К байта при использовании микросхем, позволяющих хранить 1024 четырехразрядных слов. Соответственно и для ПЗУ. Блок ЗУ организуется по страничному принципу. Каждая страница образована заданными микросхемами в количестве, позволяющем хранить 8-ми разрядные слова. Для хранения в ОЗУ 1 Кбайта необходимы две микросхемы с организацией 2Кбх8. Причем одна из них будет хранить младшие разряды байта Д0 - Д3, а другая - старшие Д4 - Д7. Для организации ОЗУ в 8К байта необходимы две страницы, т.е. четыре микросхемы с заданной организацией. Соответственно ПЗУ будет состоять из четырех страниц, каждая из которых будет организована на одной микросхеме. Выбор той или иной страницы памяти производит адресный дешифратор. Для его разработки необходимо составить таблицу адресов ЗУ (табл. 1): Начальный адрес 0 -й страницы ОЗУ - 00 0016, а конечный – 1FFF16, т.к. последний адрес представляется логическими 1 во всех десяти разрядах А0 - А9. Начальный адрес следующей страницы ОЗУ формируется как двоичная сумма конечного адреса предыдущей страницы и логической 1 в младшем разряде, т.е. имеем перенос 1 в разряд А10. Для определения конечного адреса этой страницы к начальному адресу прибавляем 210 ,т.е. код с логическими 1 в разрядах А0 - А9. Аналогично строится таблица для страниц ПЗУ. Анализ таблицы позволяет заключить, что отличие адресов 0-й и 1-й страниц ОЗУ состоит в разряде А10. Если А10 = 0, то обращение производится к 0-й странице, а если А10 = 1 , то к 1-й странице ОЗУ. Если в разряде A11 появляются логические 1, то производится адресация ПЗУ, а если 0 - то ОЗУ. Причем номер страницы ПЗУ определяется состоянием разряда A8. Если А8 = 0, то производится обращение к 0 странице ПЗУ (при условии А11 = 1), если А8 = 1, то производится выбор 1-й страницы ПЗУ. На основании проведенных рассуждений строится адресный дешифратор. Используемые дешифраторы имеют вход " Разрешение дешифрации" Р. Если на этом входе присутствует уровень логического 0, то дешифрация разрешена. На вход разрешения первого дешифратора подаются сигналы ЧтП и ЗпП, объединенные по "И". В этом случае дешифрация номеров страниц ЗУ будет производится только в том случае, когда имеет место обращение к ЗУ. Сформированные сигналы "Выбор страниц" поступают на входы "Выбор микросхем" (ВМ) каждой страницы ЗУ. При наличии уровня логического 0 на этом входе микросхема ЗУ выводится из высокоимпедансного состояния и, если это схема ПЗУ, то её выход подключается к ШД, на которую поступают данные выбранные по адресу в соответствии с состоянием разрядов А0 - А7. Таблица 1. Адресное пространство ЗУ

|