вычислит техника. методичка ВТ к_р. Методическое пособие по выполнению контрольной работы по дисциплине вычислительная техника

Скачать 306.54 Kb. Скачать 306.54 Kb.

|

|

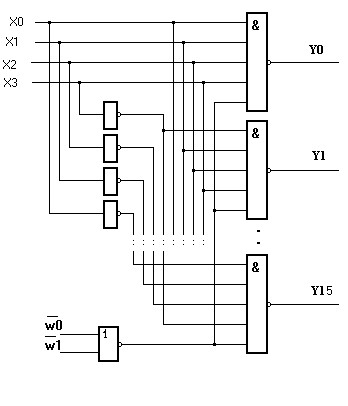

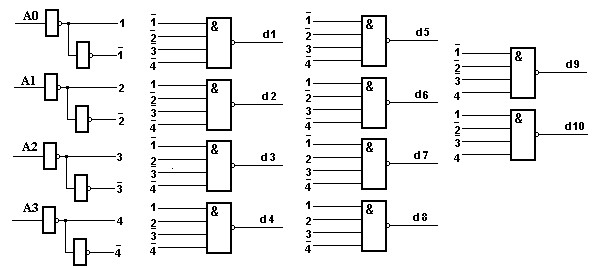

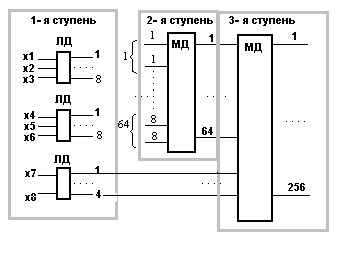

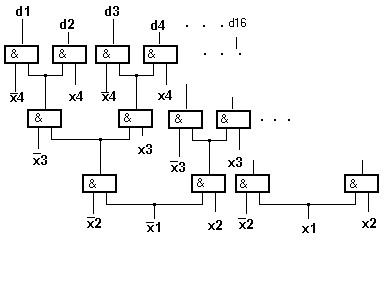

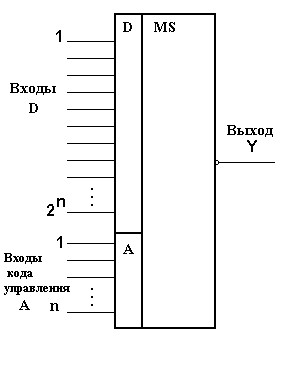

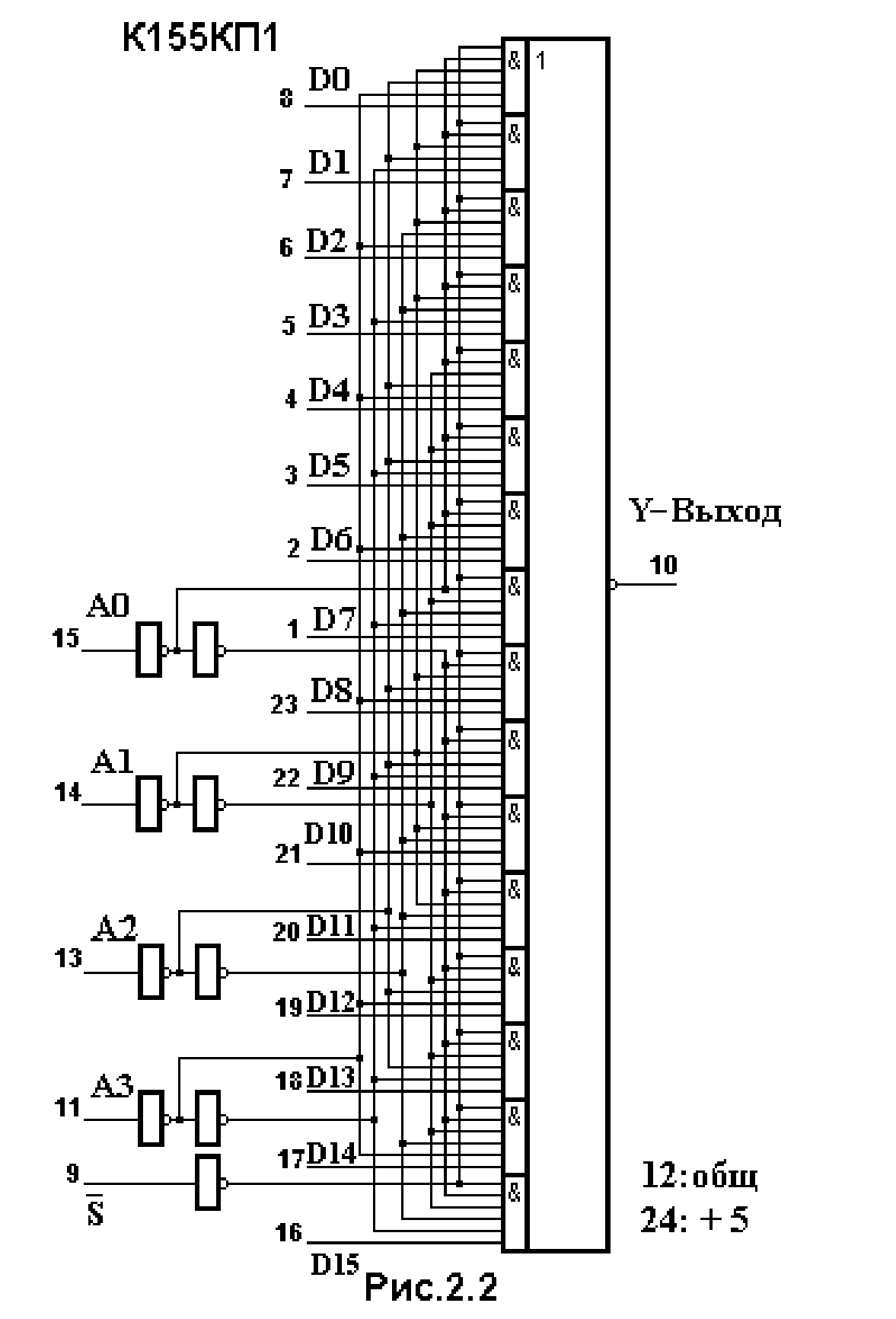

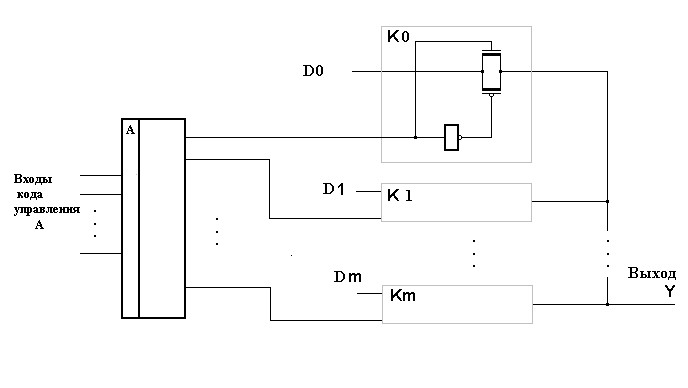

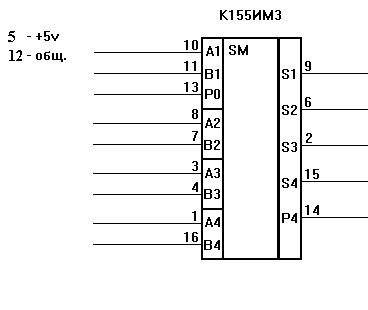

Министерство цифрового развития, связи и массовых коммуникаций Российской Федерации Ордена Трудового Красного Знамени федеральное государственное бюджетное образовательное учреждение высшего образования «Московский технический университет связи и информатики» 09.03.02 Информационные системы и технологии МЕТОДИЧЕСКОЕ ПОСОБИЕ по выполнению контрольной работы по дисциплине «ВЫЧИСЛИТЕЛЬНАЯ ТЕХНИКА» Москва 2022 Составители (разработали): Гематудинов Р.А., к.т.н. и.о. зав. кафедрой «Системное программирование», Чантиева М.Э., к.т.н., доцент кафедры «Математической кибернетики и информационных технологий» Рассмотрено на заседании кафедры «Системное программирование Протокол № 5 от « 17 »января 2022 г. _______________________ (Подпись зав. кафедрой) Одобрено и утверждено редакционным советом ____________________ (Подпись председателя РС) «_____»_____________20__г. №_____________________ Методические указания предназначены для студентов дневной и заочной форм обучения для выполнения контрольных работ по дисциплинам: «Вычислительная техника» специальности 09.03.02 Информационные системы и технологии ВведениеВсе контрольные работы курса разбиты на тематические блоки: - логические элементы; комбинационные схемы; триггерные и пересчетные устройства; управляющие устройства; схемотехника интерфейсов; - запоминающие устройства; - схемотехника АЦП и ЦАП. Настоящие методические указания содержат краткое описание принципов работы комбинационных элементов и порядок проведения контрольных работ «Комбинационные схемы». Цель работы: Контрольная работа «Комбинационные схемы» предназначена для практического изучения принципов построения и функционирования комбинационных схем: дешифраторов, мультиплексоров и сумматоров. 1 ДешифраторыДешифраторы относятся к комбинационным схемам, которые предназначены для преобразования двоичного или двоично-десятичного кода в позиционный. Общепринятое условное обозначение двоичного дешифратора показано на рисунке 1.1.  Рисунок 1.1- Условное обозначение двоичного дешифратора Данный дешифратор имеет четыре входа и 16 выходов. В зависимости от разрядности дешифрируемого кода и функциональных возможностей интегральных схем (ИС), имеющихся в распоряжении разработчика, дешифратор может быть выполнен на основе одноступенчатой (линейной) или многоступенчатой схем дешифрации. Линейные дешифраторы выполняются прямой схемной реализацией системой логических выражений вида: Y0 =X0∗X1∗Х2∗...∗Xm-1, (1) Y1 =X0∗X1∗Х2∗...∗Xm-1, (2) Y2 =X0∗X1∗Х2∗...∗Xm-1, (3) .................................... Yn-1 =X0∗X1∗Х2∗...∗Xm-1, (n)где Y0, Y1,…. ,Yn-1 – выходные логические функции; X1, X2,..., Xm-1; X1, X2,..., Xm-1 – входные логические переменные и их отрицания ; ∗ – знак логического умножения; n=2m – множество комбинаций входных переменных (число выходов полного дешифратора). Таким образом, линейный дешифратор представляет собой 2m независимых по выходам вентилей с m входами каждый. На рисунке 1.2 показана схема четырехразрядного линейного дешифратора.  Рисунок 1.2 - Функциональная схема линейного четырехразрядного двоичного дешифратора Одноступенчатые линейные дешифраторы эффективны, когда разрядность входного кода не превышает числа входов схемы И типового логического элемента ИС. Линейный одноступенчатый дешифратор обладает самым высоким быстродействием в сравнении с другими типами дешифраторов. Одной из наиболее популярных ИС линейных дешифраторов является двоично-десятичная схема SN7445 фирмы TEXAS (USA) (рисунок 1.3). Это двоично-десятичный дешифратор, преобразующий двоично-десятичный код в позиционный десятиразрядный код.  А0- А3 – входные логические переменные; d1- d10 – выходы дешифратора. Рисунок 1.3 - Функциональная схема линейного двоично-десятичного дешифратора SN7445 фирмы TEXAS Прямоугольный или матричный дешифратор (рисунок 1.4) содержит первую ступень из нескольких линейных дешифраторов (ЛД), на каждом из которых дешифрируется группа разрядов входного слова. Количество ЛД определяется числом групп, на которое разбивается входное слово. Во второй ступени прямоугольного дешифратора осуществляется парное совпадение выходных сигналов двух линейных дешифраторов первой ступени по матричной схеме на двухвходовых вентилях (матричный дешифратор). На третьей ступени прямоугольного дешифратора осуществляется парное совпадение 64-х выходных сигналов второй ступени и 4-х выходных сигналов третьего ЛД первой ступени по матричной схеме на двухвходовых вентилях. На рисунке 1.4 показана схема построения прямоугольного дешифратора на 256 выходов. При оптимальном разбиении входного слова общее число вентилей, необходимых для построения матричного дешифратора равно 2 m +2 2+m/2 Другой разновидностью многоступенчатых дешифраторов являются пирамидальный дешифратор. Особенностью пирамидального дешифратора является применение во всех ступенях дешифрации двухвходовых вентилей с обязательным подключением выхода элемента i-й ступени к входам только двух элементов i+1-й ступени. Число ступеней в пирамидальном дешифраторе на единицу меньше разрядности дешифрируемого числа. Число вентилей в каждой ступени равно 2 i+1, где i - номер ступени. Общее количество вентилей на дешифратор равно (2 m+1- 4). На рисунке 1.5 показан пирамидальный дешифратор на 16 выходов.  Рисунок 1.4- Структурная схема прямоугольного дешифратора на 256 выходов  х1- х4 – входные переменные; d1- d16 – выходы дешифратора. Рисунок 1.5 - Функциональная схема пирамидального дешифратора на 16 выходов Контрольные вопросы Опишите принципы построения линейных дешифраторов. Поясните принцип действия матричного дешифратора как на функциональном, так и на уровне логических элементов. Каким образом строится пирамидальный дешифратор? От чего зависят сложность и быстродействие дешифратора? 2 МультиплексорыМультиплексоры - это комбинационные устройства, предназначенные для коммутации одного из нескольких источников логических сигналов к одной выходной шине. Обозначение мультиплексора приведено на рисунке 2.1.  Рисунок 2.1- Условное обозначение мультиплексора Мультиплексор имеет n входов кода управления (может также иметь входную логику для выбора кристалла), 2n входов для данных и один выход. Логическая схема мультиплексора показана на рисунке 2.2 и включает в себя дешифратор и коммутаторы сигналов, объединенные по выходам. Причем, объединение по выходам может осуществляться двумя способами: объединение с помощью многовходового логического элемента ИЛИ либо с помощью монтажного ИЛИ. В последнем случае большой интерес представляют КМОПмультиплексоры, в которых роль коммутаторов выполняют двухсторонние КМОП- ключи, как показано на рисунке 2.3. Такие ключи осуществляют двухстороннюю передачу не только логического сигнала, но и аналогового. Таким образом, КМОП- мультиплексор является одновременно и двухсторонним коммутатором аналоговых сигналов. Мультиплексоры, имеющие режим высокого выходного сопротивления (в частности КМОП- мультиплексоры) могут объединяться по выходам для подключения к общей шине без дополнительных согласующих элементов.  Рисунок 2.2 - Схема мультиплексора  Рисунок 2.3- Схема мультиплексора с КМОП-ключами Контрольные вопросы Перечислите и опишите принципы построения мультиплексоров на функциональном уровне. От чего зависят сложность, быстродействие и функциональные возможности мультиплексоров? СумматорыСумматоры предназначены для выполнения арифметических и логических операций над числами, представленными в двоичном, двоично-десятичном и других кодах. Различают одноразрядные и многоразрядные, последовательные и параллельные сумматоры. В цифровых схемах применяются одноразрядные сумматоры на два (полусумматор) и на три входа (полный одноразрядный сумматор). Логические функции, реализуемые полусумматором: S=A+B, (1) P=AB, (2) где S - сумма; A, B - входы слагаемых; P - выход переноса. Логические функции, реализуемые полным сумматором: S=A+B+C, (3) P=AB+AC+BC, (4) где С - вход переноса. Полные сумматоры можно объединять в параллельные многоразрядные сумматоры. На рисунке 3.1 приведена схема двухразрядного сумматора ИС типа SN7482. Положительным свойством такой реализации является отсутствие инверсных входов, что позволяет на небольшом числе выводов ИС увеличить ее функциональную сложность. Задержка формирования суммы при этом равна 2t, где t - время срабатывания одного логического элемента. На рисунке 3.2 приведено обозначение полного четырехразрядного сумматора - ИС типа К155ИМ3.  Рисунок 3.1- Схема полного двухразрядного сумматора  Рисунок 3.2 - Условное обозначение полного четырехразрядного сумматора К155ИМ3 Контрольные вопросы Какую переключательную функцию реализует полусумматор? Какую переключательную функцию реализует сумматор? Объясните принцип работы сумматора по схеме на рисунке 3.1. От чего зависят сложность и быстродействие сумматора? Объясните назначение выводов сумматора 155ИМ3 по рисунку 3.2. 5 Дополнительные контрольные вопросы5.1 Дайте классификацию комбинационных схем. 5.2 Объясните отличительные особенности функционирования различных комбинационных схем. 5.3 Как осуществляется синтез и анализ комбинационных схем? 5.4 Поясните, что такое гонки и состязания, как их можно выявить и устранить. 5.5 Объясните работу всех приведенных в описании контрольнрой работы схем, их особенности. 6 Порядок выполнения контрольной работыПри подготовке к контрольной работе согласно учебной программе курса в счет часов самостоятельной работы студентов выполните следующее: -получите от преподавателя вариант тестируемых микросхем (таблица 1) на занятии, предшествующем данной контрольной работе; -изучите по основной и дополнительной литературе, приведенной в рабочей программе к курсу "Вычислительная техника", основы построения и принципы действия следующих комбинационных схем: дешифраторов и шифраторов, демультиплексоров и мультиплексоров, сумматоров и компараторов цифровых сигналов; Таблица 1- Типы тестируемых микросхем

-проработайте методические указания к настоящей контрольной работе; -начертите эскизы схем включения всех предложенных к проверке микросхем, используя приведенные в справочниках общепринятые для выполнения электрических схем обозначения комбинационных элементов, источников питания, общих шин, клемм и проводников; -составьте для всех схем таблицы, иллюстрирующие работу полного четырехразрядного сумматора, дешифратора, мультиплексора, компаратора для различных кодов входных сигналов (таблица 2). Для проверки функционирования микросхем разработайте схему, в которой для задания кодовых комбинаций на управляющие входы дешифратора и мультиплексора или для задания пары чисел на сумматор (или компаратор) используются выходы двух четырехразрядных счетчиков, а для контроля состояния выходных сигналов микросхем применяются светодиоды. Таблица 2- Пример фрагмента таблицы, иллюстрирующей работу четырехразрядного сумматора

-представьте преподавателю заполненные таблицы, схемы включения и проверки функционирования, ответьте на контрольные вопросы; -подготовьте отчет по контрольной работе и представьте его для защиты и получения зачета. 7 Содержание отчетаВ отчете должны быть приведены: -теоретический материал в объеме, достаточном для успешной защиты выполненной контрольной работы; -разработанные схемы и экспериментальные таблицы функционирования микросхем; -выводы по контрольной работе. Список использованных источниковОлифер В. Г. Сетевые операционные системы / В. Г. Олифер, Н. А. Олифер - СПб.: Питер, 2014. - 544 с. Душкин А. В. Информационные технологии и системы : учебник / С. В. Белокуров, А. В. Душкин, В. И. Сумин и др. - Воронеж : Научная книга, 2012.-568 с. Келим Ю. М. Вычислительная техника : учеб, пособие для студ. сред, проф. образования / Ю. М. Келим. - М. : Академия, 2005. - 384 с. Мышляева И. М. Цифровая схемотехника : учебник для сред. проф. образования / И. М. Мышляева. - М. : Академия, 2005. - 400 с. Микушин А. В. Цифровые устройства и микропроцессоры / А. В. Ми- кушин. - М. : БХВ-Петербург, 2010.-338 с. Нешумова К. А. Электронные вычислительные машины и системы / К. А. Нешумова. - М. : Высшая школа, 1989. - 354 с. Столлингс В. Структурная организация и архитектура компьютерных систем : пер. с англ. / В. Столлингс. - М. : Вильямс, 2012. - 896 с. Браммер Ю. А. Импульсные и цифровые устройства : учебник / Ю. А. Браммер, И. Н. Пащук. - М. : ИНФРА-М, 2005. - 208 с. Гук М. Аппаратные средства IBM PC : Энциклопедия. - 2-е изд. / М. Гук. - СПб. : Питер, 2005. - 923 с. Аппаратные интерфейсы ПК: Энциклопедия / М. Гук - СПб. : Питер, 2002. - 528 с. Калачев А. В. Многоядерные процессоры / А. В. Калачев. - Интернет- университет информационных технологий, Бином. Лаборатория знаний, 2014. - 248 с. Шишкин Г. Г. Электроника : учебник для вузов / Г. Г. Шишкин, А. Г. Шишкин. - М. : Дрофа, 2009. - 702 с. Орлов С. А. Организация ЭВМ и систем. Фундаментальный курс по архитектуре современных компьютерных средств : учебник для вузов / C. А. Орлов, Б. Я. Цилькер. - СПб.: Питер, 2011. - 688 с. Баранов И. Ю. Аппаратные средства вычислительной техники. Функциональная и структурная организация ЭВМ / И. Ю. Баранов. - Орел : Академия ФСО России, 2006. - 134 с. Пирогов В. В. Аппаратные средства вычислительной техники. Процессоры и система памяти ЭВМ : учеб, пособие / В. В. Пирогов, И. Ю. Баранов, А. К. Абрамов. - Орел : Академия ФСО России, 2008. - 222 с. Баранов И. Ю. Аппаратные средства вычислительной техники. Внутренняя коммуникационная система и система ввода-вывода ЭВМ : учеб, пособие / И. Ю. Баранов, А. К. Абрамов. - Орел : Академия ФСО России, 2009. - 149 с. Евреинов Э. В. Цифровая и вычислительная техника / Евреинов Э. В. - М. : Радио и связь, 1991. - 257 с. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||