Рэснаплисезадание1. РЭС на ПЛИС Лаб 1 - введение в разработку. Vivado 2016 Написание модулей на языке Verilog

Скачать 0.56 Mb. Скачать 0.56 Mb.

|

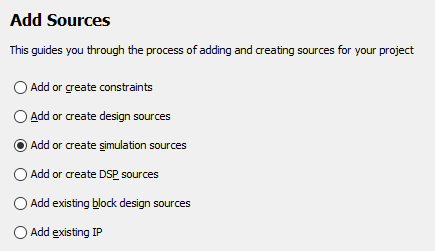

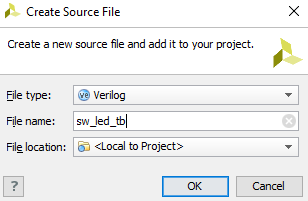

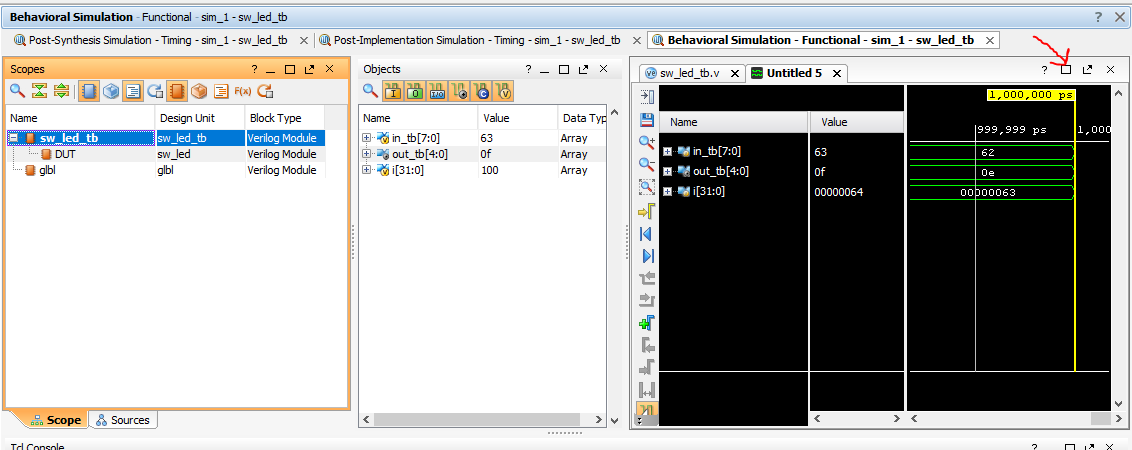

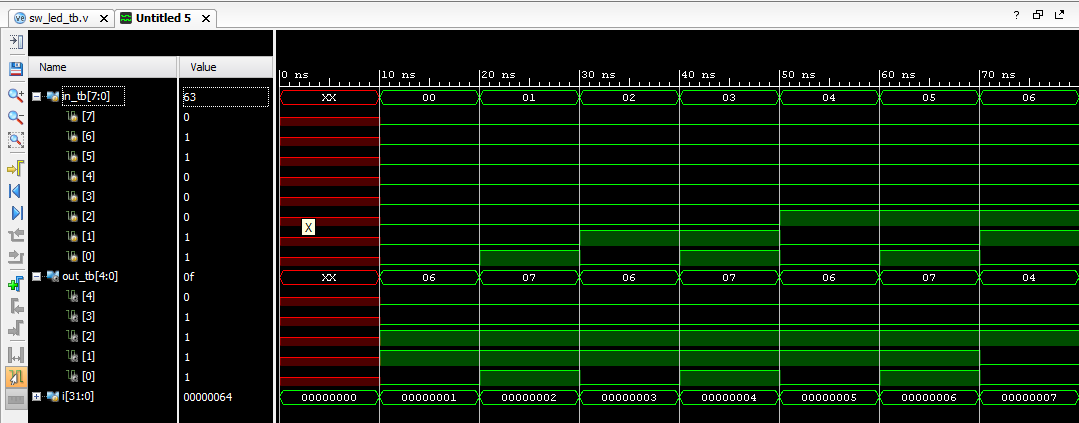

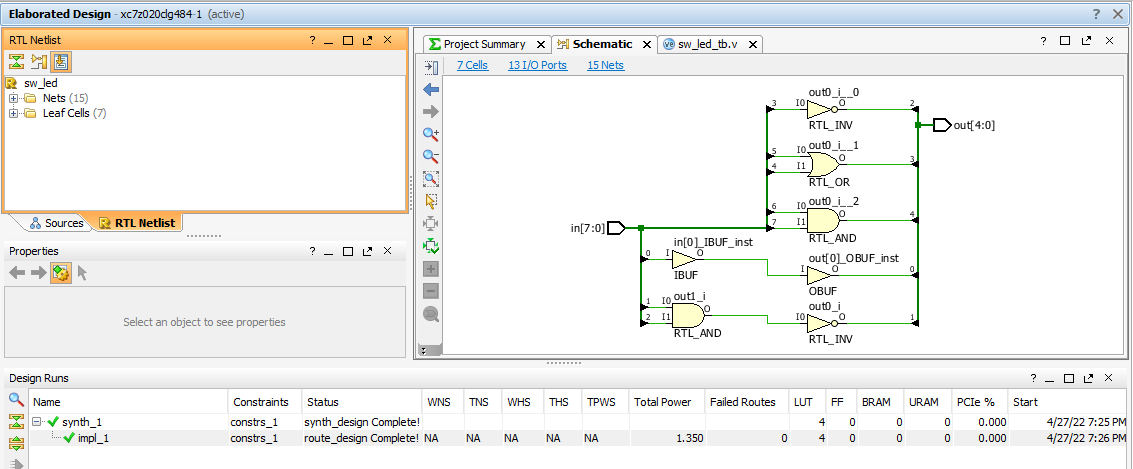

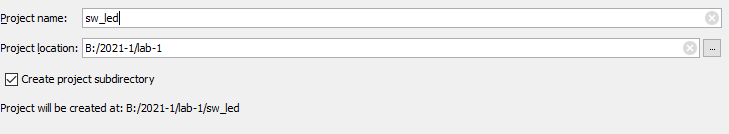

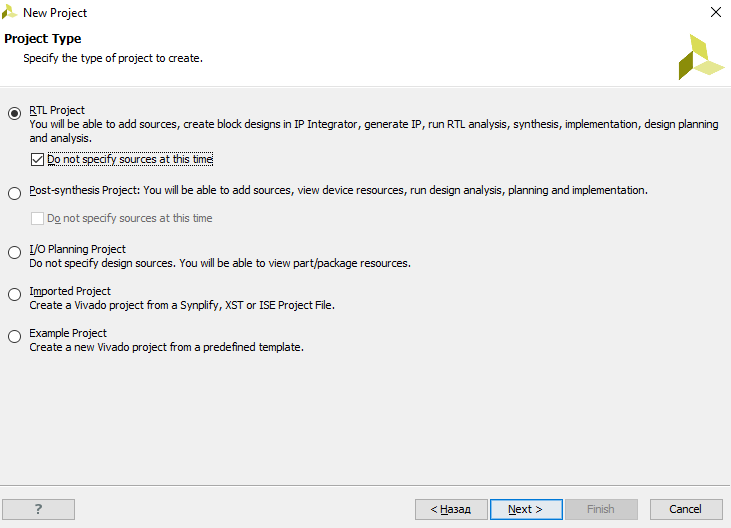

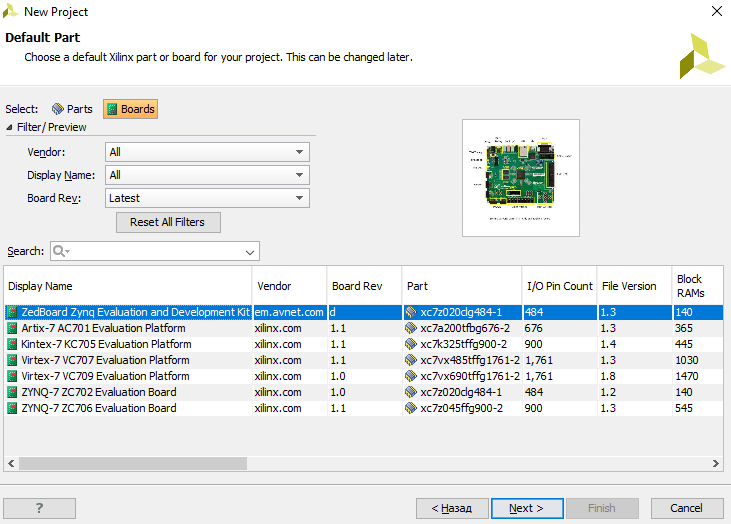

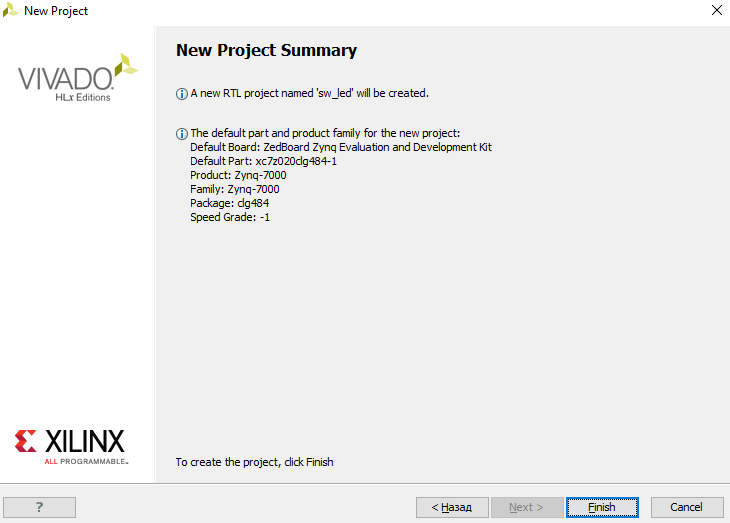

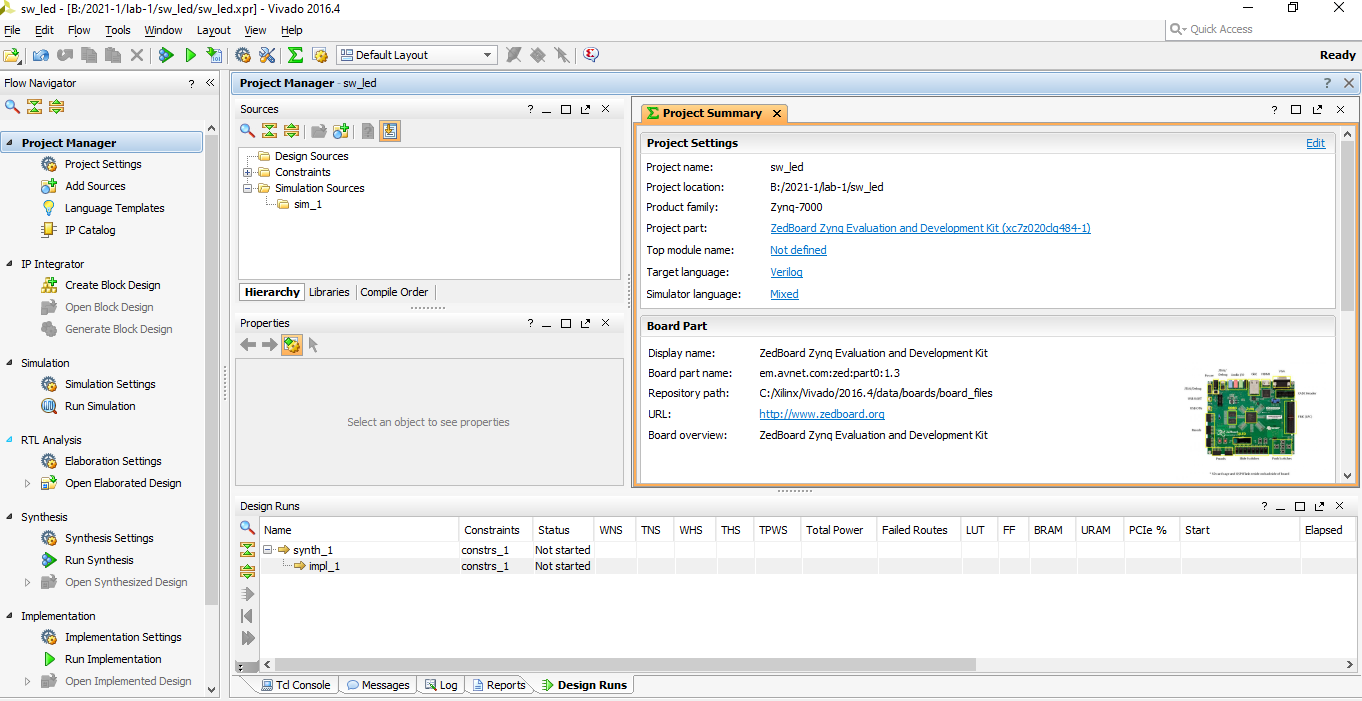

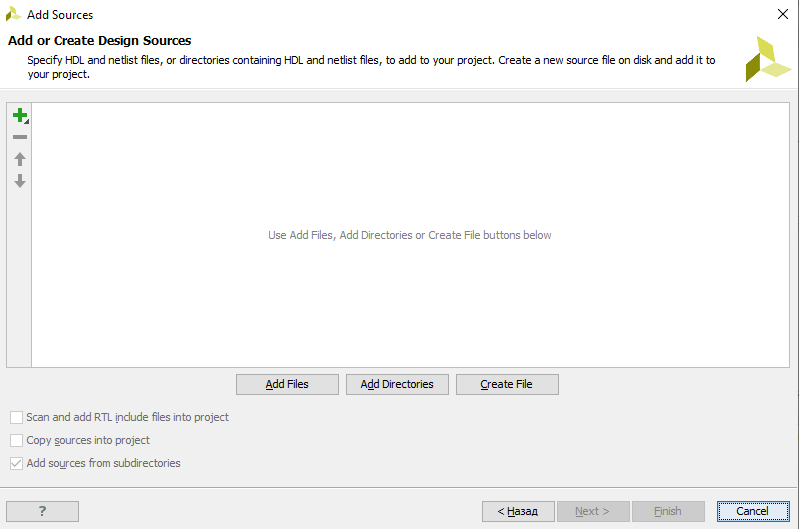

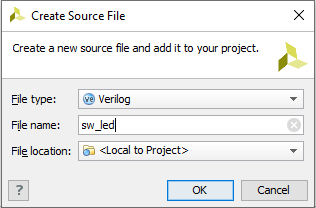

(in[1] & in[2]);Лабораторная работа 1 ОСНОВЫ РАЗРАБОТКИ ПРОЕКТА В СРЕДЕ VIVADO Цель работы Изучение среды разработки цифровых устройств на ПЛИС Xilinx Vivado 2016.4. Написание модулей на языке Verilog и тестирующих окружений. Проверка работоспособности разработанного устройства на временной симуляции в XSim. Основные вопросы, изучаемые перед выполнением работы Основы комбинационной логики Введение в Verilog Содержание работы Ознакомиться с приложением 1. Создать на разделе D директорию (год обучения)-(семестр). В созданном каталоге создать индивидуальную директорию (Фамилия на литинице)-(группа). Для каждой лабораторной работы создается каталог lab-(номер лабораторной). Например, полный путь для первой лабораторный работы: D:/2021-1/Ivanov_RT51/lab-1 Создание проекта в Vivado 2016.4 Выбрать пункт Create New Project (рис. 1) и в открывшемся окне нажать Next Р  ис. 1. Окно создания проекта Введите имя проекта sw_led (рис. 2) и укажите путь к созданной ранее директории, оставив отметку напротив Create project subdirectory – это позволит создать для проекта отдельный каталог и поместить в него все файлы проекта. Данная функция будет активно использована в последующих работах, в рамках которых будет создано несколько проектов. Р  ис. 2. Окно выбора директории проекта Нажмите Next. Убедитесь, что в следующем окне установлен указатель RTL project и установлена отметка Do not specify sources at this time и нажмите next (рис. 3).  Рис. 3. Окно выбора типа проекта В следующем окне выберите вкладку Board и выберите модель отладочной платы ZedBoard и нажмите Next (рис. 4).  Рис. 4. Окно выбора отладочной платы Проверьте Project summary и нажмите finish. На данном этапе создан пустой проект для платы ZedBoard (рис. 5).  Рис. 5. Окно свойств созданного проекта Добавление design файла в проект Рассмотрите окно среды после создания проекта (рис. 6). Панель Flow navigator – включает в себя полный набор кнопок для создания проекта. Примечательно, что кнопки на данной панели находятся в хронологическом порядке этапов создания, отладки и тестирования на отладочной плате: - 1 – кнопка project manager – открывает окно менеджера проекта и позволяет добавлять, удалять файлы в проект; - 2 – кнопка IP integrator – дает возможно создать блочный проект и добавить; - 3 – Кнопка Simulation – открывает панель симуляции проекта; - 4 - кнопка RTL анализ – генерирует RTL схемотехнику проекта и позволяет просмотреть в виде каких элементов синтезируется проект; - 5 – кнопка Synthesis – содержит под собой элементы запуска синтеза проекта и позволяет получить отчеты по разарбатываемым устройствам; - 6 – кнопка Implementation – запускает размещение синтезированного проекта на логических элементах выбранной микросхемы или отладочной платы;                       Панель flow navigator – панель с основными этапами разработки Панель project manager – управление файлами проекта Вкладка project summary – обобщает всю информацию о проекте 6 5 4 3 2 1 Консольное окно Рис. 6. Окно среды разработки после создания пустого проекта Н  ажмите на кнопку Project Manager, затем на Add Sources. В открывшемся окне выберите Add or create design sources (добавить или создать файл разрабатываемого устройства) и нажмите next. Рис. 7. Окно добавления или создания новых файлов В  открывшемся окне (рис. 7) нажмите Create File Рис. 8. Окно создания файла В открывшемся окне (рис. 8) введите имя файла swled и убедитесь, что языком разработки выбран Verilog. Нажмите OK. На этом этапе создан файл устройства (design source). После успешного создания файла, найдите и кликните на файл swled.v в дереве проекта (примечание: должна быть активна кнопка project manager).  Напишите в протоколе обозначения и запишите их таблицу истинности для логических элементов на рисунке (рис.9). Рис. 9. Условно-графическое обозначение логических элементов  Пример разрабатываемой логики (рис. 10). Рис. 10. Разрабатываемое устройство Разрабатываемое устройство предоставляет собой входную шину in [7:0] из 8 проводов, логических элементов И, ИЛИ, НЕ, И-НЕ и простого провода, и выходную шину out [4:0]. Впишите содержание файла swled.v согласно листингу ниже: module sw_led( //название модуля input wire [7:0] in, //входная 8-битная шина проводов output wire [4:0] out //выходная 5-битная шина проводов ); //присвоение 4 биту шины out логической операции И между in[6] и in[7] assign out[4] = in[6] & in[7]; //присвоение 3 биту шины out логической операции ИЛИ между in[5] и in[4] assign out[3] = in[5]| in[4]; //присвоение 2 биту шины out логического отрицания сигнала in[3] assign out[2] = |