цифровые устройства и микропроцессоры. 1 Назначение psw. Структура

Скачать 6.57 Mb. Скачать 6.57 Mb.

|

|

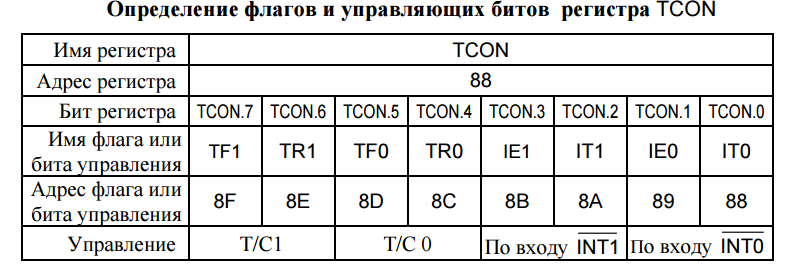

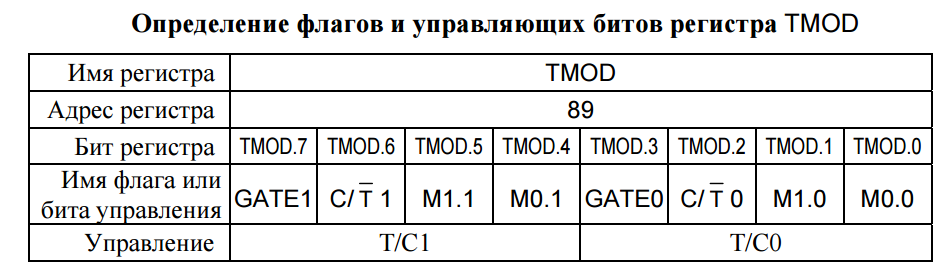

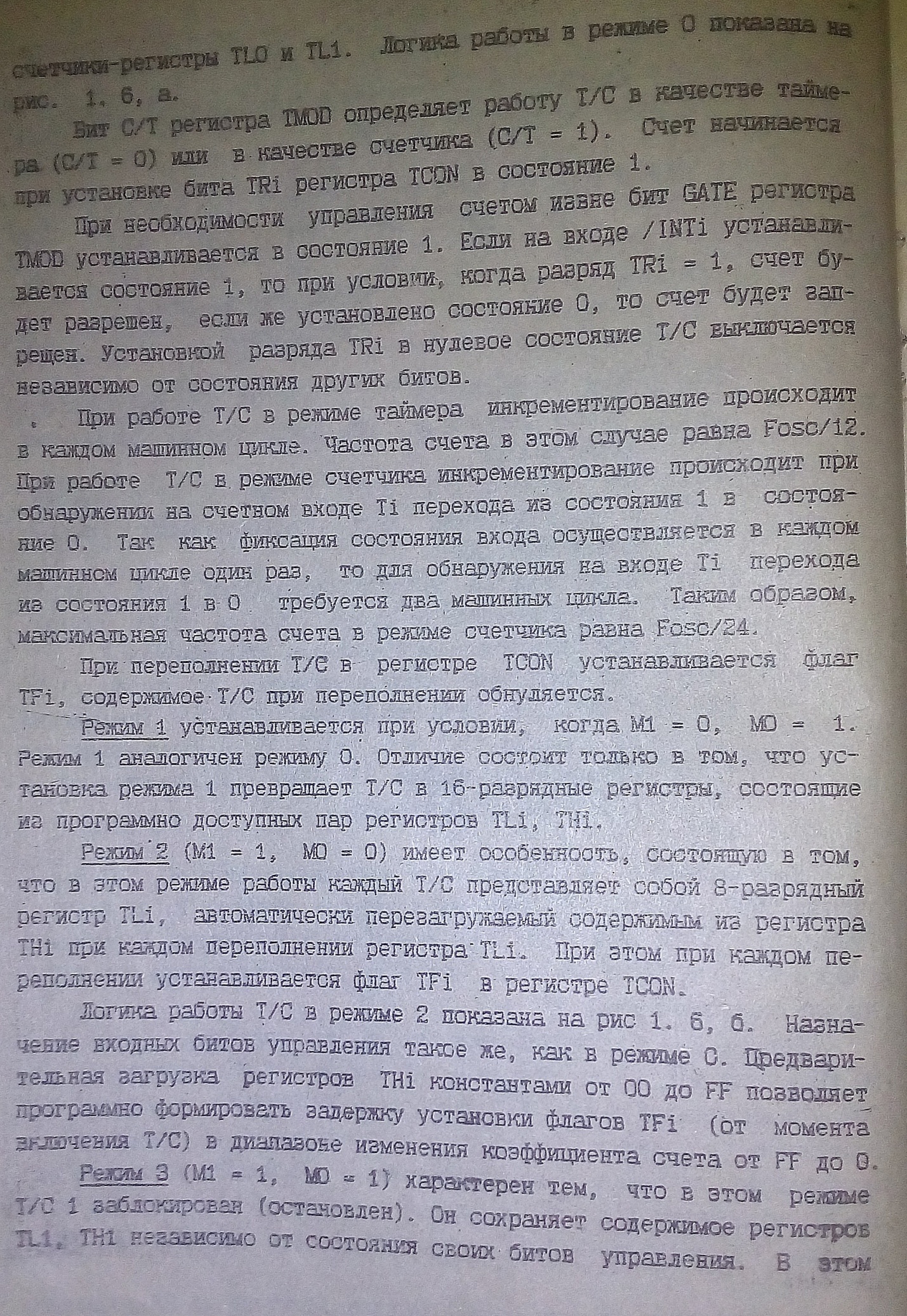

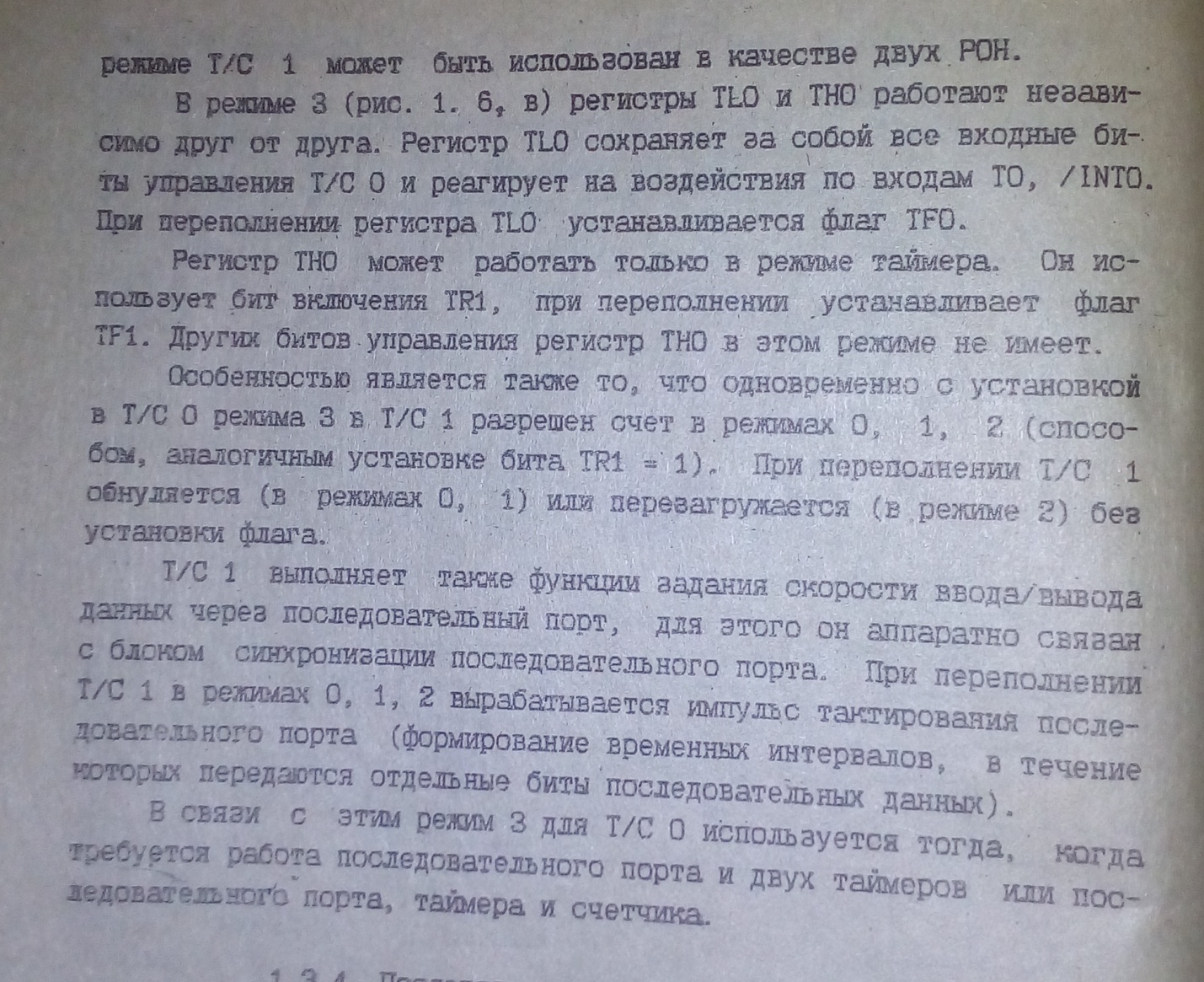

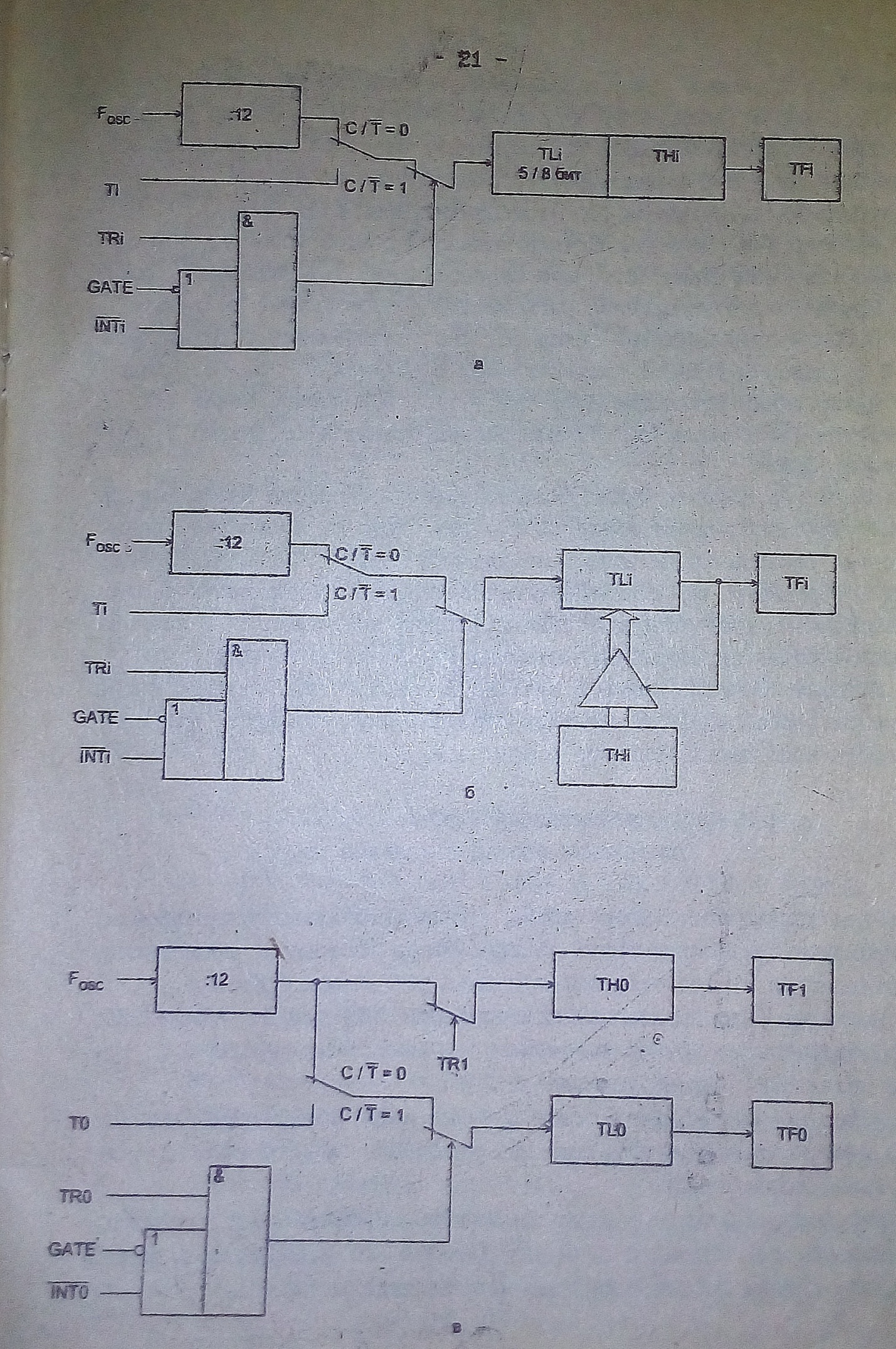

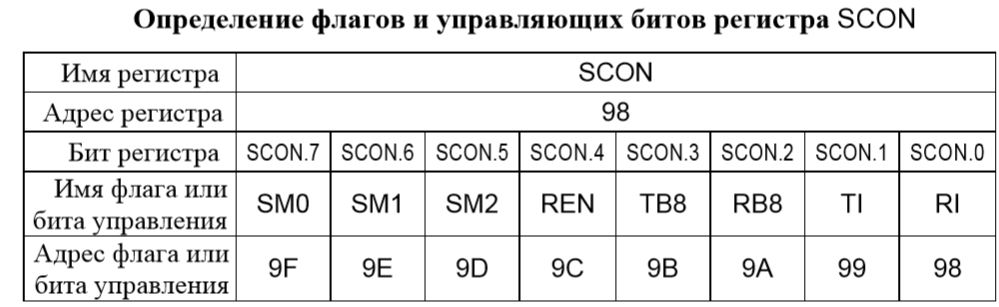

обладает свойством деления втекающих токов в каждом узле схемы на две равных составляющих. Опорный ток Io от источника опорного напряжения V1, равный Io = V1 / R, в первом узле делится на две составляющие 0,5 Io, во втором узле – на составляющие 0,25 Io, в третьем – на составляющие 0,125 Io и т.д. Частичные токи в ветвях матрицы соответствуют весовым значениям двоичных разрядов дробного двоичного числа: 2-1 = 0,5; 2-2 = 0,25; 2-3 = 0,125; ... . Таким образом, собирая частичные токи, соответствующие единичным значениям входного двоичного числа в одну ветвь, получаем результирующий ток, пропорциональный числовому значению входного цифрового кода. В ЦАП с матрицей резисторов R-2R выходной аналоговой величиной является ток (токовый ЦАП). Схема макета для изучения 3-разрядного ЦАП с матрицей резисторов R-2R представлена на рис. 2. В качестве коммутаторов тока в схеме используются аналоговые ключи АКа и АКb, реализованные по схеме рис.3.  Рис.3 Аналоговый ключ (АК) построен на полевых транзисторах с индуцированным каналом Т1 (n-канальный) и Т2 (p-канальный), включенных параллельно для уменьшения сопротивления ключа (между выводами Pin1 и Pin2) в состоянии проводимости. Входом управления состоянием АК является вывод Pin3. Транзисторы Т1 и Т2 либо одновременно открыты (при высоком логическом уровне на линии Pin3), либо одновременно закрыты (при низком логическом уровне). В схеме ЦАП (рис.2) состояниями ключей АК управляют отдельные биты входного цифрового кода (а2, а1, а0). Ключ АКа замкнут, если соответствующий бит входного кода равен единице, при нулевом бите – разомкнут. Выходной ток Iвых а является, таким образом, суммой частичных токов, соответствующих единичным битам входного двоичного числа. Ключи АКb управляются через инверторы, следовательно, они замкнуты, если соответствующие биты входного кода равны нулю, при единичных битах – разомкнуты. Выходной ток Iвых b является суммой частичных токов, соответствующих нулевым битам входного двоичного числа. Входной код для ЦАП формирует генератор входного цифрового кода. Буферы U5, U6, U7 к схеме ЦАП не относятся, они введены для удобства отображения результатов работы схемы. Преобразование выходных токов в выходные аналоговые напряжения осуществляется с помощью низкоомных резисторов R7, R8. 18)т\с Таймеры/счётчики. Управление таймерами/счётчиками В состав внутренних функциональных узлов МК КР1830ВЕ31 вхо- дят два идентичных 16-разрядных таймера/счётчика (Т/С), которые могут быть запрограммированы для работы либо в качестве таймера, либо в качест- ве счётчика. Функция таймера состоит в счёте внутренних машинных циклов, следующих с частотой FOSC/12. Машинный цикл имеет фиксированную дли- тельность, равную 12 периодам тактового генератора (кварцевого резонато- ра). Функция счётчика заключается в подсчёте внешних событий, которые сопровождаются формированием импульсов на входах Т0 и Т1. Т/С в режиме счёта внешних событий считают переходы из 1 в 0 на соответствующих вхо- дах. Каждый Т/С состоит из двух 8-разрядных регистров-счетчиков, ко- торые можно рассматривать как универсальные последовательностные уст- ройства, способные выполнять микрооперации параллельной записи (загруз- ки), параллельного чтения (выгрузки), микрооперации счёта. Обращение к Т/С осуществляется по адресам составляющих их регистров: TL0 (адрес 8A), TH0 (адрес 8C), TL1(адрес 8B), TH1 (адрес 8D). 8-разрядные регистры-счётчики, составляющие каждый Т/С, могут объединяться в единые 16-, 13-разрядные счётчики или работать независимо, взаимодействуя между собой для обеспечения предусмотренных пользовате- лем режимов работы. Регистры-счётчики работают только в режиме сумми- рования. При переполнении (при переходе из состояния “все 1”в состояние “все 0”) устанавливается соответствующий флаг переполнения. Управление Т/С осуществляется через 8-разрядные управляющие регистры TCON (адрес 88) и TMOD (адрес 89)  Описание флагов и управляющих битов в составе регистра TCON: TF1 (TF0) – флаг переполнения Т/С1 (Т/С0), который может запрашивать прерывание; при подтверждении пре- рывания сбрасывается. TR1 (TR0) – бит включения (запуска) Т/С1 (Т/С0); TR = 1 – Т/С включен, TR = 0 – выключен; бит устанавливается и сбрасывается из программы. IE1 (IE0) – флаг, устанавливающийся при наличии запроса прерывания по входу INT1 (INT0 ); при подтверждении прерывания сбрасывается. IT1 (IT0) – бит управления типом прерывания по входу INT1 (INT0 ); IT = 1 – прерывание по переходу из 1 в 0, IT = 0 – прерывание по статическому уровню 0; бит устанавливается и сбрасывается из программы.  Описание флагов и управляющих битов в составе регистра TMOD: M1, M0 – двухразрядный код, определяющий номер рабоче- го режима (00, 01, 10, 11) Т/С; задается из про- граммы. C/ T – бит управления функцией Т/С: C/ T = 0 – таймер, на входе которого - импульсы с частотой FOSC/12 от внутреннего источника сигналов синхрониза- ции; C/ T = 1 – счетчик событий на внешнем входе T; устанавливается из программы. GATE – бит, разрешающий блокировку Т/С сигналом на внешнем выводе INT ; GATE = 1 – блокировка раз- решена: сигнал INT = 0 или вызывает останов ра- ботающего Т/С, или запрещает (блокирует) запуск Т/С из программы; GATE = 0 – блокировка запре- щена; устанавливается из программы.     19)Команды арифметические и и логические. Назначение, классификация, содержание. Группа команд арифметических операций (таблица П2.2) со- держит команды сложения ADD, сложения с учетом переноса ADDC, вычитания с учетом заема SUBB, увеличения и уменьшения на единицу INC и DEC, десятичной коррекции сложения в двоично-десятичном (BCD) коде упакованного формата, умножения MUL и деления DIV. Операции выполняются над беззнаковыми целыми числами. В опера- циях сложения и вычитания первым операндом и приемником резуль- тата служит аккумулятор. Для определения второго операнда исполь- зуется прямая регистровая, прямая абсолютная, непосредственная и косвенная адресации. Операции INC и DEC применимы к аккумулятору, прямо адресуемому регистру, прямо или косвенно адресуемой ячейке памяти. Кроме того, операция INC применима к содержимому 16- разрядного регистра указателя DPTR. В операциях целочисленного умножения и деления без знака уча- ствуют аккумулятор и регистр B. При умножении 8-разрядное значение A умножается на 8-разрядное значение B, а 16-разрядный результат записывается в пару BA. При этом регистр B хранит старшую часть произведения. Флажок OV устанавливается, если произведение боль- ше 255. При делении 8-разрядного значения A на 8-разрядное значение B частное записывается в A, а остаток в B. При попытке деления на 0 устанавливается флаг переполнения OV. Команда десятичной коррекции аккумулятора DA размещается после команды сложения. Слагаемые необходимо представить в BCD коде. Коррекция выполняется стандартным способом. Группа команд логических операций (таблица П2.3) содержит три типовые операции: ANL – логическое И, ORL – логическое ИЛИ, XRL – логическое исключающее ИЛИ. Источником первого операнда44 служит либо аккумулятор A, либо прямо адресуемая ячейка памяти. Второй операнд задается одним из четырех основных методов адреса- ции. В состав группы входят также одноместные операции над содер- жимым аккумулятора: CLR - очистки, CPL – инверсии, а также RL, RLC, RR и RRC – операции циклического и расширенного сдвигов вправо и влево. Сюда же включена операция обмена тетрад в аккумуляторе SWAP,которая может интерпретироваться как циклический сдвиг байта на четыре разряда. 20)Режим работы последовательного порта SCON Управление последовательным портом осуществляется через 8-разрядный управляющий регистр SCON (адрес 98).  Описание флагов и управляющих битов в составе регистра SCON: SM0, SM1 – двухразрядный код, определяющий номер рабочего режима (00, 01, 10, 11) последовательного порта (задается из программы): 00 – режим 0, синхронный последовательный ввод/вывод со скоростью FOSC/12; 01 – режим 1, асинхронный ввод или вывод с переменной скоростью и с 10-битовым кадром (старт-бит, 8 бит последовательных данных D0,…,D7, стоп-бит); 10 – режим 2, асинхронный ввод или вывод с фиксированной скоростью FOSC/32 или FOSC/64 и с 11-битовым кадром (старт-бит, 8 бит последовательных данных D0,…,D7, служебный бит D8, стоп-бит); 11 – режим 3, асинхронный ввод или вывод с переменной скоростью и с 11-битовым кадром (старт-бит, 8 бит последовательных данных D0,…,D7, служебный бит D8, стоп-бит). SM2 – бит запрета приема кадров с нулевым восьмым битом (D8 = 0); устанавливается и сбрасывается из программы; в режиме 1 должен быть установлен; в режиме 0 – сброшен. REN – бит разрешения приёма последовательных данных; устанавливается и сбрасывается из программы. TB8 – восьмой бит (D8) передатчика в режимах 2 и 3; устанавливается и сбрасывается из программы для задания подлежащего передаче значения служебного бита в кадре (признак информации, передаваемой в кадре). RB8 – восьмой бит (D8) приёмника в режимах 2 и 3; копия значения служебного бита D8 в принятом кадре (признака информации, принятой в кадре); в режиме 1 – записывается стоп-бит; в режиме 0 – не используется и должен быть равен 0; фиксируется аппаратными средствами приёмника. TI – флаг прерывания от передатчика; устанавливается аппаратно по окончании передачи кадра, сбрасывается из программы после обработки прерывания. RI – флаг прерывания от приемника; устанавливается аппаратно по окончании приёма кадра; сбрасывается из программы после обработки прерывания. Режим 0. Последовательный порт МК работает как 8-разрядный регистр сдвига. Данные последовательно передаются (передатчиком) или принимаются (приёмником) путём их сдвига через общую линию RxD младшими битами вперёд, по 8 разрядов за одну операцию обмена. Для синхронизации устройств, участвующих в обмене (регистров сдвига), передатчик формирует импульсы сдвига с частотой FOSC/12 и выдает их на общую линию TxD. Передача последовательных данных инициируется всякий раз, когда новый байт записывается в SBUF. Признаком окончания передачи служит установка флага TI. Приём данных активизируется (при разрешенном приёме последовательных данных – REN = 1) путём сброса флага RI. Снова установленный флаг указывает на готовность новых (введённых) данных, которые можно считывать из SBUF. Режим 1. Передача инициируется любой командой, для которой получателем байта является SBUF. Время передачи каждого бита последовательных данных равно 16 тактам специального счётчика (счётчика битинтервалов), пересчитывающего импульсы переполнения таймера/счётчика Т/С1. Частота переполнения Т/С1 определяет скорость выдачи последовательных данных передатчиком. Приём последовательных данных начинается с момента обнаружения перехода сигнала на входе RxD из состояния 1 в состояние 0 и включения счётчика бит-интервалов для приёмника. В середине каждого битинтервала производится опрос сигнала на входе RxD и принимаются решения о значении каждого последовательного бита. Принятые биты сдвигаются в регистр приёмника, затем запоминаются в SBUF – после чего устанавливается флаг RI. После окончания приема кадра устройство управления приёмом вновь начинает отыскивать переход 1 – 0 на входе RxD. Режим 2. Скорость передачи в режиме 2 постоянная, но зависит от значения флага SMOD в регистре PCON и может быть равна либо FOSC/32 (SMOD = 0), либо FOSC/64 (SMOD = 1). Режим 3 . Скорость передачи переменная и определяется частотой переполнения таймера/счётчика Т/С, но может понижаться в 2 раза при значении флага SMOD = 0 в регистре PCON. При SMOD = 1 скорость передачи совпадает с частотой переполнения. Флаги приёмника RI и передатчика TI могут использоваться для запроса прерывания. В режимах 1, 2, 3 при значении флага SM2 = 1 установка флага RI и генерация запроса от него на прерывание возможны лишь при приёме кадра с D8 = 1. Для режима 1 это означает контроль кадра на наличие стоп-бита. Для режимов 2 и 3 такая работа обеспечивает выделение кадров одного класса, в которых D8 = 1. Кадры, в которых D8 = 0, в SBUF не записываются и теряются. Возможность реагировать только на кадры с RB8 = D8 = 1 или принимать любые кадры при SM2 = 0 может использоваться при построении управляющей системы из нескольких МК, объединённых в единую сеть на основе использования последовательной передачи данных. 21)Классификация команд 23)Параллельный АЦП Схема макета для изучения параллельного АЦП представлена на рис.1. Основа схемы – аналоговые компараторы. Аналоговый компаратор (АК) – аналого-цифровая схема, имеющая два аналоговых входа (неинвертирующий – U+ , и инвертирующий – U–) и один цифровой выход. Цифровой сигнал на выходе произвольного компаратора АКi имеет высокий уровень ("1"), если U+i ≥ U–i , и низкий уровень ("0") – при U+i < U–i . В схеме макета параллельного АЦП входное  Рис. 1 напряжение Uin задаётся источником напряжения V1, которое можно изменять (в реальных АЦП постоянное на интервале дискретизации входное напряжение поступает из схемы выборки и хранения – СВХ). Входное напряжение Uin подаётся одновременно (параллельно) на неинвертирующие входы всех компараторов. А на инвертирующих входах АК все напряжения – разные; они задаются резистивным делителем, подключенным к источнику опорного напряжения Uref. Минимальное напряжение на инвертирующем входе АК0 равно u0 = 0,5δ – половине шага квантования δ = Uref / (2k – 1) и определяет порог переключения АК0. Порог переключения для АК1 равен u1 = 0,5δ + δ = 1,5δ; для АК2 – u2 = 2,5δ ; и т.д. ; для АК6 – u6 = 6,5δ. Таким образом, если входное напряжение Uin = 0, на выходах компараторов d0 ... d6 – все нули (0); при Uin = Uref – все единицы (1). При промежуточных значениях Uin: на выходах нижних компараторов – 1, на выходах верхних – 0, такой код d0d1d2d3d4d5d6 на выходах компараторов является "термометрическим кодом". Величину входного напряжения Uin (его числовое значение) определяет адрес верхней единицы в термометрическом коде (номер верхнего компаратора с единицей на выходе). Преобразование термометрического кода d0d1d2d3d4d5d6 в натуральный двоичный код А2А1А0 выполняет приоритетный шифратор (PRCD) – комбинационная схема, формирующая адрес старшего входа из всех входов схемы, на которые поданы единицы. |