цифровые устройства и микропроцессоры. 1 Назначение psw. Структура

Скачать 6.57 Mb. Скачать 6.57 Mb.

|

|

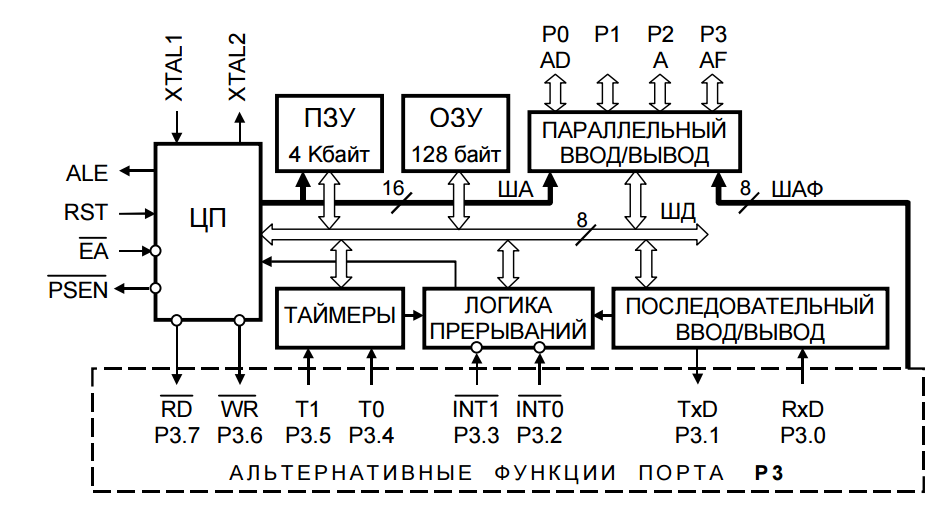

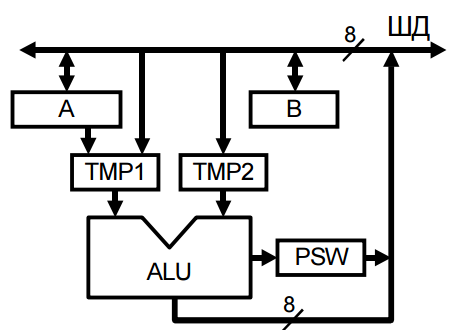

Переход к выполнению подпрограммы обслуживания прерывания задерживается при наличии следующих условий: 1) производится обработка прерывания с таким же или с высшим уровнем приоритета; 2) текущий машинный цикл не является последним циклом команды; 3) выполняется команда RETI текущей подпрограммы или любая команда обращения к регистрам IE, IP. Подпрограмма обслуживания прерывания продолжается до исполнения команды RETI, по которой восстанавливается состояние программного счётчика из двух верхних ячеек стека. Если же использована команда RET для возврата из подпрограммы обработки прерывания, состояние программного счётчика также восстанавливается, но считается, что обслуживание прерывания продолжается и новые прерывания становятся невозможными. 6)Структура МПС с мультиплексированной ШД(3х шинная) Базовая конфигурация микроконтроллера представлена на рис. 2. Она содержит общие для всего семейства MCS-51 периферийные уст- ройства. В состав микроконтроллера входят: 8-разрядный центральный процессор ЦП; два 16-разрядных таймера/счетчика; система двухуров- невого прерывания; последовательный порт ввода/вывода; четыре 8-разрядных параллельных порта, у которых каждую из 32 линий можно настроить на ввод или вывод, а 24 линии могут выполнять альтерна- тивные функции. Внутренние ПЗУ программ IROM и ОЗУ данных IRAM имеют минимальный объем 4 Кбайта и 128 байт соответственно. Базо- вая конфигурация содержит встроенные средства расширения своих ресурсов, позволяющие реализовать вне кристалла память программ EROM и память данных ERAM до 64 Кбайт каждая. Все расположенные на кристалле устройства подключены к внутренней мультиплексиро- ванной шине данных ШД. В любой момент к шине может быть подклю- чен только один источник данных. Для этого выходы всех источников должны иметь третье состояние. Число подключаемых приемников ог- раничено нагрузочной способностью шины. Для сокращения ширины физического интерфейса (числа контак-тов ИС) линии параллельного порта выполняют альтернативные функ- ции. При обращении к внешней памяти порт P0 выполняет функции со- вмещенной шины адреса/данных (AD), а P2 – шины старшего байта ад- реса (A). Все линии порта P3 выполняют альтернативные функции управления и специального ввода/вывода (AF).  Ядром микроконтроллера является центральный процессор. Он выполняет две основные функции: управление процессом преобразо- вания (обработки) данных каждой командой и выполнение этого преоб- разования (обработки). Первую функцию решает блок управления, в состав которого входят: устройство управления и синхронизации, гене- ратор тактовых импульсов, регистр команд и устройство формирования адреса; вторую - операционное устройство (рис. 3). Центральный процессор соединен встроенной системной магист- ралью (16-разрядная шина адреса ША, 8-разрядная шина данных ШД и шина управления ШУ), физически совмещенной с портами Р0, Р2 и Р3 с памятью и всеми периферийными устройствами (рис. 2). Считанный из па- мяти программ код команды по шине данных ШД записывается в ре- гистр команд. Устройство управления и синхронизации дешифрирует команду и выдает по шине управления ШУ сигналы управления всеми внутренними устройствами микроконтроллера, а также управление внешними устройствами .Операционное устройство выбирает операнды, выполня- ет заданную коман- дой операцию над операндами и выда- ет результат опера- ции на шину данных ШД и признаки (флаги) результата на выделенные линии ШУ. Внешний сигнал рестарта RST (Restart) производит сброс микро- контроллера в исходное состояние, а сигнал EA __ (External Access) Операционное устройство выполнено по классической схеме и служит для обработки 8-разрядных данных (рис. 4). Оно содержит арифметико-логическое устройство ALU, аккумулятор A, два программ- но-недоступных регистра временного хранения TMP1 и TMP2, регистр слова состояния программы PSW (Program Status Word) и регистр B. В ALU выполняется операция над двумя операндами, находящи- мися в регистрах временного хранения TMP1 и TMP2. При выполнении операций данные интерпретиру- ются как целые числа без знака. Результат операции выдается на внутреннюю шину данных ШД, а во многих командах он также за- писывается в аккумулятор A. В командах умножения и деления роль источника и приемника ин- формации выполняют регистры A и B. При выполнении арифмети- ческих и логических операций в ALU вырабатываются признаки результата, которые записыва- ются в регистр PSW. Все биты регистра PSW, расположенного в облас- ти BSEG регистров специальных функций SFR, программно-доступны. Их можно устанавливать исбрасывать командами программы.  9)Способы выполнения арифметических команд Группа команд арифметических операций (таблица П2.2) со- держит команды сложения ADD, сложения с учетом переноса ADDC, вычитания с учетом заема SUBB, увеличения и уменьшения на единицу INC и DEC, десятичной коррекции сложения в двоично-десятичном (BCD) коде упакованного формата, умножения MUL и деления DIV. Операции выполняются над беззнаковыми целыми числами. В опера- циях сложения и вычитания первым операндом и приемником резуль- тата служит аккумулятор. Для определения второго операнда исполь- зуется прямая регистровая, прямая абсолютная, непосредственная и косвенная адресации. Операции INC и DEC применимы к аккумулятору, прямо адресуемому регистру, прямо или косвенно адресуемой ячейке памяти. Кроме того, операция INC применима к содержимому 16- разрядного регистра указателя DPTR. В операциях целочисленного умножения и деления без знака уча- ствуют аккумулятор и регистр B. При умножении 8-разрядное значение A умножается на 8-разрядное значение B, а 16-разрядный результат записывается в пару BA. При этом регистр B хранит старшую часть произведения. Флажок OV устанавливается, если произведение боль- ше 255. При делении 8-разрядного значения A на 8-разрядное значение B частное записывается в A, а остаток в B. При попытке деления на 0 устанавливается флаг переполнения OV. Команда десятичной коррекции аккумулятора DA размещается после команды сложения. Слагаемые необходимо представить в BCD коде. Коррекция выполняется стандартным способом. 11)АЦП последовательных приближений Схема макета для изучения АЦП последовательного приближения представлена на рис.2. В состав схемы входят: выходной регистр, состоящий из SR-триггеров; цифро-аналоговый преобразователь (R-2R); регистр сдвига на D-триггерах; входной SR-триггер формирования пачки импульсов сдвига С; тактовый генератор импульсов V1; генератор импульсов пуска преобразования V2; комбинационная схема (логические элементы И, ИЛИ) для управления регистрами (сдвигом и сбросом) и аналоговый компаратор. В отличие от параллельного АЦП в данной схеме используется один аналоговый компаратор, который выполняет сравнение двух  напряжений: входного Uin, поступающего на инвертирующий вход, и напряжения Uda на неинвертирующем входе с выхода ЦАП. Сигнал Z c выхода аналогового компаратора используется для управления сбросом триггеров выходного регистра. Если Uda > Uin, Z = 1 – происходит сброс одного из выходных триггеров (выбранного регистром сдвига). Пуск АЦП последовательного приближения осуществляется импульсом Start (логическая единица). При воздействии импульса Start все выходные триггеры обнуляются; в триггер X3s (в триггер set, установки) по входу S записывается логическая 1 (при этом выходной триггер старшего разряда X3 устанавливается в состояние D3 = 1); в остальные выходные триггеры по входам R записывается логический 0. На вход ЦАП в результате поступает код 1000 и на выходе ЦАП формируется напряжение Uda = Uref / 2, соответствующее весу старшей единицы кода 1000 на его входе. Импульс Start вместе с изложенным устанавливает входной SR-триггер X4 (ранее сброшенный в 0), в состояние 1, что разрешает поступление тактовых импульсов с генератора V1 на линию С для сдвига кода в регистре сдвига. Первый тактовый импульс на линии импульсов сдвига С сдвигает единицу из триггера X3s в триггер X3r (в триггер reset, триггер сброса). Единица сброса с выхода триггера X3r попадает на вход сброса R триггера X3 при Z = 1, при Uda < Uin (вход R не заблокирован сигналом Z), или не попадает, если вход R заблокирован сигналом Z = 0 (при Uda > Uin). Таким образом, после первого тактового импульса единица в старшем разряде выходного кода D3 =1 либо подтверждается (сохраняется), либо не подтверждается (сбрасывается). Произошло первое грубое "взвешивание" входного напряжения Uin посредством использования в качестве "гири" напряжения Uda = Uref / 2, соответствующее весу старшей единицы выходного кода АЦП. Получено первое приближение кода на выходе АЦП. Второй тактовый импульс сдвигает единицу в триггер X2s, устанавливается триггер X2 (D2 = 1), который затем после третьего тактового импульса либо сбрасывается единицей с выхода X2r, либо нет. Получается второе приближение выходного кода АЦП при использовании напряжения Uref / 4, равное весу единицы разряда D2. Аналогично получаются значения разрядов D1, D0 в выходном коде с использованием напряжений Uref / 8, Uref / 16, соответствующих их весовым значениям. Получением разряда D0 процесс формирования выходного кода заканчивается. Конец аналого-цифрового преобразования фиксируется сдвигом единицы в триггер XFin, который хранит бит-признак процесса преобразования Fin: Fin = 0 – преобразование продолжается; Fin = 1 – преобразование закончено. Длительность преобразования напряжения в код в АЦП последовательных приближений, рис.2, составляет 8 периодов тактовых импульсов генератора V1. Разрядность выходного кода (точность преобразования) могут быть увеличены путём увеличения разрядности выходного регистра, регистра сдвига, ЦАП; при этом, соответственно, увеличивается время преобразования. Анализ работы схемы рис.2 показывает, что эксплуатационные параметры и характеристики преобразования АЦП последовательных приближений определяется, в основном, соответствующими характеристиками ЦАП, входящего в его структуру. 12)Особенности выполнения команд перехода Группа команд передачи управления (таблицы П2.4 и П2.5) со- держит команды безусловного перехода AJMP, LJMP, SJMP, JMP, ус- ловного перехода JZ, JNZ, CJNE, вызова ACALL, LCALL, возврата RET, RETI и модификации с условным переходом DJNZ. Сюда же включена пустая команда NOP. В командах передачи управления широко применяется относи- тельная адресация, позволяющая создавать перемещаемые программ- ные модули. В качестве относительного адреса выступает 8-разрядное смещение rel – байт со знаком, обеспечивающее переход на (–128… +127) байт относительно текущего положения PC. Для перехода в лю- бую другую точку 64 Кбайтового адресного пространства может быть использован либо прямой addr16, либо косвенный @A+DPTR адрес. В последнем случае содержимое A интерпретируется как целое без зна- ка. Вариант короткой прямой адресации addr11 внутри 2 Кбайтовой те- кущей страницы введен для совместимости с семейством MCS-48. Все эти типы адресации применяются в командах перехода. В ко- мандах вызова используются только прямой addr16 и внутристранич- ный addr11 способы адресации. Во всех условных командах использу- ется только относительная адресация. Когда микроконтроллер опознает запрос на прерывание, он гене- рирует команду LCALL addr16, что автоматически обеспечивает запо- минание адреса возврата в стеке. Информация о состоянии программы (содержимое регистра PSW) автоматически не сохраняется. При этом45 логика прерываний запоминает уровень приоритета обслуживаемого прерывания. При выполнении команды RET уровень приоритета сохра- няется и следующим может быть обслужено только прерывание с бо- лее высоким уровнем приоритета. Команда RETI отличается от коман- ды RET тем, что она сбрасывает уровень приоритета, что позволяет обслуживать запросы на прерывания с низким уровнем приоритета. К типовым условным операциям относятся команды JZ и JNZ, JC и JNC. Две последних включены в группу «булевых». В команде CJNE сначала сравниваются, по правилам вычитания целых чисел, два байта и в соответствии с результатом сравнения устанавливается флаг C. За- тем, в случае их несовпадения, выполняется ветвление. В команде DJNZ в качестве счетчика может использоваться не только один из регистров текущего регистрового банка Rn, n=0...7, но и прямо адресуемая ячейка памяти данных DSEG. При исполнении ко- манды сначала выполняется декремент счетчика и, если содержимое счетчика не равно нулю, ветвление. 13)Минимальная конфигурация МК51 Минимальный состав МП-системы на базе МК КР1830ВЕ31 и БИС КР1821РФ55, КР1821РУ55 ограничен линией на рис.1. Шины портов и сиг- нальные линии, выходящие за границу, обеспечивают взаимодействие МП- системы с внешней средой. В схеме рис.1 для выбора РФ55, РУ55 и внутренних узлов в их со- ставе для взаимодействия с МК используются свободные линии шины адреса А11…А15 (линии P2.3…P2.7 порта P2, через который выводит- ся старший байт адреса), что позволяет обойтись без применения дешифра- тора. Адресная линия P2.6 (А14) используется для выбора БИС РУ55 по линии CS; P2.5 (А13) – для выбора по линии IO/M внутреннего регистра, пор- та, таймера или ячейки ОЗУ в БИС РУ55; P2.4 (А12) – для выбора БИС РФ55 по линии CS2; P2.3 (А11) – для выбора по линии IO/M внутреннего регистра, порта или ячейки ПЗУ в БИС РФ55. В состав БИС РФ55 входит ПЗУ емкостью 2К х 8 бит и два 8- разрядных порта ввода – вывода. Каждая линия обоих портов может про- граммироваться индивидуально и определяться как входная или выходная. Порты могут работать только в режиме простого обмена без каких-либо со- провождающих сигналов, причем выводимый байт запоминается в буферном регистре порта, а вводимый – не запоминается. В состав БИС РУ55 входит статическое ОЗУ емкостью 256 х 8 бит, два 8-разрядных (PА и PВ) и один 6-разрядный (PС) порты ввода-вывода и 14-разрядный программируемый счетчик/таймер. Все разряды портов PА и PВ используются для ввода-вывода па- раллельно, т.е. невозможна установка направления передачи индивидуально для каждого разряда. Порты PА и PВ содержат буферные регистры для запо- минания пересылаемого байта данных Режимы обмена через порты РФ55 и РУ55 Порты РА и РВ РФ55 работают только в режиме простого обмена – без квитирования. Порты РА и РВ РУ55 могут выполнять условный ввод или вывод с квитированием. Обмен служебными сигналами в таком случае осуществляет- ся по линиям порта РС. Протокол обмена реализуется на аппаратном уровне. Процедура условного обмена на примере ввода и вывода данных через порт РА реализуется следующим образом. При вводе в МК через порт РА внешнее устройство выдает байт данных на линии РА0 – РА7 и вырабатывает строб STB A , по которому этот байт загружается в буферный регистр порта. При этом устанавливается сиг- нал BF А = 1 (следующий байт в порт записывать нельзя). По окончании24 строба STB A устанавливается сигнал запроса прерывания INTR A для опо- вещения МК о необходимости чтения байта из порта. Сигналы BF A и INTRA остаются активными до выполнения МК команды чтения, по кото- рой содержимое буферного регистра порта РА вводится в МК по стробу RD. С началом импульса RD сбрасывается сигнал INTR A , а с его окончанием – сигнал BF А. В рассмотренном цикле условного ввода служебные сигналы STB A и BF А являются сигналами готовности байта ( STB A = 0) и подтверждения (квитирования) приёма байта (BF А = 0). При выводе данных через порт PA МК вырабатывает строб записи WR = 0. По отрицательному фронту этого импульса сбрасывается сигнал INTR А (INTR А = 0). По положительному фронту импульса WR байт данных с шины данных записывается в буферный регистр порта, и устанавливается сигнал BF A = 1 (готов байт для внешнего устройства). Внешнее устройство вырабатывает строб STB A , считывающий байт из порта и являющийся сиг- налом квитирования (подтверждения приёма байта). Сигнал BF A сбрасыва- ется (по отрицательному фронту строба STB A ), а по положительному фронту импульса STB A устанавливается сигнал INTR А= 1 для прерыва- ния работы МК с целью организации цикла вывода очередного байта дан- ных. Режим условного обмена с квитированием можно также реализовать программным способом. Информацию о наличии сигнала прерывания, о со- стоянии буферного регистра и о других управляющих сигналах МК может получить путем чтения слова состояния из РСС и анализа его содержимого. 14)ЦАП с R-2R Матрица резисторов с номиналами R и 2R (рис.2) может иметь необходимую длину в соответствии с разрядностью ЦАП и  |