цифровые устройства и микропроцессоры. 1 Назначение psw. Структура

Скачать 6.57 Mb. Скачать 6.57 Mb.

|

|

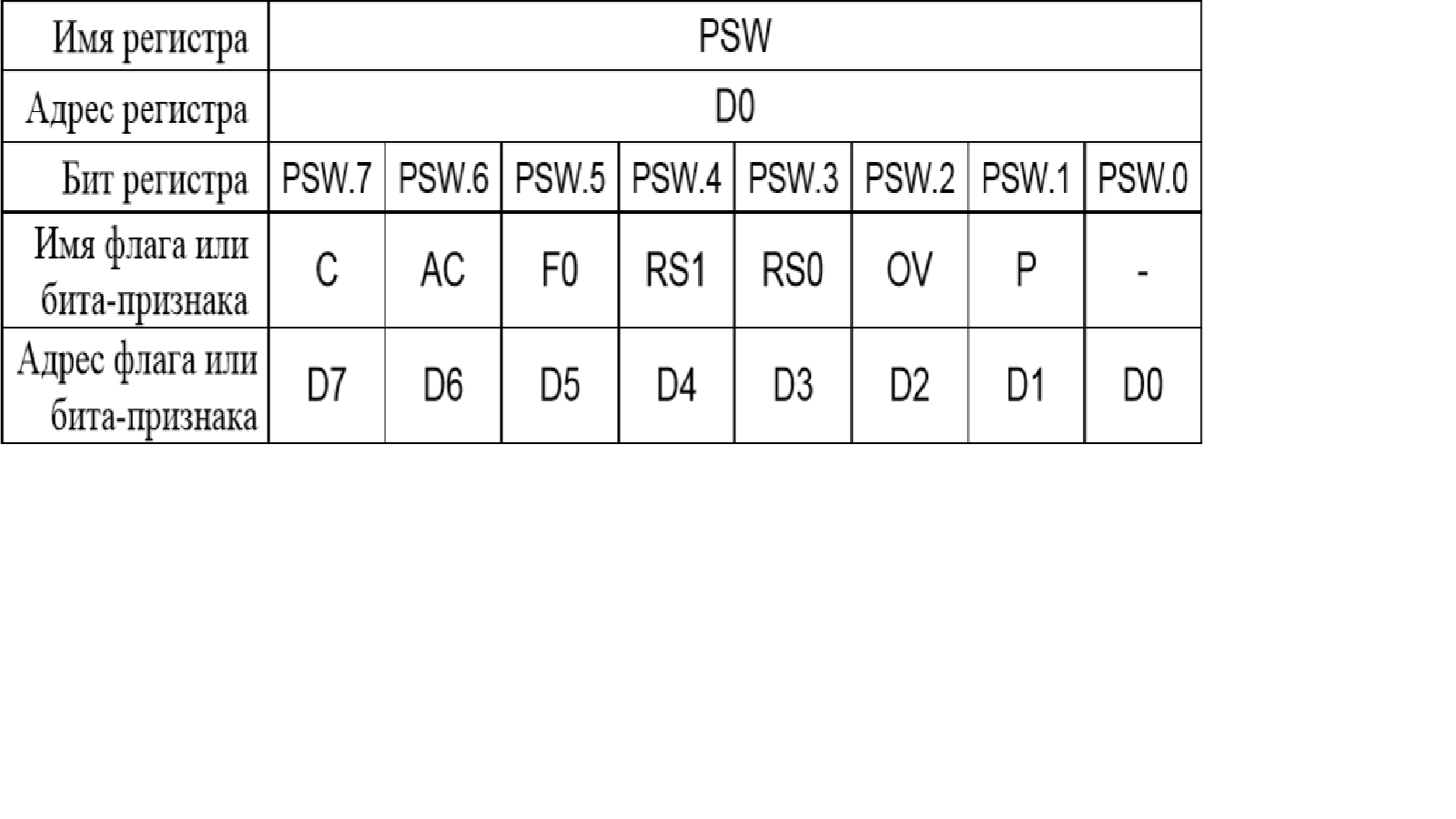

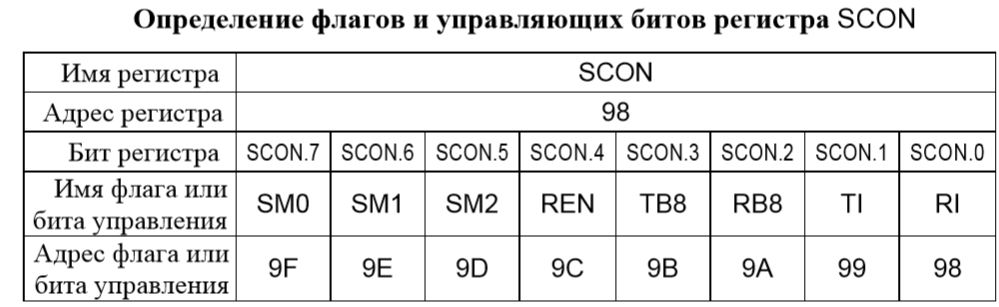

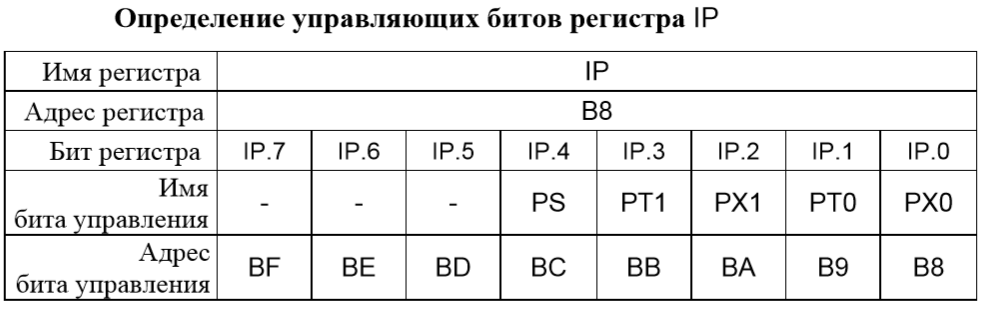

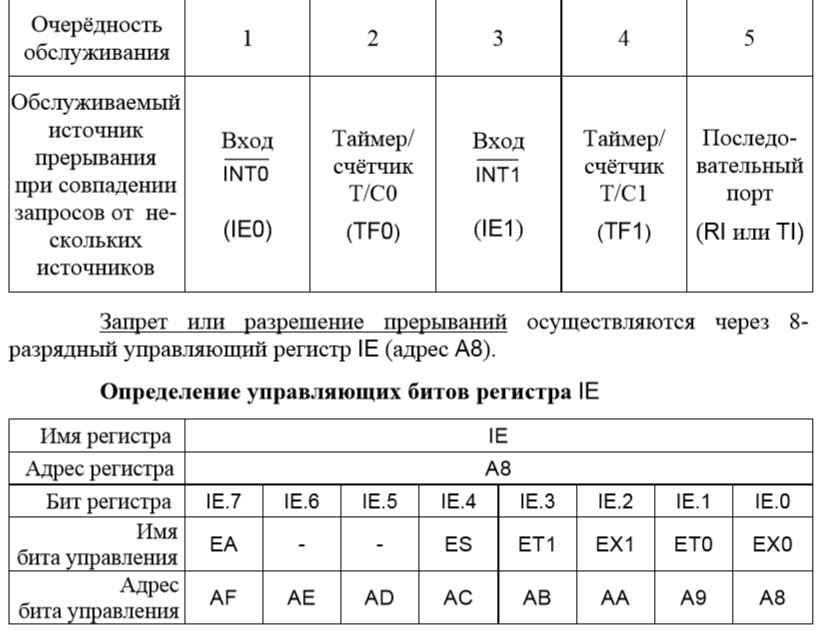

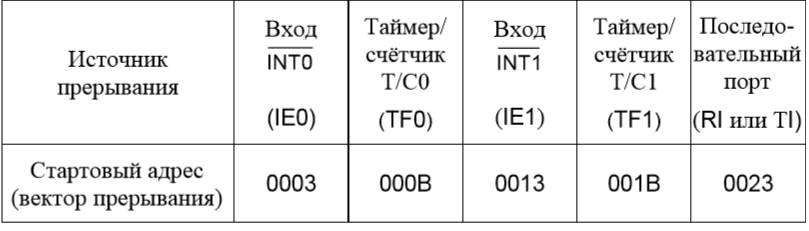

1)Назначение PSW. Структура Определение признаков и флагов регистра PSW PSW – регистр процессора МК, предназначен для фиксирования состояния процессора: значений признаков выполнения арифметических и логических операций в АЛУ, флагов режимов работы.  Описание флагов и признаков в составе регистра PSW: C – бит-признак переноса (C = 1) из старшего разряда АЛУ. AC – бит-признак дополнительного переноса (AC = 1) из младшей тетрады АЛУ в старшую. F0 – флаг общего назначения для пользователя RS1, RS0 – двухразрядный номер используемого (текущего) банка рабочих регистров. OV – бит-признак переполнения (OV = 1) при выполнении арифметической операции. P – бит дополнения аккумулятора до четности (девятиразрядное слово, составленное из содержимого аккумулятора и бита P, всегда содержит четное число единиц). Описание флагов и признаков в составе регистра PSW: C – бит-признак переноса (C = 1) из старшего разряда АЛУ. AC – бит-признак дополнительного переноса (AC = 1) из младшей тетрады АЛУ в старшую. F0 – флаг общего назначения для пользователя RS1, RS0 – двухразрядный номер используемого (текущего) банка рабочих регистров. OV – бит-признак переполнения (OV = 1) при выполнении арифметической операции. P – бит дополнения аккумулятора до четности (девятиразрядное слово, составленное из содержимого аккумулятора и бита P, всегда содержит четное число единиц). 2)Последовательный порт. Режимы работы. Функционирование. Управление последовательным портом.Последовательный порт предназначен для реализации ввода или вывода данных, представленных в последовательном коде. При вводе последовательные данные поступают на линию RxD МК, накапливаются в буфере приёмника (в последовательно-параллельном регистре) и преобразуются в параллельную форму. Принятые данные из буфера приемника в параллельном виде выдаются на внутреннюю шину последовательного порта. При выводе последовательные данные формируются в буфере передатчика (параллельно-последовательном регистре) путем преобразования параллельной информации с шины последовательного порта в поток последовательных бит, поступающих затем на линию TxD МК. Буфер приемника и буфер передатчика при обращении к ним имеют одинаковые имя (SBUF) и адрес (99). Если в команде обращения имя SBUF обозначает регистр – источник данных, то обращение происходит к буферу приемника, читаются данные, поступившие в последовательный порт по линии RxD . Если в команде имя SBUF обозначает регистр назначения, то им является буфер передатчика. Загруженные в него параллельные данные преобразуются в последовательную форму и выводятся через линию TxD МК. Управление последовательным портом осуществляется через 8-разрядный управляющий регистр SCON (адрес 98).  Описание флагов и управляющих битов в составе регистра SCON: SM0, SM1 – двухразрядный код, определяющий номер рабочего режима (00, 01, 10, 11) последовательного порта (задается из программы): 00 – режим 0, синхронный последовательный ввод/вывод со скоростью FOSC/12; 01 – режим 1, асинхронный ввод или вывод с переменной скоростью и с 10-битовым кадром (старт-бит, 8 бит последовательных данных D0,…,D7, стоп-бит); 10 – режим 2, асинхронный ввод или вывод с фиксированной скоростью FOSC/32 или FOSC/64 и с 11-битовым кадром (старт-бит, 8 бит последовательных данных D0,…,D7, служебный бит D8, стоп-бит); 11 – режим 3, асинхронный ввод или вывод с переменной скоростью и с 11-битовым кадром (старт-бит, 8 бит последовательных данных D0,…,D7, служебный бит D8, стоп-бит). SM2 – бит запрета приема кадров с нулевым восьмым битом (D8 = 0); устанавливается и сбрасывается из программы; в режиме 1 должен быть установлен; в режиме 0 – сброшен. REN – бит разрешения приёма последовательных данных; устанавливается и сбрасывается из программы. TB8 – восьмой бит (D8) передатчика в режимах 2 и 3; устанавливается и сбрасывается из программы для задания подлежащего передаче значения служебного бита в кадре (признак информации, передаваемой в кадре). RB8 – восьмой бит (D8) приёмника в режимах 2 и 3; копия значения служебного бита D8 в принятом кадре (признака информации, принятой в кадре); в режиме 1 – записывается стоп-бит; в режиме 0 – не используется и должен быть равен 0; фиксируется аппаратными средствами приёмника. TI – флаг прерывания от передатчика; устанавливается аппаратно по окончании передачи кадра, сбрасывается из программы после обработки прерывания. RI – флаг прерывания от приемника; устанавливается аппаратно по окончании приёма кадра; сбрасывается из программы после обработки прерывания. Режим 0. Последовательный порт МК работает как 8-разрядный регистр сдвига. Данные последовательно передаются (передатчиком) или принимаются (приёмником) путём их сдвига через общую линию RxD младшими битами вперёд, по 8 разрядов за одну операцию обмена. Для синхронизации устройств, участвующих в обмене (регистров сдвига), передатчик формирует импульсы сдвига с частотой FOSC/12 и выдает их на общую линию TxD. Передача последовательных данных инициируется всякий раз, когда новый байт записывается в SBUF. Признаком окончания передачи служит установка флага TI. Приём данных активизируется (при разрешенном приёме последовательных данных – REN = 1) путём сброса флага RI. Снова установленный флаг указывает на готовность новых (введённых) данных, которые можно считывать из SBUF. Режим 1. Передача инициируется любой командой, для которой получателем байта является SBUF. Время передачи каждого бита последовательных данных равно 16 тактам специального счётчика (счётчика битинтервалов), пересчитывающего импульсы переполнения таймера/счётчика Т/С1. Частота переполнения Т/С1 определяет скорость выдачи последовательных данных передатчиком. Приём последовательных данных начинается с момента обнаружения перехода сигнала на входе RxD из состояния 1 в состояние 0 и включения счётчика бит-интервалов для приёмника. В середине каждого битинтервала производится опрос сигнала на входе RxD и принимаются решения о значении каждого последовательного бита. Принятые биты сдвигаются в регистр приёмника, затем запоминаются в SBUF – после чего устанавливается флаг RI. После окончания приема кадра устройство управления приёмом вновь начинает отыскивать переход 1 – 0 на входе RxD. Режим 2. Скорость передачи в режиме 2 постоянная, но зависит от значения флага SMOD в регистре PCON и может быть равна либо FOSC/32 (SMOD = 0), либо FOSC/64 (SMOD = 1). Режим 3 . Скорость передачи переменная и определяется частотой переполнения таймера/счётчика Т/С, но может понижаться в 2 раза при значении флага SMOD = 0 в регистре PCON. При SMOD = 1 скорость передачи совпадает с частотой переполнения. Флаги приёмника RI и передатчика TI могут использоваться для запроса прерывания. В режимах 1, 2, 3 при значении флага SM2 = 1 установка флага RI и генерация запроса от него на прерывание возможны лишь при приёме кадра с D8 = 1. Для режима 1 это означает контроль кадра на наличие стоп-бита. Для режимов 2 и 3 такая работа обеспечивает выделение кадров одного класса, в которых D8 = 1. Кадры, в которых D8 = 0, в SBUF не записываются и теряются. Возможность реагировать только на кадры с RB8 = D8 = 1 или принимать любые кадры при SM2 = 0 может использоваться при построении управляющей системы из нескольких МК, объединённых в единую сеть на основе использования последовательной передачи данных. 4)Структура ЦАП ШИМ Особенность ЦАП с ШИМ в составе микроконтроллера в том, что он построен только на цифровых компонентах, не содержит прецизионных элементов, требующих настройки или подгонки (резисторов Выходной сигнал ЦАП с ШИМ – последовательность прямоугольных импульсов с постоянной амплитудой, с постоянным периодом повторения Т, но с изменяемой скважностью (скважность s = TQ/T, где TQ – длительность выходного импульса), которая определяет величину напряжения на выходе ЦАП. Скважность выходных импульсов определятся числовым значением кода на входе ЦАП: на входе все нули – скважность выходных импульсов минимальная (постоянная составляющая импульсного выходного напряжения минимальна); на входе все единицы – скважность максимальная (постоянная составляющая импульсного выходного напряжения максимальна). Для промежуточных числовых значений входного кода постоянная составляющая выходного импульсного напряжения пропорциональна коду на входе ЦАП. Получение постоянной составляющей как результата цифро-аналогового преобразования требует усреднения импульсов на выходе ЦАП на интервале времени, многократно превышающем период следования импульсов. Для этого используются интегрирующие RC-цепи с большой постоянной времени или интеграторы на основе операционных усилителей. Такие сглаживающие схемы подключаются к выходу ЦАП ШИМ микроконтроллера. Необходимость усреднения последовательности импульсов на большом интервале времени и определяет невысокое быстродействие таких ЦАП, что является их недостатком. Схема макета для изучения 4-разрядного ЦАП с ШИМ представлена на рис. 1. Собственно ЦАП с ШИМ состоит из параллельного регистра (Х1) для хранения входного цифрового кода, двоичного счётчика импульсов (Х2) для формирования "цифровой пилы", цифрового компаратора (Х3) для сравнения двоичных чисел {а3, а2, а1, а0} и {q3, q2, q1, q0} и выходного триггера ШИМ для формирования выходного импульсного сигнала с ШИМ. Генератор цифрового сигнала (U1) в составе макета формирует цифровые коды входного сигнала, подлежащие преобразованию в аналоговые величины. По умолчанию генератор U1 запрограммирован на формирование с частотой 16,66 кГц числовых значений смещённой синусоиды (16 точек в периоде). Буферы-инверторы U2 и U4 используются в качестве источников высокого логического уровня для тактового входа входного регистра (обеспечивается прозрачность регистра Х1), для настройки компаратора Х3 на режим формирования сигнала на выходе n1 при равенстве чисел на входах А и В и для входа D выходного триггера Х4. Генератор импульсов V1 вырабатывает непрерывную последовательность импульсов С1 с частотой 2,5 мГц (по умолчанию) для счётного входа двоичного счётчика Х2. Буферы U3 и U5 обеспечивают при моделировании схемы трансляцию аналогового сигнала на цифровой узел и цифрового сигнала на аналоговый узел. Сглаживание выходных импульсов с ШИМ выполняет внешняя интегрирующая RC-цепь. По умолчанию постоянная времени RC-цепи равна 100 мкс. Функционирование ЦАП с ШИМ. Четырёхразрядный двоичный счётчик импульсов Х2 работает непрерывно и последовательно формирует все 16 кодовых комбинаций – от 0000 до 1111. При каждом переполнении счётчика (состояние 1111 изменяется на 0000) на выходе переполнения p формируется отрицательный фронт, который используется в качестве фронта переключения для выходного D-триггера Х4, и триггер Х4 устанавливается в состояние 1, так как на его синхронном входе D – всегда 1. Таким образом, при каждом переполнении счётчика Х2 на выходе триггера Х4 (выход n) формируется положительный (передний) фронт выходного импульса. Отрицательный (задний) фронт выходного импульса формируется с запаздыванием – в результате сброса триггера Х4 по асинхронному входу R высоким уровнем сигнала с выхода A= компаратора Х3 (линия n1), который устанавливается при равенстве кодов на его входах А и В. Из этого следует, что период следования выходных импульсов постоянен и равен периоду переполнения двоичного счётчика Х2 (16 периодов тактового генератора V1), а длительность выходных импульсов равна сумме периодов импульсов C1 в количестве, равном числовому значению входного цифрового кода а3а2а1а0. Аналоговое напряжение, как результат ЦАП, содержится в постоянной составляющей выходного импульса на интервале периода повторения. В схеме рис.1. усреднение выходных импульсов ЦАП выполняет интегрирующая RC-цепь.  5)Прерывание. Управление прерываниями. Система прерываний предусматривает пять источников прерываний: внешние (от входов INT0 , INT1) и внутренние (от флагов переполнения TF0, TF1 таймеров/счётчиков и от флага RI или TI последовательного порта). Внешние запросы прерываний INT0 , INT1 независимо друг от друга могут быть запрограммированы на срабатывание либо по переходу из 1 в 0, либо по низкому уровню входного сигнала запроса прерывания (регистр TCON). Для каждого из пяти источников прерываний может быть запрограммирован один из двух уровней приоритета (0 – низкий приоритет, 1 – высокий приоритет). Управление приоритетом прерываний осуществляется через 8разрядный управляющий регистр IP (адрес B8). Описание управляющих битов в составе регистра IP:  PS – бит приоритета последовательного порта; устанавливается и сбрасывается из программы. PT1 – бит приоритета Т/С1 (TF1); устанавливается и сбрасывается из программы. PX1 – бит приоритета внешнего прерывания от входа INT1; устанавливается и сбрасывается из про- граммы. PT0 – бит приоритета Т/С0 (TF0); устанавливается и сбрасывается из программы. PX0 – бит приоритета внешнего прерывания от входа INT0 ; устанавливается и сбрасывается из программы. низкий уровень приоритета. IP.i = 0 – IP.i = 1 – высокий уровень приоритета. Обработка прерывания низкого уровня может быть прервана запросом высокого уровня. Если одновременно появляются несколько запросов одного уровня, используется схема арбитража, основанная на порядке последовательного опроса разрядов регистра IP и устанавливающая предпочтения между всеми источниками запросов.  Описание управляющих битов в составе регистра IE: EA – бит блокировки всех прерываний; EA = 0 – все прерывания запрещены; EA = 1 – прерывания мо- гут быть разрешены управляющими битами ES, ET1, EX1, ET0, EX0; устанавливается и сбрасыва- ется из программы. ES – бит разрешения прерывания от последовательного порта (по признаку RI окончания работы приём- ника или по признаку TI окончания работы пере- датчика); устанавливается и сбрасывается из про- граммы. ET1 – бит разрешения прерывания от Т/С1 (TF1); устанавливается и сбрасывается из программы. EX1 – бит разрешения внешнего прерывания от входа INT1; устанавливается и сбрасывается из про- граммы. ET0 – бит разрешения прерывания от Т/С0 (TF0); устанавливается и сбрасывается из программы. EX0 – бит разрешения внешнего прерывания от входа INT0 ; устанавливается и сбрасывается из программы. прерывания от соответствующего источника запрещены (замаскированы). IE.i = 0 – IE.i = 1 – прерывания от соответствующего источника разрешены. Установка соответствующего флага при наличии запроса прерывания происходит в конце текущего машинного цикла, а опрос флагов – в следующем цикле. И только после выполнения последнего цикла текущей команды производится аппаратный вызов соответствующей подпрограммы обслуживания, эквивалентный команде LCALL vect, обеспечивающей переход к стартовому адресу (vect) соответствующей подпрограммы обслуживания. С каждым источником прерывания связан свой стартовый адрес (вектор прерывания).  |