цифровые устройства и микропроцессоры. 1 Назначение psw. Структура

Скачать 6.57 Mb. Скачать 6.57 Mb.

|

|

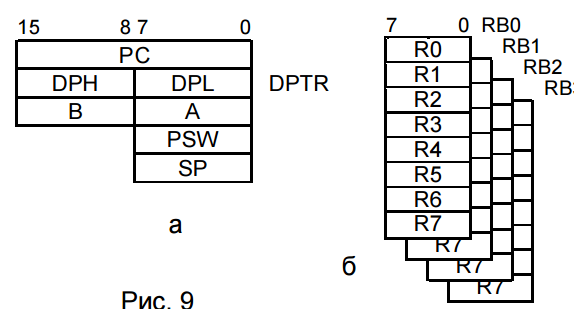

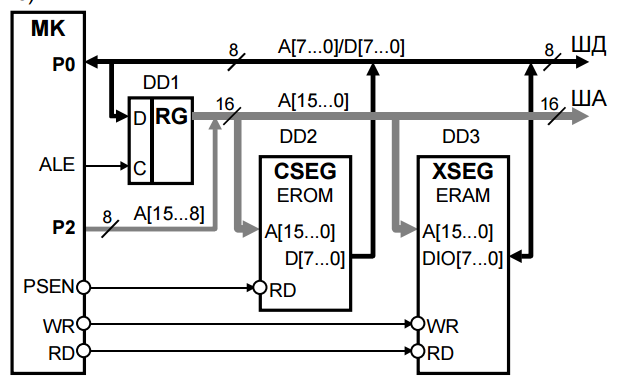

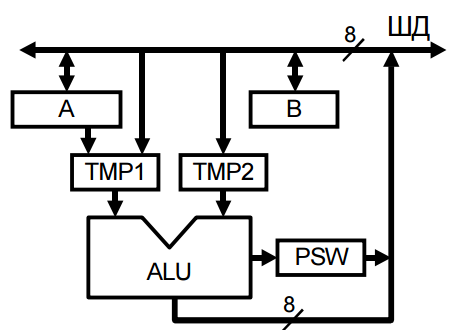

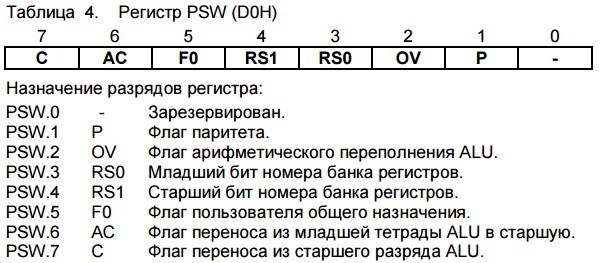

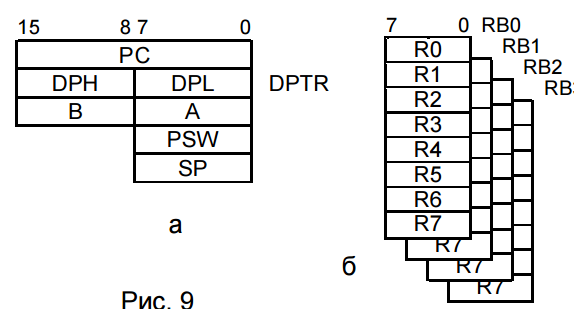

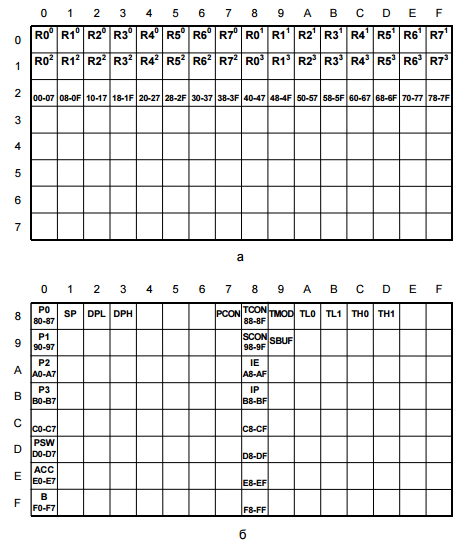

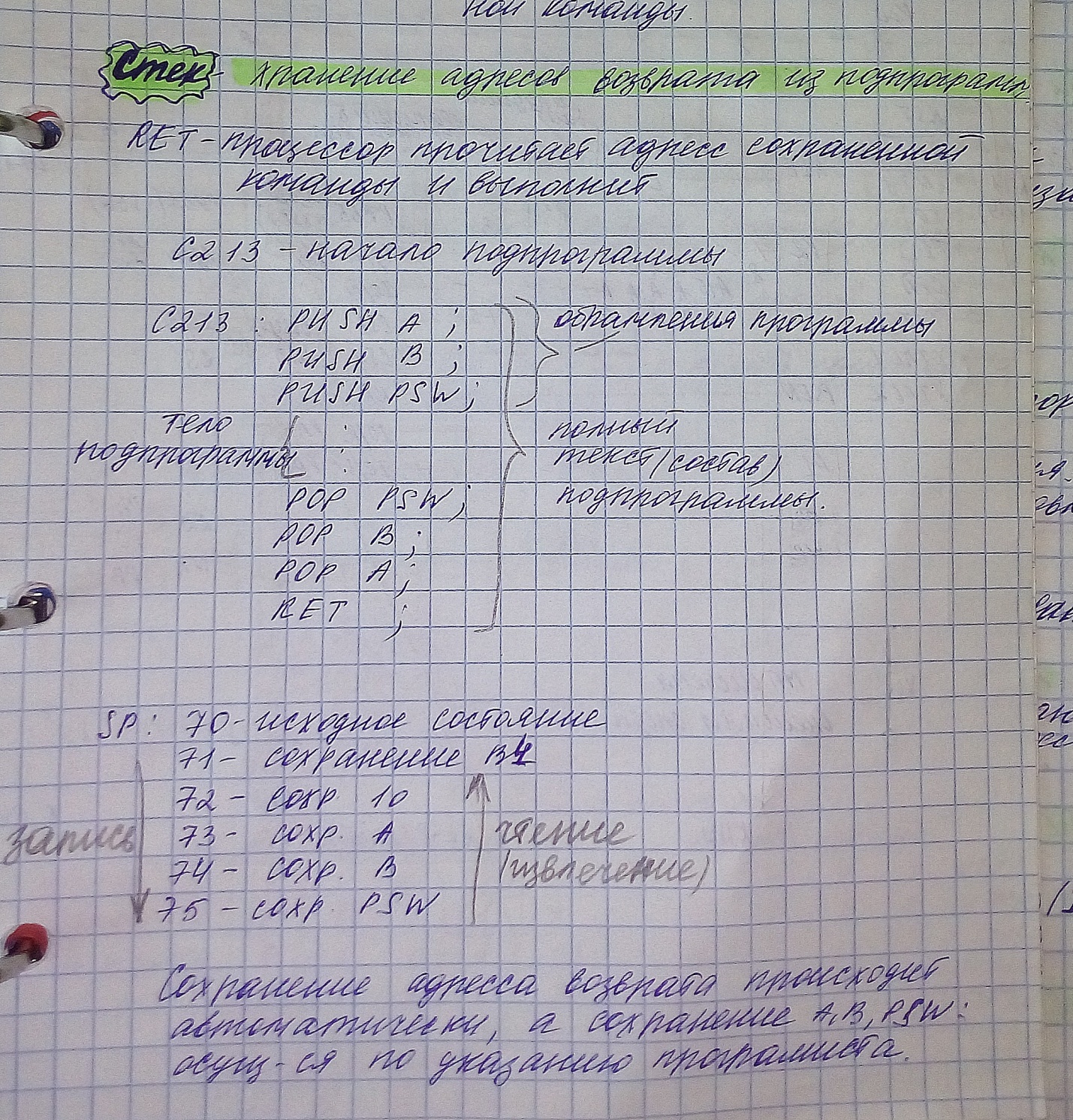

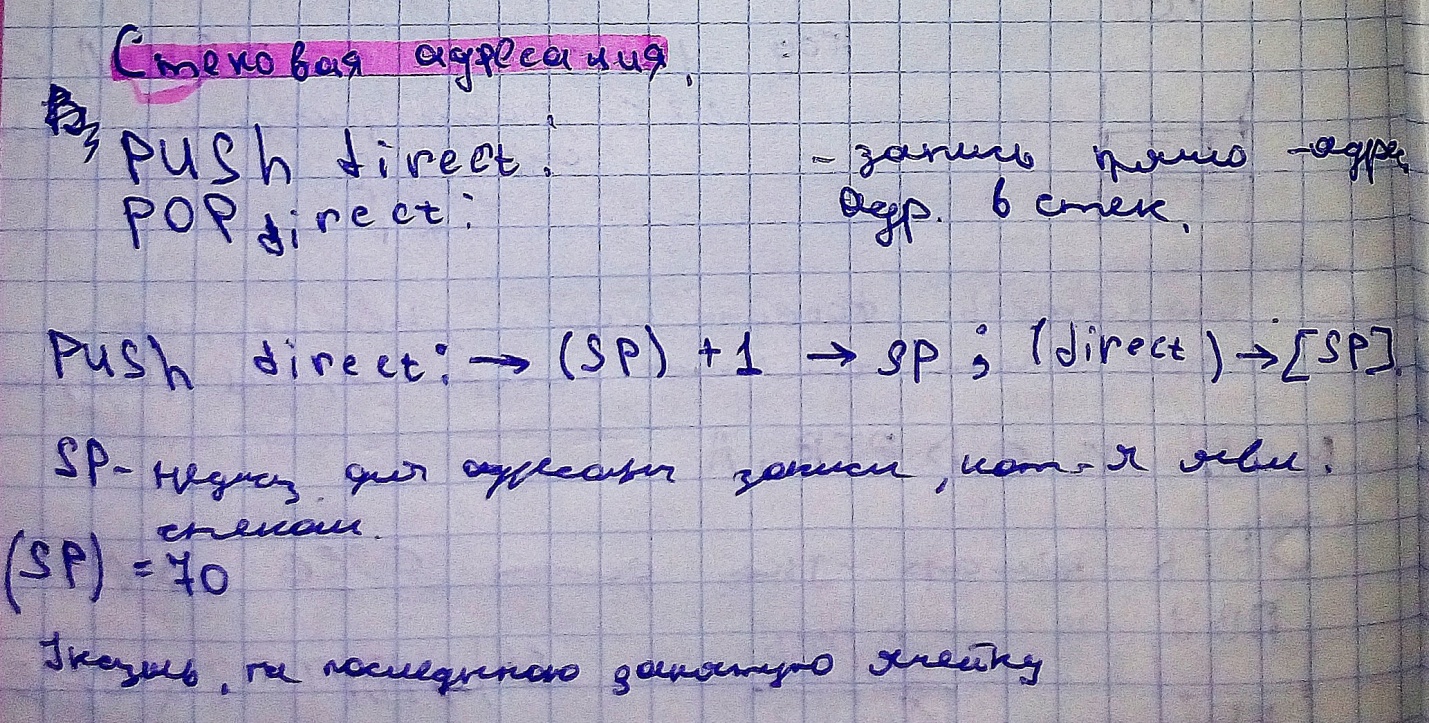

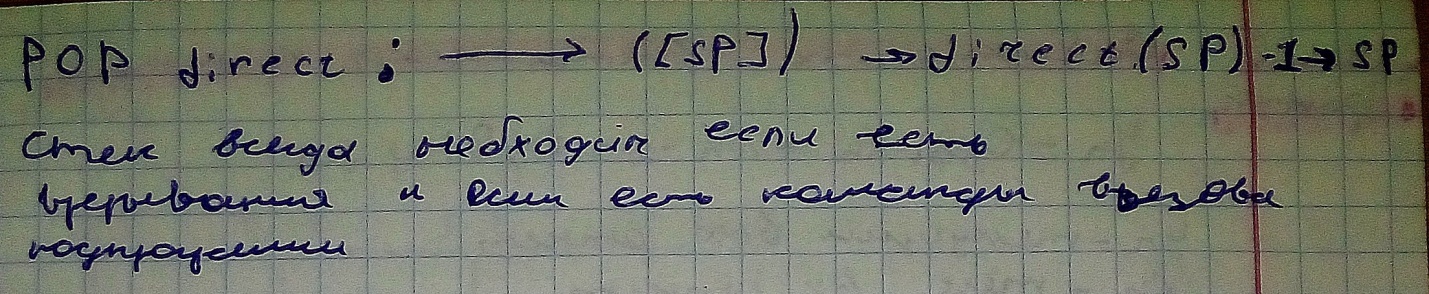

Быстродействие (время преобразования) параллельного АЦП равно интервалу времени с момента взятия дискретного отсчёта напряжения из СВХ до установления адреса в приоритетном шифраторе (1 такт). Чтение выходного кода ЦАП осуществляется из выходного регистра управляющим импульсом Start. 26)ЦАП с суммирование напряжений.Цифровой потенциометр Цифровой потенциометр – это регулируемый делитель напряжения, построенный на основе резистивной матрицы из одинаковых по величине сопротивлений. Это позволяет дискретно изменять с помощью управляющего кода снимаемое с делителя напряжение путём коммутации точки съёма выходного напряжения. В микропроцессорных системах управления цифровой потенциометр позволяют задавать режимы и осуществлять регулировки в электронных схемах подобно обычным регулируемым резисторам и механическим потенциометрам. Принцип построения и функционирования цифрового потенциометра раскрывает схема, представленная на рис.4. Кроме резистивного делителя R1, ... , R7 в схеме использованы дешифратор Х1 и аналоговые коммутаторы АК0, ... , АК7 (рис.3). Для представленной на рис.4 конфигурации схемы, при опорном напряжении Vref2 = 0, результат её работы идентичен результату работы цифро-аналогового преобразователя. Цифровой код на входе дешифратора активизирует только один его выход, который включает соответствующий АК и подключает через него выход цифрового потенциометра к заданному узлу резистивного делителя. Шаг квантования выходного напряжения Uout определяется разрядностью входного кода и значениями опорных напряжений Vref1, Vref2, которые могут иметь разную полярность.  28)Особенности команд перехода и вызова подпрограммы Группа команд передачи управления (таблицы П2.4 и П2.5) со- держит команды безусловного перехода AJMP, LJMP, SJMP, JMP, ус- ловного перехода JZ, JNZ, CJNE, вызова ACALL, LCALL, возврата RET, RETI и модификации с условным переходом DJNZ. Сюда же включена пустая команда NOP. В командах передачи управления широко применяется относи- тельная адресация, позволяющая создавать перемещаемые программ- ные модули. В качестве относительного адреса выступает 8-разрядное смещение rel – байт со знаком, обеспечивающее переход на (–128… +127) байт относительно текущего положения PC. Для перехода в лю- бую другую точку 64 Кбайтового адресного пространства может быть использован либо прямой addr16, либо косвенный @A+DPTR адрес. В последнем случае содержимое A интерпретируется как целое без зна- ка. Вариант короткой прямой адресации addr11 внутри 2 Кбайтовой те- кущей страницы введен для совместимости с семейством MCS-48. Все эти типы адресации применяются в командах перехода. В ко- мандах вызова используются только прямой addr16 и внутристранич- ный addr11 способы адресации. Во всех условных командах использу- ется только относительная адресация. Когда микроконтроллер опознает запрос на прерывание, он гене- рирует команду LCALL addr16, что автоматически обеспечивает запо- минание адреса возврата в стеке. Информация о состоянии программы (содержимое регистра PSW) автоматически не сохраняется. При этом45 логика прерываний запоминает уровень приоритета обслуживаемого прерывания. При выполнении команды RET уровень приоритета сохра- няется и следующим может быть обслужено только прерывание с бо- лее высоким уровнем приоритета. Команда RETI отличается от коман- ды RET тем, что она сбрасывает уровень приоритета, что позволяет обслуживать запросы на прерывания с низким уровнем приоритета. К типовым условным операциям относятся команды JZ и JNZ, JC и JNC. Две последних включены в группу «булевых». В команде CJNE сначала сравниваются, по правилам вычитания целых чисел, два байта и в соответствии с результатом сравнения устанавливается флаг C. За- тем, в случае их несовпадения, выполняется ветвление. В команде DJNZ в качестве счетчика может использоваться не только один из регистров текущего регистрового банка Rn, n=0...7, но и прямо адресуемая ячейка памяти данных DSEG. При исполнении ко- манды сначала выполняется декремент счетчика и, если содержимое счетчика не равно нулю, ветвление. 29)Сегментация памяти внутренней и внешней Внутренняя память дан- ных DSEG располагается во внутреннем ОЗУ и может иметь объем 128 или 256 байт. В типо- вой конфигурации DSEG имеет объем 128 байт и располагается в нижней области данных, зани- мающей адресное пространство 00h…7Fh. В этой области DSEG можно использовать прямую и косвенную адресацию операн- дов. Область памяти с адресами 80h…FFh занимают регистры специальных функций SFR (Special Function Registers). В ней разрешена только прямая адресация (рис. 8). При объеме в 256 байт имеется как нижняя, так и верхняя облас- ти данных. Адресные пространства верхнего DSEG и регистров специ- альных функций SFR совпадают и для их различия использованы раз- ные способы адресации. Обращение к верхней области DSEG осуще- ствляется только командами косвенной адресации, а к регистрам спе- циальных функций – прямой. Карта памяти нижней области DSEG при- ведена на рис. 10,а. Пространство регистров RSEG содержит 32 регистра, сгруппи- рованных в 4 регистровых банка (Register Banks) RB0...RB3 по 8 реги- стров (R0...R7) в каждом (рис. 9,б). Все регистры выполняют общецеле- вые функции промежуточного хранения данных, а два регистра R0 и R1 каждого банка еще и функцию 8-разрядного указателя данных в коман- дах косвенной адре- сации. Регистровые банки переключаются полем RS слова со- стояния программы PSW. Физически RSEG расположен в области DSEG с ад- ресами 00h...1Fh (рис. 10,а). Такое со- вмещение позволяет двояко интерпретиро- вать содержимое ячейки, что дает возможность программисту выбрать наиболее подходящий вариант для уменьшения объема и повышения скорости исполнения программы  Пространство битов BSEG предназначено для хранения буле- вых данных. Оно имеет объем в 256 бит и разделено на две области по 128 бит каждая. Одна область BSEG с адресами 00h...7Fh физически совмещена с шестнадцатью ячейками памяти DSEG, имеющими адреса 20h...2Fh, и является областью общего назначения (рис. 10,а). Другая область с адресами 80h..FFh физически совмещена с областью регист- ров специальных функций SFR, что обеспечивает доступ к отдельным разрядам регистров (рис. 10,б). В битовом пространстве определена только прямая адресация bit и действует свой набор команд, опреде- ляемых битовым процессором. Роль аккумулятора битового процессо- ра выполняет бит C регистра PSW. Пространство внешней памяти данных XSEG может иметь объ- ем 64 Кбайт и реализуется внешними средствами (рис. 12). Связь с XSEG поддерживается единственной командой MOVX, имеющей два типа адресации: косвенную регистровую по DPTR и страничную с номе- рами страниц в порту P2 и смещением в R0, R1. Это позволяет рас- сматривать организацию внешней памяти как область с линейной или со страничной структурой адресации. Адресное пространство памяти данных внешнего XSEG и внутреннего DSEG не связаны между собой. Программный счетчик может адресовать память программ CSEG с адресным пространством 64 Кбайт. Часть этой памяти (в базовой конфигурации 4 Кбайт) размещено во внутреннем ПЗУ и образует внут- реннюю память программ. Оставшаяся часть может быть реализована внешними средствами и называется внешней памятью программ. Кон- фигурирование памяти программ осуществляется управлением по вхо- ду EA __ . При EA __ =0 доступ к внутренней памяти запрещается, и микро- контроллер обращается только к внешней памяти, адрес которой начи- нается с 0000h (рис. 11,а). При EA __ = 1 адресное пространство внешней памяти программ является продолжением адресного пространства внутренней памяти программ (рис. 11,б). Обращение к внешней па- мяти происходит автомати- чески всякий раз при пре- вышении текущим адресом максимального адреса внут- ренней памяти (0FFFh для объема 4 Кбайт). По этой причине внутренняя и внеш- няя память программ пред- ставляют собой единое ли- нейное пространство. В начале CSEG распо- ложена таблица векторов прерывания. Каждому источнику прерывания соответствует свой адрес ячейки памяти (вектор прерывания). Он за- гружается в программный счетчик PC при обслуживании прерывания 2.2.4. Внешняя память программ и данных Схема включения внешних CSEG и XSEG показана на рис.12. Она содержит 8-разрядный параллельный регистр DD1 на одноступенчатых триггерах с прямым потенциальным управлением, внешние ПЗУ DD2 (CSEG) и ОЗУ DD3 (XSEG). Внешняя 8-разрядная (D[7...0]) шина дан- ных ШД формируется из линий порта Р0. Младший байт адреса по стробу ALE фиксируется в регистре DD1 и вместе со старшим байтом, выдаваемым портом Р2, образует 16-разрядную шину адреса ША При низком уровне сигнала PSEN _____ выполняется чтение команды из CSEG, а при высоком - выходы DO[7...0] (Data Output) должны перейти в третье состояние (рис. 6,б). Низким уровнем сигнала WR ___ производится запись байта с шины данных ШД в XSEG (рис. 6,в), а низ- ким уровнем сигнала RD ___ чтение бай- та из XSEG на ШД (рис. 6,г). При вы- соких уровнях сигналов WR ___ и RD ___ двунаправленные выводы DIO[7...0] (Data Input/Output) внешнего ОЗУ DD3 должны находиться в третьем состоянии. Данные из CSEG читаются в устройство управления центрального процессора, а XSEG обменивается данными с операционным устройст- вом. Единственная команда MOVC позволяет читать данные из CSEG в аккумулятор операционного устройства. Это позволяет использовать программную память для размещения констант, доступных для опера- ционного устройства.  25)Типовая схема арифмитического узла Операционное устройство выполнено по классической схеме и служит для обработки 8-разрядных данных (рис. 4). Оно содержит арифметико-логическое устройство ALU, аккумулятор A, два программ- но-недоступных регистра временного хранения TMP1 и TMP2, регистр слова состояния программы PSW (Program Status Word) и регистр B. В ALU выполняется операция над двумя операндами, находящи- мися в регистрах временного хранения TMP1 и TMP2. При выполнении операций данные интерпретиру- ются как целые числа без знака. Результат операции выдается на внутреннюю шину данных ШД, а во многих командах он также за- писывается в аккумулятор A. В командах умножения и деления роль источника и приемника ин- формации выполняют регистры A и B. При выполнении арифмети- ческих и логических операций в ALU вырабатываются признаки результата, которые записыва- ются в регистр PSW. Все биты регистра PSW, расположенного в облас- ти BSEG регистров специальных функций SFR, программно-доступны. Их можно устанавливать и сбрасывать командами программы.  Назначение разрядов регистра PSW дано в таблице 4. Флаг паритета P устанавливается любыми командами, в том чис- ле и командами передачи данных, регистром-приемником которых яв ляется аккумулятор. Если в разрядах аккумулятора содержится нечетное число единиц, то P=1. Девятиразряд- ное слово, составленное из содержи- мого аккумулятора и бита P, всегда со- держит четное число единиц (четный паритет). Битами RS1 и RS0 выбирается в качестве рабочего один из четырех ре- гистровых банков RBx (x=0...3) (таблица 5). Флаг арифметического переполнения OV=1 устанавливается, ес- ли при сложении двух чисел с одинаковыми знаками результат имеет противоположный знак. В командах битовой адресации аккумулятором является бит C   8)Логические объекты и их физическое расположение 29)Сегментация памяти внутренней и внешней Внутренняя память дан- ных DSEG располагается во внутреннем ОЗУ и может иметь объем 128 или 256 байт. В типо- вой конфигурации DSEG имеет объем 128 байт и располагается в нижней области данных, зани- мающей адресное пространство 00h…7Fh. В этой области DSEG можно использовать прямую и косвенную адресацию операн- дов. Область памяти с адресами 80h…FFh занимают регистры специальных функций SFR (Special Function Registers). В ней разрешена только прямая адресация (рис. 8). При объеме в 256 байт имеется как нижняя, так и верхняя облас- ти данных. Адресные пространства верхнего DSEG и регистров специ- альных функций SFR совпадают и для их различия использованы раз- ные способы адресации. Обращение к верхней области DSEG осуще- ствляется только командами косвенной адресации, а к регистрам спе- циальных функций – прямой. Карта памяти нижней области DSEG при- ведена на рис. 10,а. Пространство регистров RSEG содержит 32 регистра, сгруппи- рованных в 4 регистровых банка (Register Banks) RB0...RB3 по 8 реги- стров (R0...R7) в каждом (рис. 9,б). Все регистры выполняют общецеле- вые функции промежуточного хранения данных, а два регистра R0 и R1 каждого банка еще и функцию 8-разрядного указателя данных в коман- дах косвенной адре- сации. Регистровые банки переключаются полем RS слова со- стояния программы PSW. Физически RSEG расположен в области DSEG с ад- ресами 00h...1Fh (рис. 10,а). Такое со- вмещение позволяет двояко интерпретиро- вать содержимое ячейки, что дает возможность программисту выбрать наиболее подходящий вариант для уменьшения объема и повышения скорости исполнения программы  Пространство битов BSEG предназначено для хранения буле- вых данных. Оно имеет объем в 256 бит и разделено на две области по 128 бит каждая. Одна область BSEG с адресами 00h...7Fh физически совмещена с шестнадцатью ячейками памяти DSEG, имеющими адреса 20h...2Fh, и является областью общего назначения (рис. 10,а). Другая область с адресами 80h..FFh физически совмещена с областью регист- ров специальных функций SFR, что обеспечивает доступ к отдельным разрядам регистров (рис. 10,б). В битовом пространстве определена только прямая адресация bit и действует свой набор команд, опреде- ляемых битовым процессором. Роль аккумулятора битового процессо- ра выполняет бит C регистра PSW. Пространство внешней памяти данных XSEG может иметь объ- ем 64 Кбайт и реализуется внешними средствами (рис. 12). Связь с XSEG поддерживается единственной командой MOVX, имеющей два типа адресации: косвенную регистровую по DPTR и страничную с номе- рами страниц в порту P2 и смещением в R0, R1. Это позволяет рас- сматривать организацию внешней памяти как область с линейной или со страничной структурой адресации. Адресное пространство памяти данных внешнего XSEG и внутреннего DSEG не связаны между собой. Программный счетчик может адресовать память программ CSEG с адресным пространством 64 Кбайт. Часть этой памяти (в базовой конфигурации 4 Кбайт) размещено во внутреннем ПЗУ и образует внут- реннюю память программ. Оставшаяся часть может быть реализована внешними средствами и называется внешней памятью программ. Кон- фигурирование памяти программ осуществляется управлением по вхо- ду EA __ . При EA __ =0 доступ к внутренней памяти запрещается, и микро- контроллер обращается только к внешней памяти, адрес которой начи- нается с 0000h (рис. 11,а). При EA __ = 1 адресное пространство внешней памяти программ является продолжением адресного пространства внутренней памяти программ (рис. 11,б). Обращение к внешней па- мяти происходит автомати- чески всякий раз при пре- вышении текущим адресом максимального адреса внут- ренней памяти (0FFFh для объема 4 Кбайт). По этой причине внутренняя и внеш- няя память программ пред- ставляют собой единое ли- нейное пространство. В начале CSEG распо- ложена таблица векторов прерывания. Каждому источнику прерывания соответствует свой адрес ячейки памяти (вектор прерывания). Он за- гружается в программный счетчик PC при обслуживании прерывания  Область регистров специальных функций SFR содержит регист- ры, обслуживающие порты, таймеры/счетчики, систему прерываний и энергосбережения. Здесь также находится аккумулятор A и регистр B, служащий расширением аккумулятора в командах умножения и деле- ния. В других командах регистр В выполняет общецелевые функции. Список регистров специальных функций с адресами для типовой кон- фигурации микроконтроллеров семейства MCS-51 приведен в табли- це 7, а карта памяти представлена  При включении микроконтроллера или аппаратном сбросе (RST=1) в указатель стека SP записывается значение 07h (для обеспе- чения совместимости с семейством MCS-48), триггеры всех разрядов параллельных портов устанавливаются в состояние 1, переводя все линии в режим «Чтение». Все используемые разряды остальных реги- стров устанавливаются в состояние 0, а состояние неиспользуемых (зарезервированных) разрядов и регистра SBUF не определено. 22)Стек.Назначение и основные определения.Правила работы.Пример    |