Модуль 3. 1. Память эвм, ее характеристики. Структура памяти. Постоянные запоминающие устройства (программируемые маской, перепрограммируемые eprom, eeprom). Оперативные запоминающие устройства статического и динамического типов. Стек. Виртуальная память

Скачать 2.32 Mb. Скачать 2.32 Mb.

|

|

Чипсет - от англ. "chip set" - набор микросхем, спроектированных для совместной работы с целью выполнения набора каких-либо функций. Так, в компьютерах чипсет выполняет роль связующего компонента, обеспечивающего совместное функционирование подсистем памяти, ЦПУ, ввода-вывода и других. Чипсеты встречаются и в других устройствах, например, в радиоблоках сотовых телефонов. Чипсет материнских плат компьютеров состоит из двух основных микросхем (иногда они объединяются в один чип):

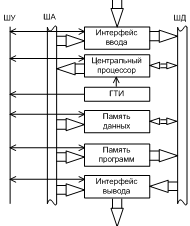

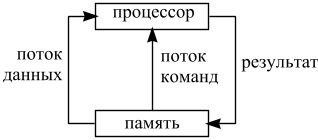

Также иногда к чипсетам относят микросхему Super I/O, которая подключается к южному мосту и отвечает за низкоскоростные порты RS232, LPT, PS/2. В настоящее время основными производителями чипсетов для настольных компьютеров являются фирмы Intel, nVidia, AMD (которая приобрела фирму ATI и в настоящее время выпускает чипсеты под своим именем), VIA и SIS. Фирма Intel выпускает чипсеты только для собственных процессоров. Для процессоров фирмы AMD наиболее распространенными являются чипсеты nVidia (выпускаемые как правило под торговой маркой nForce) и AMD. Чипсеты фирм VIA и SIS популярны в основном в секторе low end, а также в офисных системах, хотя встроенная графика у них по 3D возможностям значительно уступает nVidia и AMD. Микропроцессоры Центральный процессор (ЦП) - программно-управляемое устройство обработки информации, предназначенное для управления работой всех блоков машины и выполнения арифметических и логических операций. Функции процессора: чтение команд из ОЗУ; декодирование команд, то есть определение их назначения, способа выполнения и адресов операндов; исполнение команд; управление пересылкой информации между МПП, ОЗУ и периферийными устройствами; обработка прерываний; управление устройствами, составляющими ЭВМ. Центральный процессор состоит из устройства управления, арифметико-логического устройства, микропроцессорной памяти, генератор тактовой частоты (ГТЧ). Устройство управления (УУ) -- формирует и подает во все блоки машины управляющие импульсы; выдает адреса требуемых ячеек памяти, и передает их в другие блоки ЭВМ. Арифметико-логическое устройство АЛУ состоит из регистров памяти, сумматора и схем управления; используется для выполнения арифметических и логических операций над числовой и символьной информацией. Для увеличения скорости работы АЛУ подключают математический сопроцессор. Запоминающее устройство - это внутренняя память процессора. Регистры служит промежуточной быстрой памятью, используя которые, процессор выполняет расчёты и сохраняет промежуточные результаты. Для ускорения работы с оперативной памятью используется кэш-память, в которую с опережением подкачиваются команды и данные из оперативной памяти, необходимые процессору для последующих операций. Генератор тактовой частоты генерирует электрические импульсы, синхронизирующие работу всех узлов компьютера. В ритме ГТЧ работает центральный процессор. Основные характеристики микропроцессора:

Быстродействие (вычислительная мощность) – это среднее число операций процессора в секунду. 1)Тактовая частота в МГц. Тактовая равна количеству тактов в секунду. Такт - это промежуток времени между началом подачи текущего импульса ГТЧ и началом подачи следующего. Тактовая частота отражает уровень промышленной технологии, по которой изготавливался данный процессор. 2)Разрядность процессора - это максимальное количество бит информации, которые могут обрабатываться и передаваться процессором одновременно. Разрядность процессора определяется разрядностью регистров, в которые помещаются обрабатываемые данные. Система команд процессора представляет собой набор отдельных операций, которые может выполнить процессор данного типа. Разные модели микропроцессоров выполняют одни и те же операции за разное число тактов. Чем выше модель микропроц тем, меньше тактов требуется для выполнения одних и тех же операций. Для математических вычислений к основному микропроцессору добавляют математический сопроцессор. Начиная с модели 80486DX процессор и сопроцессор выполняют на одном кристалле. Шины микропроцессорной системы.  Шина данных — это основная шина, ради которой и создается вся система. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд. Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями. Шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2N, где N — количество разрядов. Например, 16-разрядная ША обеспечивает 65 536 адресов. Шина управления — это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управл сигналы обслуживают запрос и предоставление прерываний, запрос и предост прямого доступа.  Процессор 8086 состоит из операционного устройства, которое выполняет команды, и из устройства шинного интерфейса, которое выбирает команды, считывает операнды и записывает результаты. Оба устройства могут работать параллельно и в большинстве случаев обеспечивают значительное совмещение выборки и выполнения команд. В результате этого время выборки команды как-бы "исчезает" из цикла команды, так как операционное устройство выполняет команды, уже выбранные шинным интерфейсом. Процессор 8086 состоит из операционного устройства, которое выполняет команды, и из устройства шинного интерфейса, которое выбирает команды, считывает операнды и записывает результаты. Оба устройства могут работать параллельно и в большинстве случаев обеспечивают значительное совмещение выборки и выполнения команд. В результате этого время выборки команды как-бы "исчезает" из цикла команды, так как операционное устройство выполняет команды, уже выбранные шинным интерфейсом.PSW – регистр слова состояния процессора АХ – аккумулятор ВХ – регистр базового адреса СХ- счетчик в операциях сдвигов, циклических операциях и др. DX – неявно адресуется в операциях * и /, исп-ся в адресации портов CS, SS, DS, ES – сегменты: кодовый, стековый, данных, доп-ный данных. Начальные адреса (16 из 20 разрядов адреса) хранятся в сегментных регистрах. Команды с обращением к памяти формируют 16-разрядный исполнительный адрес (ЕА), представляющий собой смещение в сегменте емкостью 64 kb. Т.о. физ адрес = сегм регистры + ЕА. При адресации портов I/O сегм регистры не исп-ся. SP – указатель вершины стека BP – указатель базы (?) SI – индексный указатель (индекс источника) DI – индекс приемника IP – указатель команд (программный счетчик) 4. Прерывания. Типы прерываний. Структура и обслуживание прерываний. Таблицы указателей векторов прерываний. Контроллер прерываний. Прерывание — сигнал, сообщающий процессору о наступлении какого-либо события. При этом выполнение текущей последовательности команд приостанавливается, и управление передаётся обработчику прерывания, который реагирует на событие и обслуживает его, после чего возвращает управление в прерванный код. Прерывания делятся:

Запросы, поступающие как от внутренних источников так и внешних выстраиваются по приоритетности. Прерывание вызывает обработчик прерываний, который вызывает прерывающую программу. Она состоит из 3 частей:

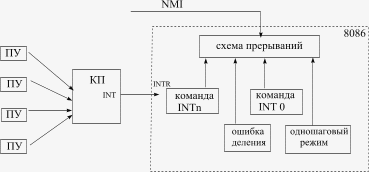

Имеется два входа для обслуживания прерываний: немаскируемый NMI - пользователь не может блокировать запросы, маскируемый INTR (запрос на прерывание принимается но не обслуживается). При выполнении программ могут автоматически вырабатываться внутренние прерывания (division by 0). Также имеется режим пошагового выполнения программы.  При возникновении сигнала на обслуживание маскируемого прерывания от КП процессор:

Обслуживание немаскируемого прерывания происходит быстрее и они имеют фиксированный код, не требует подтверждения и считывания типа прерывания (алгоритм обработки аналогичен маскируемым за описанными выше исключениями ). Внутренние прерывания для них тип прерываний предопределен либо содержится в коде команды. Эти прерывания нельзя запретить кроме прерывания пошаговой работы. Любое внутреннее прерывание имеет более высокий приоритет, чем внешние кроме прерывания пошаговой работы.

Приоритеты прерываний (в порядке убывания).

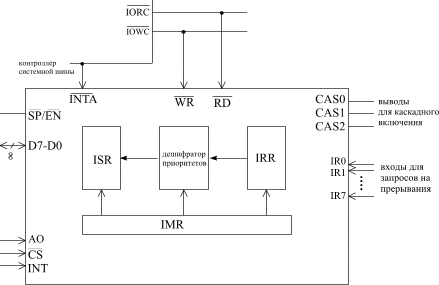

Для определения типа прерывания необходимо указать процедуру, которая обслуживает это прерывание. Для вызова процедуры составляется таблица указателей векторов прерываний, осуществляющая связь между кодом типа прерывания и процедурой, обслуживающей прерывания данного типа. При выполнении процедуры прерывания опускается в стек содержимое регистра флагов ,кодового сегмента (CS) и IP, а флаги прерывания IF и TF трассировки сброшены. Эта процедура может разрешить внешние прерывания и допускает прерывания на вход NMI и INT. После завершения процедуры прерывания последней командой должна быть команда возврата. Режим прерываний контрольной точки (необходим для отладки программы) позволяет сразу перейти на то место программы которое требуется выполнять в пошаговом режиме. Контрольной точкой называется то место программы где её выполнение приостановлено. Для обработки множества запроса на прерывания (а маскируемый вход всего один) в ЭВМ используются контроллеры прерываний. При возникновении ситуации, требующей немедленной реакции, машина должна прервать обработку текущих программ и перейти к программе обработки прерывания с последующим возвратом к выполнению прерванной программы этот процесс называется прерыванием программы. Таблицы указателей векторов прерываний Вектор прерывания – вектор нач-го состояния прерывающей программы. Вектор прерывания содержит всю необх. инф-ю для перехода к прерывающей программе, в том числе ее нач. адрес. Каждому уровню прерывания соотв-ет свой вектор прерывания. Векторы прерывания обычно нах-ся в спец-но выделенных фиксированных ячейках памяти. Различают абсолютный и относительный приоритеты. Запрос, имеющий абс. приоритет, прерывает выполняемую пр-му и инициирует вып-е соотв-щей прерывающей программы. Запрос с относ. приоритетом явл-ся первым кандидатом на обслуж-е после завершения вып-я текущей программы. Таблица указателей векторов прерываний осуществляет связь между кодом типа прерывания и процедурой, которая обслуживает прерывание данного типа. В микропроцессоре 8086 каждому прерыванию поставлен в соответствие код типа, допускается обработка до 256 типов прерываний. Таблица занимает 1 Кб памяти с диапазоном адресов 0–3FF и может содержать до 256 элементов. Каждый элемент i таблицы предст-ет собой полный нач. лог. адрес процедуры, которая обслуживает прерывание типа i. Слово с меньшим адресом содержит смещение, а слово с большим адресом – баз. адрес сегмента. Т.к. каждый элемент таблицы состоит из 4 байт, процессор выч-ет адрес нужного Эл-та таблицы путем умножения кода типа на 4.  Метод опроса предполагает поочередное опрашивание ПУ и определение его приоритета. Расположение ПУ в цепочке определяет его приоритетность, проанализировав значимость ПУ, можно изменить путь следования. Метод опроса предполагает поочередное опрашивание ПУ и определение его приоритета. Расположение ПУ в цепочке определяет его приоритетность, проанализировав значимость ПУ, можно изменить путь следования.Опрос продолжается до тех пор пока не обнаружится ПУ пославшее запрос на прерывание. Контроллер прерываний создает очередь ПУ (периферийных устройств), посылающих запросы на прерывания, обрабатывает информацию о приоритетности, определяет способ прерывания (векторные, методом поочередного опроса). Контроллер, получив запрос, формирует в свою очередь запрос к процессору.  Программируемый контроллер прерываний 8259A Одна микросхема PIC может обслуживать 8 запросов прерываний. В современных компьютерах на базе процессоров Intel используются две микросхемы PIC, объединенных с помощью так называемого каскадного включения, что позволяет обслуживать до 15 источников прерывания. Одна из микросхем является ведущей, а вторая – ведомая. Ведущий PIC связан с ЦП, а ведомый PIC с ведущим. Максимальные возможности каскадного включения PIC позволяют обслуживать до 64 внешних источников запросов прерываний. Связь между ведущим PIC и ЦП осуществляется по двум линиям: 1-ая линия INT PIC – INTR(CPU), 2 – ая линия INTA (CPU) – INTA (PIC). Основные функции PIC. Фиксация запросов, поступающих от подключенных к нему ВУ в специальном регистре запросов - IRR. Осуществление внутреннего маскирования запросов с помощью специального регистра – маски IMR (0 – разрешение, 1 - запрет). Выделение наиболее приоритетного запроса из всех поступивших и незамаскированных запросов. Выдача в ЦП сигнала о наличии хотя бы одного незамаскированного запроса (по линии 1). Выдача в ЦП номера (кода запроса) в цикле подтверждения прерывания, который, в свою очередь, модифицируется ЦП в адрес вектора прерываний (начальный адрес программы обработчика соответствующего прерываний). Внутренняя структура PIC. В состав PIC входят 7 байтных регистров, основными из которых являются: IRR – Interrupt Request Register IMR – Interrupt Mask Register ISR – Interrupt Service Register (фиксируются запросы, принимаемые на обслуживание или обработку в ЦП) Кроме регистров, в состав PIC входят комбинационные схемы, в частности: Схема выделения наиболее приоритетного незамаскированного запроса. Шифратор выделенного запроса. Шифратор представляет собой комбинационную схему, осуществляющую преобразование двоичного унитарного кода (код с единственной единицей) в двоичный позиционный код, в данном случае шифратор имеет 8 входов и 3 выхода. Внешние запросы о ВУ поступают на входы ir0,..ir7. Основные режимы работы PIC. 1) FNM (Fully Nested Mobile – Режим вложенных прерываний). В этом режиме наивысшим приоритетом обладает запрос irq0, наинизшим irq7.Допускается прерывание прерываний, это означает, что поступление на вход PIC запроса с более высоким приоритетом, чем обрабатываемый, вызывает генерацию актив уровня выходного сигнала INT, который поступает в ЦП. В регистре ISR. В регистре ISR может быть несколько установленных битов. Недостаток этого режима – достаточно сильная дискриминация запросов низшего уровня. В связи с этим, используется следующий режим. 2) ARM (Automatic Rotation Mode – Режим автоматического сдвига приоритета запросов). Приоритеты линейно упорядочены и изменяются после обработки очередного запроса таким образом, что уровень обработанного запроса становится низшим, а следующий за ним уровень – высшим.

Взаимодействие между ЦП и ведущим PIC.

a) сбрасывает бит обрабатываемого запроса в IRR; б) устанавливает бит обрабатываемого запроса в ISR; в) выставляет на внешнюю шину данных (в ее младший байт) номер обрабатываемого запроса; 6) ЦП принимает номер запроса по шине данных и модифицирует этот номер в адрес соответствующего вектора прерываний (модификация осуществляется путем умножения на 4 – сдвиг влево на 2 разряда). 7) Текущее значение регистра флагов CP и IP последовательно помещаются в стек, и тем самым сохраняется минимальный контекст прерываемой программы. 8) Два последовательных слова из таблицы векторов прерываний загружаются в регистр IP(слово по меньшему адресу) и CS (слово по большему адресу). 9) На аппаратном уровне осуществляется сброс флага IF. 10) Процессор переходит к выполнению первой команды обработчика прерываний. 5.Устройства USB: функции и хабы (состояния нисходящих портов хабов, хост-контроллер). USB (Universal Serial Bus) – универсальная последовательная шина. Архитектура USB определяется следующими критериями:

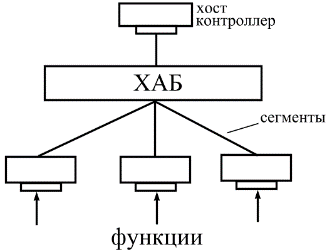

Структура USB USB обеспечивает обмен данными между хост-компьютером и множеством одновременно доступных периферийных устройств. Распределение пропускной способности шины между подключенными устройствами планируется хостом и реализуется им с помощью посылки маркеров. Устройства USB могут являться хабами, "функциями" или их комбинацией. Хаб обеспечивает дополнительные точки подключения устройств к шине. Функции USB предоставляют системе дополнительные возможности - подключение к ISDN, цифровой джойстик, акустические колонки с цифровым интерфейсом. Работой всей системы USB управляет хост-контроллер, являющийся программно-аппаратной подсистемой хост-компьютера.  Физическое соединение устройств осуществляется по топологии многоярусной звезды. Центр каждой звезды – хаб. В вершине пирамиды – хост-контроллер. Хост-контроллер интегрируется с корневым хабом (root hub), обеспечивающим точки подключения. Логически устройство, подключенное к любому хабу и сконфигурированное, может рассматриваться как подключенное напрямую к хост-контроллеру. Функции представляют собой устройства USB, способные принимать или передавать данные или управляющую информацию по шине. Функции должна быть выделена полоса в канале, выбраны специфические опции конфигурации. Примерами функций являются: Указатели - мышь, планшет, световое перо.Устройства ввода - клавиатура или сканер. Устройство вывода - принтер, звуковые колонки (цифровые). Телефонный адаптер ISDN. Хаб может распознать подключение или отключение устройств к этим портам и управлять подачей питания на их сегменты. Хаб обеспечивает изоляцию сегментов с низкой скоростью от высокоскоростных. Используется диффер способ передачи сигналов D+ и D- по двум проводам. Лог 0 – < 0,3 В, лог 1 – > 2,8 В. Приемники выдерживают вх напряжение в пределах - 0,5...+3,8 В. Передатчики должны уметь переходить в высокоимпедансное состояние для двунаправленной полудуплексной передачи по одной паре проводов. Дифференц или линейный приемник сигналов D+ и D-, передатчики этих линий управляются индивидуально. Шина имеет два режима передачи. Полная скорость передачи сигналов USB составляет 12 Мбит/с, низкая - 1,5 Мбит/с. Для полной скорости используется экранированная витая пара с импедансом 90 Ом и длиной сегмента до 5 м, для низкой - невитой неэкранированный кабель до 3 м. Разъемы типа "А" – для подключения к хабам. Вилки устанавливаются на кабелях, не отсоединяемых от устройств (клавиатура, мышь). Разъемы типа "В" устанавливаются на устройствах, от которых соединительный кабель может отсоединяться (принтеры и сканеры). Ответная часть (вилка) устанавливается на соединительном кабеле, противоположный конец которого имеет вилку типа "А". Конструкция разъемов обеспечивает позднее соединение и раннее отсоединение сигнальных цепей по сравнению с питающими. Модель передачи данных Каждое устройство USB представляет собой несколько независимых конечных точек, с которыми хост-контроллер может обмениваться информацией. Каждое устройство обязательно имеет конечную точку с номером 0, используемую для инициализации и общего управления логическим устройством, а так же опроса его состояния. Канал (pipe) - модель передачи данных между хост-контроллером и конечной точкой устройства. Имеются два типа каналов - потоки и сообщения. Поток доставляет данные от одного конца канала к другому, он всегда однонаправленный. Доставка всегда идет в порядке FIFO. Сообщения: хост отсылает запрос к конечной точке, после которого передается или принимается поток сообщения, за которым следует пакет с информацией о состоянии конечной точки. USB поддерживает как однонаправленные, так и двунаправленные режимы связи. Типы передачи данных: 1. Управляющие посылки – используются для конфигурирования при подключения и в процессе работы для управления устройствами. Обеспечивает гарантированную доставку данных. Длина поля данных управляющей посылки не превышает 64 байт для полной скорости и 8 байт для низкой. 2. Сплошные передачи сравнительно больших пакетов. Занимают всю свободную полосу пропускания шины не занятую другими классами передач. Пакеты имеют поле данных размером 8, 16, 32 или 64 байт. Приоритет этих передач самый низкий. 3. Прерывания – короткие (до 64 байт на полной скорости и до 8 на низкой) передачи типа вводимых символов или координат. 4. Изохронные передачи - непрерывные передачи в реальном времени, занимающие предварительно согласованную часть пропускной способности шины и имеющие заданную задержку доставки. Архитектура USB предусматривает внутреннюю буферизацию всех устройств. Протокол Транзакции по USB состоят из трех пакетов. Каждая транзакция планируется и начинается по инициативе контроллера, который посылает пакет-маркер, который описывает тип и направление передачи, адрес устройства и номер конечной точки. Устройство USB распознает свой адрес и подготавливается к обмену. Источник данных передает пакет данных (или уведомление об отсутствии данных). После успешного приема пакета приемник посылает пакет подтверждения приема информации. Нумерация устройств шины явл постоянным процессом отслеж-щим динамические изменения физ топологии. Хост определяет, является подключенное устройство хабом или функцией и назначает ему уникальные адрес USB. Хост устанавливает с этим устройством канал управления используя назначенный адрес и нулевой номер точки назначения. Когда устройство отключается, хаб автоматически запрещает использование соответствующего порта и сообщает об отключении контроллеру. Подключенному устройству позволяется потреблять от шины ток питания в пределах 100 мА. Рабочий ток не должен превышать 500 мА. Хост-компьютер общается с устройствами через контроллер. Хост имеет следующие обязанности:

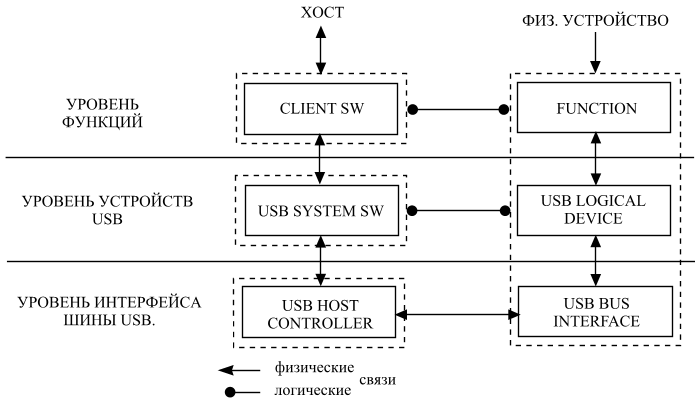

Для соединения USB шины и ПУ устройств используется 4-жильный кабель: 2 нити питания +5В и 2 нити для передачи дифференциального сигнала +D/-D. Система USB обеспечивает обмен данными между хост контроллером и множеством одновременно-доступных периферийных устройств. Распределение пропускной способности между ПУ осуществляется хост компьютером (этот же хост компьютер позволяет производить горячее подключение/отключение ПУ от системы. Система USB делится на 3 уровня с определёнными правилами межуровнего взаимодействия:  Каждая часть ответственна за опред круг задач: Client SW – ПО, соответствующее конкретному устройству и исполняемому на хост компьютере (может быть частью ОС либо драйвером); USB system SW – поддержка USB со стороны ОС, не зависимое от конкретного устройства и client SW; USB host controller – аппаратные программные средства, обеспечивающие подключение USB устройств и хост компьютера. 6.Основные принципы построения вычислительных систем. Многопроцессорные и многомашинные вычислительные системы. Вычислительные сети. Классификация вычислительных сетей. Вычислительные системы – это совокупность взаимосвязанных или взаимодействующих микропроцессоров или ЭВМ, периферийное оборудование и ПО, предназначенных для автоматизации, приёма, обработки, хранения и выдачи информации, ориентированные на получение сверхвысокой производительности и высокой надёжности средств вычислительной техники. ВС м\б построена на основе : многопроцессорной системы; многомашинной структуры; распределённых сетей. Объединение производится в целях уменьшения времени, необходимого для решения какой-либо конкретной задачи: задача расчленяется на модули, каждый из которых может быть решён на отдельном процессоре, а значит, работа идёт параллельно. После обработки все рез-ты собираются вместе и анализируются.

Создание многопроцессорных/многомашинных систем повышает надёжность решения поставленной задачи. В таких системах может быть использовано горячее резервирование: одна и та же задача паралл решается на нескольких машинах. При совпадении рез-тов, конечный ответ считается достаточно достоверным. Принципы построения ВС. Обеспечение:

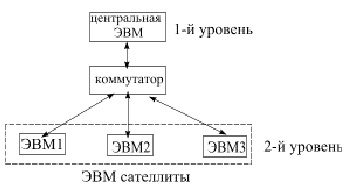

Классификация ВС.  1) по назначению: универсальные (для решения любых типов задач); специализированные (предназначены для решения задач определённого типа, что отражено в изменении общей структуры системы – появляются специализированные блоки); 2) по типу комплектующих: неоднородные системы однородные системы (используются однотипные процессоры/ЭВМ); недостатком является использование загрузки отдельных типов ЭВМ или процессоров используют неоднородные. Центральная ЭВМ более мощная осуществляет обработку информации слабых ЭВМ (1,2,3), которые осуществляют ввод, вывод данных, предварительную обработку и передачу в центральную ЭВМ посредством коммутатора. ВС с иерархической структурой могут иметь и более двух уровней иерархии. 3) по типу структуры

4) по степени территориальной разобщённости:

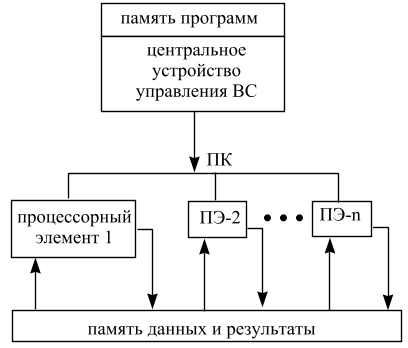

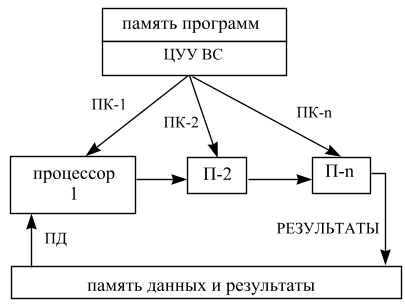

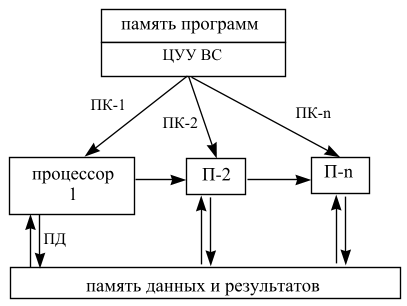

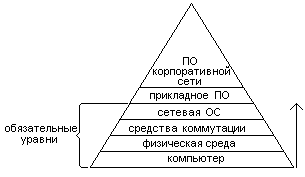

5) по степени централизации управления централизованные - все управляющие функции содержатся в одном элементе ЦП или центральном ЭВМ децентрализованные - каждый процессор или ЭВМ действуют автономно, решая свои задачи смешанное управление. ВС разбивается на группы взаимодействующих ЭВМ или процессоров, в каждом из которых осуществляется централизованное управление, а между группами децентрализованное. Структура ВС.  1) Однопроцессорная ЭВМ. В такой ЭВМ Одинарный Поток Команд и Одинарный Поток Данных. ОКОД Используется принцип последовательной обработки данных, а значит необходимо мультиплексирование во времени выполнения программ; происходит разделение ресурсов и оборудования (АЛУ в каждый момент времени выполняет только одну программу). Производительность такой системы не очень высокая, хотя для выполнения пользовательских задач этого может быть достаточно.  2). Многопроцессорная система (Одинарный Поток Команд и Множественный Поток Данных); ОКМД ПЭ представляют собой идентичные быстродействующие процессоры, имеющие память небольшой ёмкости. Они выполняют операции параллельно над разными потоками данных, но под управлением одного потока команд (паралл во времени выполняется одна и та же команда, но над разными потоками данных). В данных системах реализуется синхронный паралл вычислительный процесс. Благодаря распараллел задач, производительность системы повышена. 3) Система МКОД. (Множественный Поток Команд и Общий Поток Данных) Все процессоры находятся в конвеере. Образуется регулярная структура из последовательно включенных процессоров. Реализуется принцип магистральной обработки, каждый этап реализуется на отдельном процессоре. Поток данных поступает на вход конвеера, каждый процессор решает свою часть задачи. Результат выполнения поступает на вход следующего процессора. К каждому процессору подводится свой поток команд. После выполнения свой части задачи, процессор не простаивает, а выполняет какую-нибудь дополнительную работу.  ОКМД и МКОД строятся как матричные ВС, обладающие высоким быстродействием и экономичностью в использовании ресурсов и времени. Недостаток – невысокая надёжность работы систем такого типа, т.к. процессоры включены в цепь последовательно = > при сбое 1 процессора, рушится вся вычислительная цепь. 4). Системы МКМД.  Такие системы наиболее распространены на практике. Из памяти программ через ЦУУ ВС на каждый процессор поступают свои команды => каждый процессор выполняет свой участок сложной программы с собственными данными. По такой архитектуре могут строиться как многопроцессорные, так и многомашинные системы. Вывод: Многопроцессорные системы по сравнению с многомашинными осуществляют более быстрый обмен информацией между процессорами через общую оперативную память. Поэтому получают более высокую производительность, более быструю реакцию на возникающие внутри системы и во внешней среде ситуации, обладают более высокой надежностью и живучестью, так как система работоспособна, пока работоспособен хотя бы один модуль, каждого типа устройства. Однако построение многомашинных систем проще, так как применяются серийные ЭВМ со стандартными ОС. Вычислительные сети - частный случай распределенных систем Компьютерные сети относятся к распределенным (или децентрализованным) вычислительным системам. Поскольку основным признаком распределенной вычислительной системы является наличие нескольких центров обработки данных, то наряду с компьютерными сетями к распределенным системам относят также мультипроцессорные компьютеры и многомашинные вычислительные комплексы. Многомашинная система - это вычислительный комплекс, включающий в себя несколько компьютеров (каждый из которых работает под управлением собственной операционной системы), а также прогр и аппар средства связи компьютеров, которые обеспечивают работу всех компьютеров комплекса как единого целого. Работа любой многомашинной системы определяется двумя главными компонентами: высокоскоростным механизмом связи процессоров и системным программным обеспечением, которое предоставляет пользователям и приложениям прозрачный доступ к ресурсам всех компьютеров, входящих в комплекс. В состав средств связи входят программные модули, которые занимаются распределением вычислительной нагрузки, синхронизацией вычислений и реконфигурацией системы. Если происходит отказ одного из компьютеров комплекса, его задачи могут быть автоматически переназначены и выполнены на другом компьютере. Если в состав многомашинной системы входят несколько контроллеров внешних устройств, то в случае отказа одного из них, другие контроллеры автоматически подхватывают его работу. Таким образом, достигается высокая отказоустойчивость комплекса в целом. Помимо повышения отказоустойчивости, многомашинные системы позволяют достичь высокой производительности за счет организации параллельных вычислений. По сравнению с мультипроцессорными системами возможности параллельной обработки в многомашинных системах ограничены: эффективность распараллеливания резко снижается, если параллельно выполняемые задачи тесно связаны между собой по данным. Это объясняется тем, что связь между компьютерами многомашинной системы менее тесная, чем между процессорами в мультипроцессорной системе, так как основной обмен данными осуществляется через общие многовходовые периферийные устройства. Говорят, что в отличие от мультипроцессоров, где используются сильные программные и аппаратные связи, в многомашинных системах аппаратные и программные связи между обрабатывающими устройствами являются более слабыми. Территориальная распределенность в многомашинных комплексах не обеспечивается, так как расстояния между компьютерами определяются длиной связи между процессорным блоком и дисковой подсистемой. Вычислительные сети В вычислительных сетях программные и аппаратные связи являются еще более слабыми, а автономность обрабатывающих блоков проявляется в наибольшей степени - основными элементами сети являются стандартные компьютеры, не имеющие ни общих блоков памяти, ни общих периферийных устройств. Связь между компьютерами осуществляется с помощью специальных периферийных устройств - сетевых адаптеров, соединенных относительно протяженными каналами связи. Каждый компьютер работает под управлением собственной операционной системы, а какая-либо «общая» операционная система, распределяющая работу между компьютерами сети, отсутствует. Взаимодействие между компьютерами сети происходит за счет передачи сообщений через сетевые адаптеры и каналы связи. С помощью этих сообщений один компьютер обычно запрашивает доступ к локальным ресурсам другого компьютера. Такими ресурсами могут быть как данные, хранящиеся на диске, так и разнообразные периферийные устройства - принтеры, модемы, факс-аппараты и т. д. Разделение локальных ресурсов каждого компьютера между всеми пользователями сети - основная цель создания вычислительной сети. Классификация сетей. Вычислительные сети классифицируются по ряду признаков. В зависимости от расстояний между связываемыми узлами различают вычислительные сети: Территориальные, локальные (ЛВС), корпоративные (масштаба предприятия). Среди ЛВС наиболее распространены : шинная (bus) , кольцевая (ring) звездная (star). 7. Стандарты сетевых технологий. Технология клиент-сервер. Модель ISO/OSI уровни: физический, канальный, сетевой, сеансовый, транспортный, представительский и прикладной Возможность создания сетей появилась только после появления стандартов коммутаций. Вычислительная сеть является одним из случаев распределенных информационных систем, обладающая набором средств для физической и логической передачи информации, а также свойствами: 1) отказоустойчивость; 2) прозрачность для пользователей; 3) низкая стоимость обслуживания. Базис технологий ЛВС основывается на технологии клиент-сервер. ЛВС состоит из ПК, объединенных по средствам каналов связи. Каждый компьютер в сети называется узлом. Каждый узел может либо предоставлять свои ресурсы для узлов (сервер), либо являться потребителем ресурсов другого узла (клиент). Служба – набор программ, обеспечивающий совместный доступ к данным на данном узле сети. Сервис – описывает набор услуг, предоставляемых данными службами. Возникновение корпорат сетей привело к соединению ЛВС и ГВС.  Физическая среда: каналы передачи данных, принципы кодирования информации, стандарты, принципы коммутации, методы расчета пропускной способности среды. Средства коммутации: коммутаторы, концентраторы, шлюзы, а также протоколы передачи информации. Сетевые ОС – это ОС, в которых присутствуют службы и сервисы, необходимые для организации клиент-серверной архитектуры. Прикладное ПО – программы, отвечающие за организацию работы пользователя в рамках вычислительной сети, но не являющиеся частью ОС (системы обмена сообщениями в сети, почтовые программы, браузеры, системы передачи речи и видеосигналов). ПО корпоративной сети – ориентированно на достижение цели организации в рамках ее деятельности. Является специализированным и разрабатывается по индивидуальному заказу. Протокол – это формализованные правила, опред посл-ть и формат сообщ, которыми обмениваются сетевые компоненты, принадлежащие к одному и тому же уровню модели, но находящиеся на различных узлах сети. Интерфейс – это формализованные правила, определяющие вз\действие сетевых компонентов соседних уровней одного узла. Интерфейс определяет набор сервисов, предоставляемых данным ур для соседних уровней. Стек коммуникационных протоколов – иерархический набор протоколов, достаточный для организации взаимодействия узлов в сети. Сеть состоит из огромного числа различных модулей - компьютеров, средств коммутации, ОС и модулей приложений. Разнообразие выпускаемых для построения сетей устройств и программ. Все компоненты сети должны работать согласованно – необходимо принятие стандартов, которые гарантировали бы совместимость различного оборудования и программ. Большинство принимаемых стандартов носят открытый характер. Возможность вз\действия с продуктами конкурентов повышает ценность изделия, так как его можно применить в большем кол-ве работающих сетей. Совместимость достигается только после того, как все производители реализуют стандарт в своих изделиях одинаковым образом. Источники стандартов

Организации, занимающиеся разработкой стандартов:

Протоколы и стандарты. Режим TDM – совместное использ кабелей всеми ПК сети в режиме разделения времени. Режим АТМ – конечные узлы присоед-ся индивидуальными линиями связи к коммутаторам. 2 режима работы: полудуплексный, полнодуплексный. Структура стандартов IEEE 802.X. Содержит рекомендации по проектированию нижних уровней LAN (физического и канального). Канальный уровень делится в локальных сетях на два подуровня:

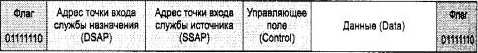

Уровень MAC обеспечивает корректное совместное использование общей, разделяемой среды (Ethernet, Fast Ethernet, Gigabit Ethernet, Token Ring, FDDI, l00VG-AnyLAN). Уровень LLC отвечает за передачу кадров данных между узлами с различной степенью надежности, реализует функции интерфейса с сетевым уровнем. Комитет 802 включает подкомитеты: 802.1 - объединение сетей; 802.2 - LLC - управление логической передачей данных; 802.3 - Ethernet с методом доступа CSMA/CD; 802.4 - Token Bus LAN - локальные сети с методом доступа Token Bus; 802.5 - Token Ring LAN - локальные сети с методом доступа Token Ring; 802.6 - MAN - сети мегаполисов; 802.7 - техническая консультационная группа по широкополосной передаче; 802,8 - техническая консультационная группа по волоконно-оптическим сетям; 802.9 - интегрированные сети передачи голоса и данных; 802.10 - сетевая безопасность; 802.11 - беспроводные сети; 802.12 - LAN с методом доступа по требованию с приоритетами (l00VG-AnyLAN). 802.ID - описывает логику работы моста/коммутатора; 802.1Н - определяет работу транслирующего моста; 802.1Q - определяет способ построения виртуальных VLAN на основе коммутаторов. Протокол LLC уровня. Протокол LLC обеспечивает для LAN нужное качество услуг транспортной службы, передавая свои кадры либо дейтаграммным способом, либо с помощью процедур с установлением соединения и восстановлением кадров. Структура кадров LLC.  Флаги определяют границы кадра LLC. Кадр LLC содержит поле данных и заголовок, который состоит из трех полей:

Клиент-сервер. ЛВС состоит из ПК, объединенных по средствам каналов связи. Каждый компьютер в сети называется узлом. Каждый узел может либо предоставлять свои ресурсы для узлов (сервер), либо являться потребителем ресурсов другого узла (клиент). Стандартные стеки коммуникационных протоколов Стек OSI – набор конкретных спецификаций протоколов для всех семи уровней взаимодействия. Полностью соответствует модели OSI. На нижних уровнях стек OSI поддерживает Ethernet, Token Ring, FDDI, протоколы глобальных сетей. Протоколы сетевого, транспортного и сеансового уровней стека OSI реализованы различными производителями, но распространены мало. Протокол передачи файлов FTAM, протокол эмуляции терминала VTP, протоколы электронной почты Х.400. «–» большая сложность и неоднозначность спецификаций, стремление учесть все случаи жизни и все существующие и появляющиеся технологии. требуют больших затрат выч мощности центрального процессора. Стек TCP/IP – протоколы IP и TCP, относятся к сетевому и транспортному уровням соответственно. IP обеспечивает продвижение пакета по составной сети, а TCP гарантирует надежность его доставки. Используется для связи компьютеров сети Internet, и в огромном числе корпоративных сетей. Поддерживает стандарты физического и канального уровней: для локальных сетей – Ethernet, Token Ring, FDDI, для глобальных – протоколы работы на аналоговых коммутируемых и выделенных линиях SLIP, РРР, протоколы территориальных сетей Х.25 и ISDN. Протоколы прикл уровня – протокол пересылки файлов FTP, протокол эмуляции терминала telnet, почтовый протокол SMTP, используемый в электронной почте сети Internet, гипертекстовые сервисы службы WWW. Способность фрагментировать пакеты – в каждой сети – собственная величина макс длины кадра – при переходе из одной сети в другую м возникнуть необходимость деления передаваемого кадра на несколько частей. «+» гибкая система адресации. экономно используются возможности широковещательных рассылок. «–» высокие требования к ресурсам и сложность администрирования IP-сетей. наличие в IP-сети различных централизованных служб типа DNS, DHCP и т. п. Стек IPX/SPX – протоколы стека IPX/SPX до недавнего времени хорошо работали в локальных сетях и не очень - в больших корпоративных сетях, так как они слишком перегружали медленные глобальные связи широковещательными пакетами, которые интенсивно используются несколькими протоколами этого стека (например, для установления связи между клиентами и серверами). NetWare, UNIX, Sun Solaris, Microsoft Windows NT. Стек NetBIOS/SMB– появился как сетевое расширение стандартных функций BIOS На физическом и канальном уровнях использ – протоколы Ethernet, Token Ring, FDDI. На верхних уровнях работают протоколы NetBEUI и SMB. NetBEUI - NetBIOS Extended User Interface – протокол, потребляющий немного ресурсов и предназначенный для сетей, насчитывающих не более 200 рабочих станций. Содержит функции сетевого, транспортного и сеансового уровней, но невозможна маршрутизация пакетов. Протокол SMB (Server Message Block) выполняет функции сеансового, представительного и прикладного уровней. На основе SMB реализуется файловая служба, службы печати и передачи сообщений между приложениями. |