Модуль 3. 1. Память эвм, ее характеристики. Структура памяти. Постоянные запоминающие устройства (программируемые маской, перепрограммируемые eprom, eeprom). Оперативные запоминающие устройства статического и динамического типов. Стек. Виртуальная память

Скачать 2.32 Mb. Скачать 2.32 Mb.

|

|

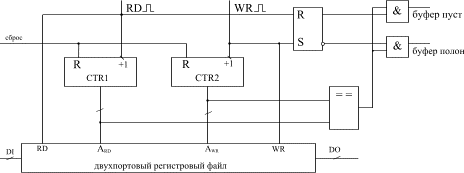

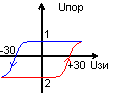

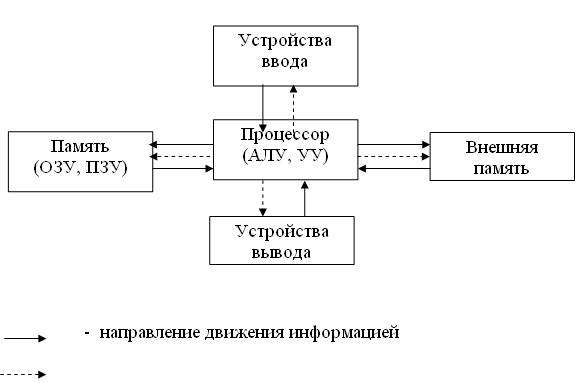

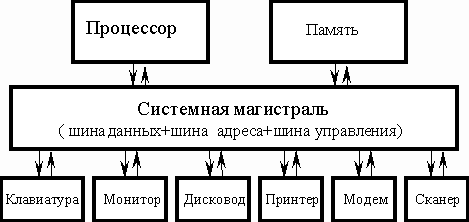

2.Буфер FIFO. Кэш память. FLASH. FLASH с несимметричной блочной структурой. Параметры. Устройство, хранение и считывание о и хранение информациильной обратной связью на логических элементах. FIFO. Буфер FIFO. Представляет собой ЗУ для хранения очередей данных (списков) с порядком выборки слов, таким же, что и порядок их поступления. Интервалы между словами могут быть различными, так как моменты записи и чтения из буфера задаются внешними сигналами управления независимо друг от друга. Разный темп приёма и выдачи слов необходим, например, если приёмник способен принимать данные, поступающие с некоторой частотой, а источник выдает слова в более высоком темпе, и возможно нерегулярно. Такие данные поступают в буфер FIFO, а из него считываются с необходимой приёмнику частотой. Новое слово ставится в конец очереди, считывание осуществляется с начала очереди.  В схеме перед началом работы оба счётчика адресов CTR1 и CTR2 сбрасываются. При записи адреса увеличиваются на единицу при каждом обращении, то есть возрастают начиная с нулевого. То же происходит при чтении слов, так что адрес чтения гонится за адресом записи. Если адреса сравниваются при чтении – буфер пуст, если при записи - буфер полон (адресами занята вся емкость счетчика). Возникновение этих ситуаций отмечается соответствующими сигналами. Очередь удлиняется или укорачивается в зависимости от разности чисел записанных и считанных слов. Переход через ноль осложнений не вызывает. FIFO-буферы СОМ-портов, и несколькомегабайтные кэш-буфе ры высокопроизводительных устройств хранения, видеопамять. Кэш память. Для обеспечения быстрого доступа к оперативной памяти, сокращения времени простаивания процессора и увеличения быстродействия используется кэш-память или «сверхоперативная память» небольшого объёма. Кэш память располагается «между» микропроцессором и оперативной памятью. Кэш память реализуется на триггерных элементах памяти. В памяти этого типа поиск нужной информации производится не по адресу, а по ее содержанию (по ассоциативному признаку). При этом поиск по ассоциативному признаку (или последовательно по отдельным его разрядам) происходит параллельно во времени для всех ячеек запоминающего массива. Во многих случаях ассоциативный поиск позволяет существенно упростить и ускорить обработку данных. Это достигается за счет того, что в памяти этого типа операция считывания информации совмещена с выполнением ряда логических операций.  При чтении данных сначала выполняется обращение к кэш-памяти, если в кэше имеется копия данных адресованной ячейки основной памяти, то им вырабатывается сигнал Hit (попадание) и выдает данные на общую шину данных. Если данных в кэше нет, то они считываются из основной памяти и одновременно помещаются в кэш. 3 уровня КЭШ-памяти. Процессор обращается сначала к 1 уровню, потом ко 2, 3, затем к ОЗУ. L1-cache – самая быстрая, расположена на одном кристалле с проц-ром, состоит из кэша команд и кэша данных, работает на частоте процессора, объём обычно невелик — не более 128 КБ. L2-cache – менее быстрый, расположен либо на кристалле, либо в близи от ядра, объём от 128 КБ до 1−8 МБ. L3-cache – наименее быстродействующий, но всё равно быстрее ОЗУ, расположен отдельно от ядра, объем — более 32 МБ. Структура кэшированной памяти. Объем кэш памяти намного меньше, емкости основной памяти и любая единица информации, помещаемая в кэш, должна сопровождаться дополнительными данными (тэгом), определяющими копией какой ячейки информации основной памяти является эта единица информации. Во избежание значительного увеличения стоимости устанавливается только небольшой объем высокоскоростной памяти SRAM, которая используется в качестве кэш-памяти. Кэш-память работает на тактовых частотах, близких или даже равных тактовым частотам процессора, причем обычно именно эта память непосредственно используется процессором при чтении и записи. Чтобы минимизировать время ожидания при считывании процессором данных из медленной оперативной памяти, в современных персональных компьютерах обычно предусмотрены два типа кэш-памяти: кэш-память первого уровня (L1) и кэш-память второго уровня (L2). Кэш- память первого уровня также называется встроенным, или внутренним кэшем; он непосредственно встроен в процессор и фактически является частью микросхемы процессора. Во всех процессорах 486 и выше кэш-память первого уровня интегрирована в микросхему процессора. Кэш память второго уровня изначально устанавливалась рядом с процессором на системной плате, но в поколениях процессоров от Pentium 2/Athlon данная кэш память второго уровня стала непосредственно размещаться на кристалле процессора. В зависимости от способа определения взаимного соответствия строки кэша и области основной памяти различают три архитектуры кэш-памяти: кэш пря мого отображения (direct-mapped cache), полностью ассоциативный кэш (fully associative cache) и их комбинация — частично - или наборно-ассоциативный кэш (set-associative cache). В кэш-памяти прямого отображения адрес памяти, по которому происходит обращение, однозначно определяет строку кэша, в которой может находиться требуемый блок. Поскольку объем основной памяти много больше объема кэша, на каждую строку кэша может претендовать множество блоков памяти с одина ковой младшей частью адреса (смещением внутри страницы). Одна строка в оп ределенный момент может, естественно, содержать копию только одного из этих блоков, и информация о том, какой именно блок занимает данную строку, хранится в памяти тегов. Память тегов должна иметь количество ячеек, равное ко личеству строк кэша, а ее разрядность должна быть достаточной, чтобы вмес тить старшие биты адреса кэшируемой памяти, не попавшие на шину адреса кэш-памяти. Кроме адресной части тега с каждой строкой кэша связаны биты при знаков действительности и модифицированности данных. Независимо от объе ма затребованных данных в кэш из основной памяти строка переписывается вся целиком. Если контроллер кэша реализует упреждающее считывание (read ahead), то в последующие свободные циклы шины также обновится и следующая строка (если она была чистой). Чтение «про запас» позволяет при необходимости осу ществлять пакетный цикл чтения из кэша через границу строки. Такой кэш имеет самую простую аппаратную реализацию и применяется во вторичном кэше большинства системных плат. Однако ему присущ серьезный недостаток: если в процессе выполнения программы процессору поочередно бу дут требоваться блоки памяти, смещенные относительно друг друга на величи ну, кратную размеру страницы, то кэш будет работать интенсивно, но вхолостую (cache trashing). Увеличение размера кэша при сохранении архитектуры прямо го отображения даст не очень существенный эффект, поскольку разные задачи будут претендовать на одни и те же строки кэша. Объем кэшируемой памяти (MCACHED) при архитектуре прямого отображения определяется объемом кэш-па мяти (VCACHE) и разрядностью памяти тегов (N): MCACHED = VCACHE x 2N. Так, для кэша размером 256 Кбайт и 8-битной памятью тегов (типичный вариант для си стемных плат с сокетами 5 и 7) объем кэшируемой памяти составит mcached ш256 кбайт х 28 - 64 Мбайт. Наборно-ассоциативная архитектура кэша позволяет каждому блоку квити руемой памяти претендовать на одну из нескольких строк кэша, объединенных в набор (set). Можно считать, что в этой архитектуре есть несколько параллельно и согласованно работающих каналов (банков) прямого отображения, где кон троллеру кэша приходится принимать решение о том, в какую из строк набора помещать очередной блок данных. В простейшем случае каждый блок памяти может помещаться в одну из двух строк (Two Way Set-Associative Cache — двух-канальный наборно-ассоциативный кэш). Наборно-ассоциативная архитектура широко применяется для первичного кэша современных процессоров. Объем кэшируемой памяти определяется так же, как и в предыдущем варианте, но здесь фигурируют объем одного банка (а не всего кэша) и разрядность относящихся к нему ячеек тега. В отличие от предыдущих у полностью ассоциативного кэша любая его стро ка может отображать любой блок памяти, что существенно повышает эффектив ность использования его ограниченного объема. Его реализация является слож ной аппаратной задачей, которая пока решена только для небольших объемов первичного кэша в некоторых процессорах. Применение полностью ассоциатив ной архитектуры во вторичном кэше пока не предвидится. FLASH память. Флэш-память относится к классу EEPROM, но использует особую технологию построения запоминающих ячеек. Стирание во флэш-памяти производится сразу для целой области ячеек (блоками или полностью всей микросхемы). Это позволило существенно повысить производительность в режиме записи (программирования). Флэш-память обладает сочетанием высокой плотности упаковки (ее ячейки на 30% меньше ячеек DRAM), энергонезависимого хранения, электрического стирания и записи, низкого потребления, высокой надежности и невысокой стоимости...Это репрограммируемые ЗУ. Подобно ОЗУ, флэш-память модифицируется электрически внутрисистемно, но подобно ПЗУ, флэш энергонезависима и хранит данные даже после отключения питания. Однако, в отличие от ОЗУ, флэш нельзя переписывать побайтно. Флэш-память читается и записывается байт за байтом и предъявляет новое требование: ее нужно стереть перед тем, как записывать новые данные. Флэш-память - это полупроводниковая память, причем особого типа. Ее элементарная ячейка, в которой хранится один бит информации, представляет собой не конденсатор, а полевой транзистор со специальной электрически изолированной областью, которую называют "плавающим затвором". Электрический заряд, помещенный в эту область, способен сохраняться в течение многих лет. При записи одного бита данных ячейка заряжается - заряд помещается на плавающий затвор, при стирании - заряд снимается с плавающего затвора и ячейка разряжается. Выделяют среди таких устройств схемы со специализированными блоками (несимметричные блочные структуры). По имени так называемых Boot блоков в которых информация надежно защищена от случайного стирания, ЗУ называются BootBlockFlashMemory. Флэш-память типа Boot Block служит для хранения обновляемых программ и данных в самых разных системах, включая сотовые телефоны, модемы, BIOS, системы управления автомобильными двигателями и многое другое. Используя флэш-память вместо EEPROM для хранения параметрических данных, разработчики добиваются снижения стоимости и повышения надежности своих систем. Преимущества флэш-памяти по сравнению с EEPROM: 1. Более высокая скорость записи при последовательном доступе за счёт того, что стирание информации во флэш производится блоками. 2. Себестоимость производства флэш-памяти ниже за счёт более простой организации. Недостаток: Медленная запись в произвольные участки памяти. Память с последовательным доступом Используются, где данные могут быть выстроены в очередь. Флэш-память с адресным доступом. Хранение редко изменяемых данных. Запись и стирание осу ществляет процессор выч устр-ва в обычном рабочем режиме. Для этого Флэш-память имеет дополнительное управление словами-командами, записывае мыми процессором в специальный регистр микросхемы. При подаче специального напряжения программирования схема обеспечивает запись и стирание информации. Перед программировани ем процессор считывает из микросхемы код - идентификатор, содержащий код фирмы-изготовителя и микросхемы для согласования алгоритмов стирания и записи, автоматически. Стираются все байты памя ти или выбранного блока, после чего все они проверяются, выполняется повторное стирание и проверка. Программирование памяти ведется байт за байтом, записанная информация проверяется. Процессор счи тывает из ЗУ записанный байт и сравнивает его с исходным. Один из блоков предназначен для хранения ПО BIOS и аппаратно защищен от случайного стирания. В ЗУ есть также блоки парамет ров и главные блоки, не защищенные от случайного стирания. Главные блоки хранят основные управляющие программы, а бло ки параметров - относительно часто меняемые параметры систе мы. Файловая Флэш-память применяется для замены твердых дис ков. Сокращает потребляемую мощность, повышает надежность ЗУ, уменьшает их размеры и вес, повышает быстродействие при чтении данных. Программа может читаться процессором непосредственно из файловой Флэш-памяти, туда же записываются и результаты.  На основе файловой Флэш-памяти создаются компактные съемные внешние ЗУ. ЗЭ – МНОП. 2 пороговых напр-ия. Uпор1 – имеет маленькую величину, 1-2 В. При подаче Uпор инициируется канал м/д стоком-истоком. Если м/д нитридом и двуокисью кремния есть заряды, то Uпор увеличилось до 7В. Запись (программирование) флеш-памяти – процесс замены 1 на 0. Стирание – замена 0 на 1. 3.Архитектура РС. Процессоры ЭВМ. Структура процессоров и их основные характеристики. Системные шины и их характеристики. Локальные шины. Чипсеты. Архитектура – это многоуровневая иерархия аппаратно-программных средств, каждый из уровней допускает многовариантное построение и применение. Структура – это совокупность элементов и их связей. ЭВМ – это комплекс технических и программных средств, предназначенный для автоматизации подготовки и решения задач пользователей. Архитектура ЭВМ - это общее описание структуры и функций ЭВМ на уровне, достаточном для понимания принципов работы и системы команд ЭВМ, не включающее деталей технического и физического устройства компьютера.  К архитектуре относятся следующие принципы построения ЭВМ: 1. структура памяти ЭВМ; 2. способы доступа к памяти и внешним устройствам; 3. возможность изменения конфигурации; 4. система команд; 5. форматы данных; 6. организация интерфейса. Архитектура современных персональных компьютеров основана на магистрально-модульном принципе. Информационная связь между устройствами компьютера осуществляется через системную шину (другое название - системная магистраль). Шина - это кабель, состоящий из множества проводников. По одной группе проводников - шине данных передаётся обрабатываемая информация, по другой - шине адреса - адреса памяти или внешних устройств, к которым обращается процессор. Третья часть магистрали - шина управления, по ней передаются управляющие сигналы (например, сигнал готовности устройства к работе, сигнал к началу работы устройства и др). Системная шина характеризуется тактовой частотой и разрядностью. Количество одновременно передаваемых по шине бит называется разрядностью шины. Тактовая частота характеризует число элементарных операций по передаче данных в 1 секунду. Разрядность шины измеряется в битах, тактовая частота – в мегагерцах. Системные шины Переда ча информации между МП и осталь ными элементами. Осуществляется также адресация устройств и обмен специальными служебными сигналами. Передачей информации по шине управляет одно из подключенных к ней устройств или специально выделенный для этого узел, называемый ар битром шины. Шина ISA (Industry Standard Architecture) есть 36-контактный разъем для плат расширения. За счет этого количество адресных линий – 4, а данных – 8. Можно передавать параллельно 16 разрядов данных, а благодаря 24 адресным линиям напрямую обращаться к 16 МБ сист памяти. Кол-во линий аппаратных прерываний - 15. Шина EISA (Extended ISA). обеспечивает наи больший возможный объем адресуемой памяти, 32-разрядную передачу данных, улучшенную систему прерываний, автоматическую конфи гурацию системы и плат расширения. В EISA-разъем на системной плате компьютера совместим с ISA. Шина EISA позволяет адресовать 4Гб адресного про ст-ва. Теор максимальная скорость 33 Мбайт/с. Шина тактируется частотой около 8—10 МГц. Локальные шины предназначены для увеличения быстродействия компа, позволяя периферийным устройствам (видеоадаптеры, контроллеры накопителей) работать с тактовой частотой до 33 МГц и выще. Используется разъем типа MCA. Шины PCI. Между локальной шиной процессора и самой PCI находится специальная согласующая м\схема В соответствии со спецификацией PCI к шине могут подклю чаться до 10 устройств. Шина PCI работает на фиксированной тактовой часто те 33 МГц и предусматривает напряжение питания для контрол леров как 5, так и 3,3 В, режим plug and play. Шина PCI-X – высокопроизводительная PCI. является синхронной, т.е. все данные обрабатываются одновременно при поступлении управляющего сигнала. Разрядность шины 32-бита. При частоте 33 МГц теоретическая пропускная способность 132 МБ/с. Всякая информация, передаваемая от процессора к другим устройствам по шине данных, сопровождается адресом, передаваемым по адресной шине. Это может быть адрес ячейки памяти или адрес периферийного устройства. Необходимо, чтобы разрядность шины позволила передать адрес ячейки памяти. Таким образом, словами разрядность шины ограничивает объем оперативной памяти ЭВМ, он не может быть больше чем  схема устройства компьютера, построенного по магистральному принципу |