a) a) б)

Недостатком параллельных многоразрядных сумматоров с последовательным переносом является их сравнительно низкое быстродействие, связанное с большим временем суммирования. Увеличение быстродействия сумматоров можно осуществить по двум направлениям :

1) уменьшением параметров tas, tap, tps, tpp и объема оборудования, оцениваемого числом входов используемых ЛЭ;

2) уменьшением времени суммирования tсум .

Первое направление представляет собой классическую задачу синтеза сумматора, не решенную окончательно до настоящего времени. За время существования ЭВМ эта задача решалась эмпирически и были получены удачные решения. В настоящее время широкое распространение получили сумматоры, построенные на основании уравнений (15.5) и (15.8), представляющих самодвойственные функции.

Второе направление связано с уменьшением ( или даже исключением ) влияния разрядности суммируемых чисел на tcyм путем одновременного формирования переносов во все разряды. Такие сумматоры называют параллельными с параллельным переносом. Для синтеза таких сумматоров представим выражение (15.5) для переноса в старший разряд в виде:

(15.10) (15.10)

или

где  . (15.11) . (15.11)

Сигнал gi = 1 вырабатывается тогда, когда ai = bi=1 и не зависит от значения переноса ci в данный разряд. Поэтому функцию gi = aibi называют функцией генерации переноса. Сигналpi= ai bi= 1 разрешает прохождение переноса на выход сумматора, когда ai либо bi равно нулю и называется функцией распространения переноса. bi= 1 разрешает прохождение переноса на выход сумматора, когда ai либо bi равно нулю и называется функцией распространения переноса.

Для четырехразрядного сумматора функции генерации и распространения переноса будут иметь вид:

g 0 = a0 b0 , p0 = a0 b0 , 0 = a0 b0 , p0 = a0 b0 ,

g

(15.12)

1 = a1 b1 , p0 = a1 b1 , 1 = a1 b1 , p0 = a1 b1 ,

g 2 = a2 b2 , p0 = a2 b2 , 2 = a2 b2 , p0 = a2 b2 ,

g 3 = a3 b3 , p0 = a3 b3 . 3 = a3 b3 , p0 = a3 b3 .

Тогда функции переноса для первого и последующего разрядов можно записать в виде:

c 1 = g0 1 = g0  p0c0 ; p0c0 ;

(15.13)

Формулы (15.13) показывают, что переносы из каждого разряда можно выразить непосредственно через функции генерации gi и распространения переноса pi, определяемые только значениями слагаемых независимо от их положения в разрядной сетке, и перенос c0 в младший разряд.

Можно показать также, что  . Действительно: . Действительно:

Следовательно, одновременно (параллельно) с формированием сигналов переноса по сформированным значениям функций gi и pi можно формировать частичные суммы si (но небольшая задержка должна быть, чтобы успели выработаться сигналы переноса).

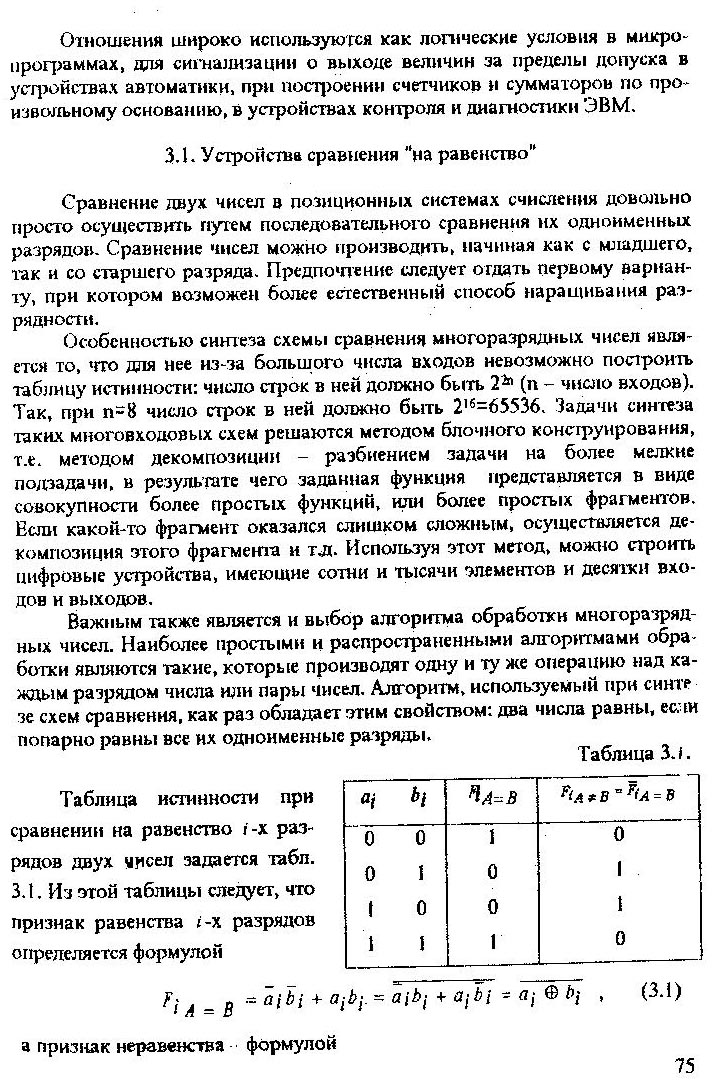

Рис.15.10

Структурная схема рассмотренного сумматора с параллельным поразрядным переносом приведена на рис. 15.10. Блок генерации и распространения совместно с блоком переноса образуют схему (блок) ускоренного переноса (сокращенно СУП или БУП).

Для реализации этого сумматора в базисе И-НЕ необходимо преобразовать уравнения (15.12) следующим образом:

(15.14)

(15.15)

П оступая аналогичным образом, получим: оступая аналогичным образом, получим:

(15.16)

(15.17)

В уравнениях (15.14)...(15.17) множители, стоящие после знака  (конъюнкции), присутствуют только в том случае, если c0=1. (конъюнкции), присутствуют только в том случае, если c0=1.

Рис.15.11

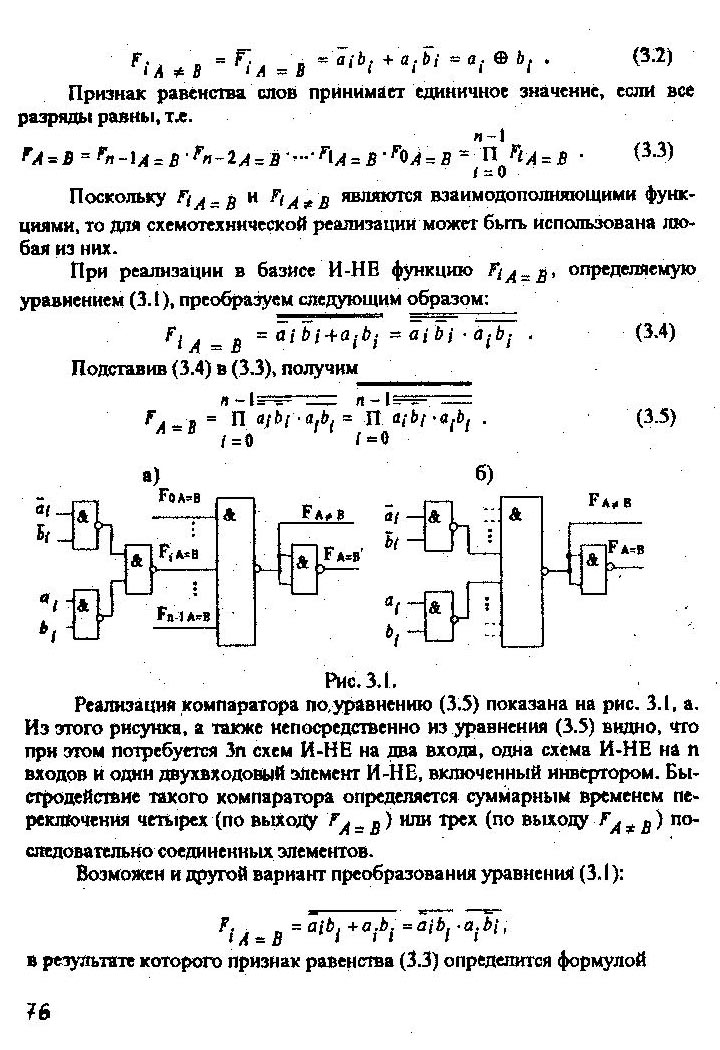

Схема четырехразрядного параллельного сумматора, построенная в соответствии с уравнениями (15.14) ... (15.17), приведена на рис.15.11. На этом рисунке пунктирными линиями обведены участки, которые не используются при c0 = 0. Из рисунка видно, что быстродействие параллельного сумматора с параллельным переносом равно времени задержки трех схем И-НЕ, формирующих сигнал переноса, плюс время задержки ПОС. В зависимости от типа одноразрядного сумматора время суммирования при параллельном переносе составляет tсум = (5-6) tзд.ла..

С ростом разрядности сумматора увеличивается число входов конъ-юнкторов, используемых для формирования переносов в старшие разряды. Поэтому сумматоры с параллельным переносом реализуют лишь для малого числа разрядов (обычно для четырех). Однако принцип параллельного переноса используется в широко распространенных сумматорах с групповой структурой.

25 Двоично-десятичные сумматоры

Эти сумматоры выполняют действия над десятичными цифрами, разряды которых закодированы двоичными тетрадами. Если при первичном суммировании тетрад результат не превышает число 9, то коррекция не нужна. Во всех остальных случаях она необходима. Если при первичном суммировании тетрад результат находится в пределах 10... 15, то сигнал переноса не вырабатывается, а полученная тетрада результата не является двоично-десятичной. В этом случае коррекция заключается в выработке сигнала переноса и одновременном уменьшении результата на 10. Вычитание из результата числа 10 можно заменить операцией прибавления к нему дополнительного кода числа 10, имеющим двоичное представление 0110, соответствующее числу 6. Таким образом в данном случае к результату нужно прибавить корректирующую поправку 6 и обеспечить сигнал переноса в старшую тетраду.

Если при первичном суммировании результат превысит число 15, то вырабатывается сигнал переноса в старшую тетраду, цена которого равна 16. Поскольку для двоично-десятичных чисел цена переноса равна 10, то к полученному результату необходимо прибавить число 6.

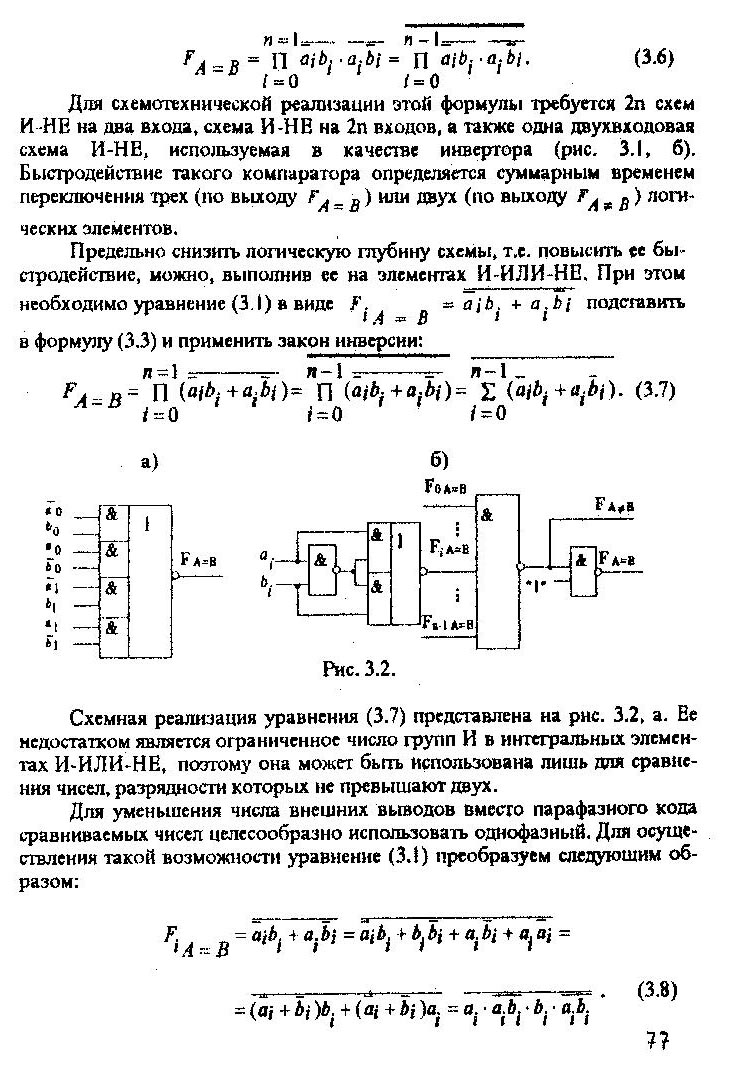

Схема двоично-десятичной тетрады показана на рис. 15.14. Она содержит сумматоры 1 и 2 и цепи коррекции. Сумматор 1 осуществляет первичное сложение двоично-десятичных тетрад a3a2a1a0 и b3b2b1b0. Коррекция результата первичного суммирования осуществляется сумматором 2, на одни входы которого подается первичное значение суммы, а на другие - корректирующая поправка 0110. При результате 10 и 11, полученном в сумматоре 1, единица переноса в старшую тетраду c1 = l образуется на выходе схемы ИЛИ благодаря конъюнктору И2, а при результате 12 и 13-благодаря конъюнктору И1. В образовании переноса c1 = l при результатах первичного суммирования, равных 14 и 15, участвуют оба конъюнктора, а при результатах, превышающих число 15, в качестве переноса с1 используется перенос с выхода переноса с4 сумматора 1. Во всех этих случаях на входы b3b2b1b0сумматора 2 поступает корректирующая поправка 0110. Из рис. 15.14 видно, что младший разряд s0 сумматора 1 передается на вход младшего разряда сумматора 2 без изменения (т.к b0 =0), поэтому сумматор 2 может быть 3-разрядным.

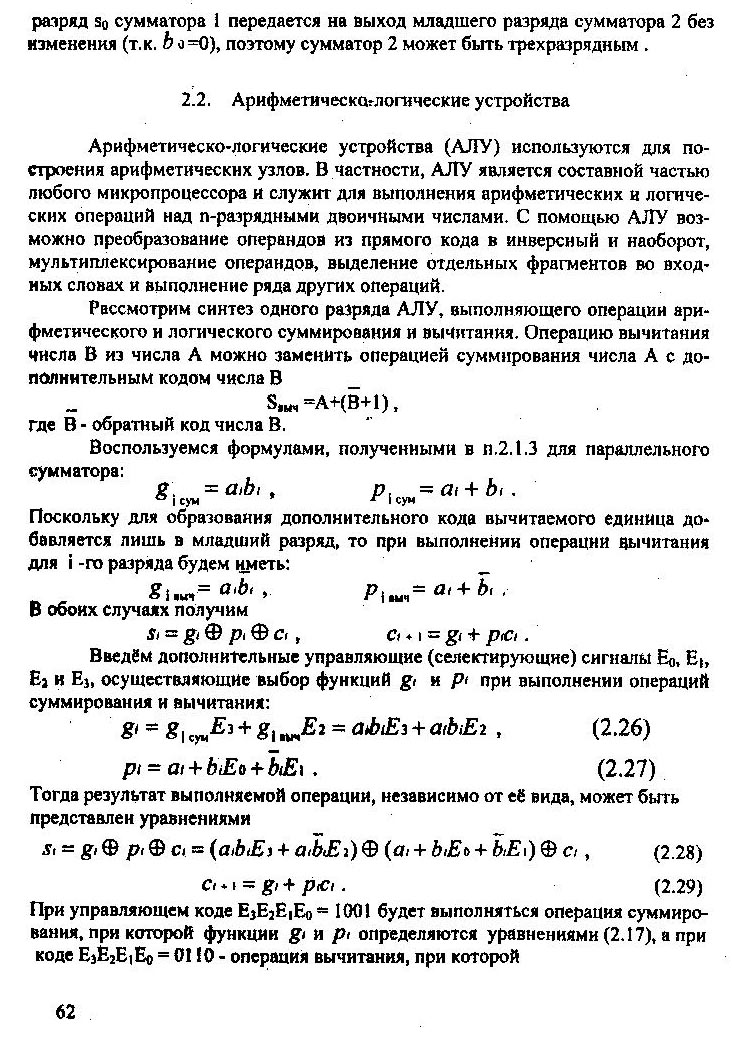

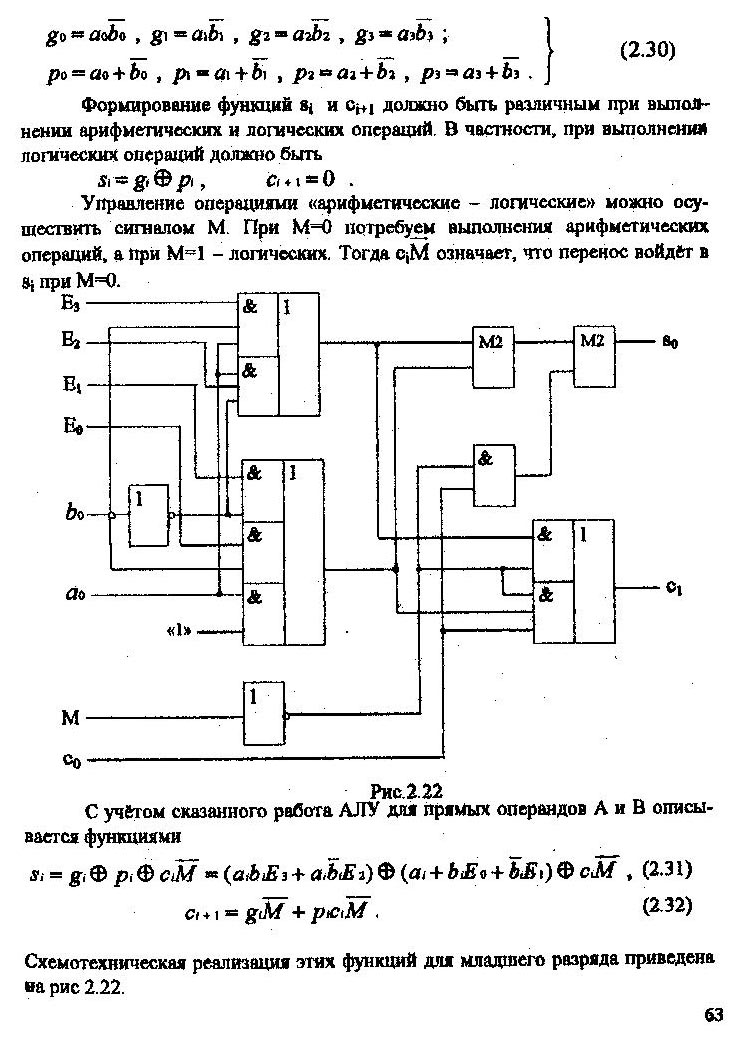

26.АЛУ

27. Схема сравнения на равенство

28. Схема сравнения на больше

29. Контроль по чётности

30. Классификация полупроводниковых БИС ЗУ

Запоминающие устройства (ЗУ) предназначены для хранения, записи и выдачи информации, необходимой для решения задач на ЭВМ. Записываемая, хранимая и считываемая информация представляется в виде слов или слогов в двоичном коде. Каждое слово (слог) располагается в ячейке памяти (ЯП), состоящей из элементов памяти (ЭП). Число ЭП в ЯП определяет разрядность ЯП и разрядность записываемого в неё слова. Конструктивно ЯП объединяются в устройство, называемое блоком памяти.

В современных ЭВМ можно выделить устройства внутренней, внешней и буферной памяти.

Устройства внутренней памяти непосредственно участвуют в процессе преобразования информации, обмениваясь данными с процессором ЭВМ и вычислительной системой.

Внешняя память хранит большие массивы информации в течение длительного времени и обменивается данными с внутренней памятью.

Буферные ЗУ предназначены для промежуточного хранения данных при обмене между внешней и внутренней памятью.

По функциональному назначению БИС ЗУ делят на постоянные (ПЗУ) и оперативные (ОЗУ).

ПЗУ предназначены для хранения данных, однократно фиксируемых при изготовлении (неизменяемых программ, констант и т.п.). Основными требованиями, предъявляемыми к ПЗУ, являются неразрушающее считывание и энергонезависимость хранения информации.

ОЗУ относятся к внутренней памяти, служат для хранения переменных данных и программ в процессе текущих вычислений. В обычных ОЗУ информация разрушается после отключения питания, хотя существуют БИС энергонезависимых ОЗУ.

По технологии изготовления (типу элемента памяти) БИС ЗУ делятся на биполярные, использующие схемотехнику ТТЛ, ТТЛШ, ЭСЛ, И2Л, и униполярные на основе МДП - технологии, использующей структуры р-МДП, n-МДП, КМДП. Новейшими разработками являются ЗУ на основе арсенида галлия, у которых ЭП выполнены на основе полевых транзисторов с барьером Шотки.

По способу хранения информации БИС ЗУ делятся на статические и динамические.

В статических ЗУ применяются бистабильные триггерные элементы. Они управляются потенциальными сигналами и считывание информации происходит без ее разрушения.

В динамических ЗУ для хранения информации используются запоминающие конденсаторы или междуэлектродные ёмкости транзисторов, в которых информация храниться в виде заряда. За счёт токов утечки заряд на конденсаторе с течением времени уменьшается, поэтому его необходимо периодически восстанавливать путём подзарядки. Этот процесс носит название регенерации.

По способу размещения и поиска информации различают БИС ЗУ адресные и безадресные.

В адресных ЗУ поиск информации производиться по номеру (адресу) ячеек памяти, в которых она размещается. Адресные ЗУ бывают с произвольным обращением (произвольной выборкой), когда допустим любой порядок выборки адресов, и с последовательным обращением (последовательной выборкой), когда выбор ЯП возможен только в порядке возрастания или убывания адресов.

Среди безадресных ЗУ можно выделить ЗУ типа "очередь", стековые или магазинные и ассоциативные ЗУ. В ЗУ типа "очередь" считывание информации производится в том же порядке, в котором она была записана (FIFO - первый вошёл, первый вышел ). В ЗУ типа стек (LIFO - последним зашёл, первым вышел) считывание информации производится в порядке, обратном тому, в котором она была записана. В ассоциативных ЗУ поиск информации осуществляется по значению признака поиска, харатеризующего информацию, т.е. по её содержанию.

Основные параметры ЗУ

Основными классификационными параметрами ЗУ являются информационная ёмкость, тип логики и быстродействие.

Ёмкость (М) ЗУ выражается в битах (байтах) и определяется как произведение количества имеющихся в ЗУ ячеек памяти (N) на их разрядность (n).

При одинаковой ёмкости БИС ЗУ могут иметь различную организацию выборки. Например, при M=4096 ЗУ могут иметь следующие организации выборки:

4096x1 (4096 одноразрядных слов);

1024x4 (1024 четырёхразрядных слова);

512x8 (512 восьмиразрядных слов) и т.д.

Под быстродействием ЗУ понимают время, затрачиваемое на одно обращение к памяти ЭВМ для записи или считывания информации. Обращение к памяти ЭВМ (время выборки tA) определяется временным интервалом от момента подачи на вход ЗУ заданного сигнала и получением на выходе данных при условии, что все остальные необходимые входные сигналы уже поданы. Время выборки можно определять относительно любого из необходимых для работы ЗУ сигналов.

Система электрических параметров БИС ЗУ включает статические и динамические параметры. К статическим параметрам относятся входные и выходные токи и напряжения высокого и низкого уровней, выходной ток в третьем состоянии, токи потребления в режимах хранения, записи и считывания, напряжение питания.

Динамические параметры характеризуют скорость реакции БИС на входные воздействия и устанавливают необходимые для правильного функционирования временные соотношения между входными и выходными сигналами, что в целом составляет временную диаграмму работы БИС ЗУ.

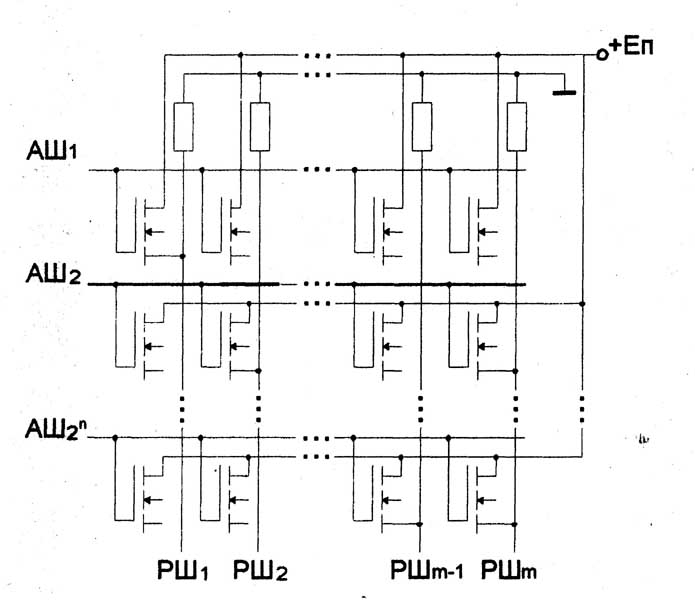

31. Структурные схемы статических ОЗУ с произвольной выборкой

Типовая структурная схема БИС ОЗУ среднего быстродействия приведена на рис.16.1. Накопитель представляет собой матрицу элементов памяти (ЭП), в качестве которых обычно используют триггеры. Выбор нужных ЭП осуществляется двумя дешифраторами DCX и DCY, на входы которых подаётся двоичный код адреса А.

Сигнал  определяет режим работы ЗУ. Если определяет режим работы ЗУ. Если  , то осуществляется режим записи. При этом входные данные DI через усилители записи (УЗп) подаются в ЭП накопителя, выбранные по данному адресу. Если , то осуществляется режим записи. При этом входные данные DI через усилители записи (УЗп) подаются в ЭП накопителя, выбранные по данному адресу. Если  , осуществляется режим чтения (считывания) информации из выбранных ЭП накопителя. Считанная информация DO поступает на выход ОЗУ через усилители считывания (УСч) и буферные , осуществляется режим чтения (считывания) информации из выбранных ЭП накопителя. Считанная информация DO поступает на выход ОЗУ через усилители считывания (УСч) и буферные

Рис.16.1

формирователи (БФ) при разрешении по выходу, определяемом сигналом СЕО.

В рабочее состояние ЗУ входит при разрешающем сигнале CS (выбор кристалла, выбор микросхемы). При запрещающем сигнале CS ЗУ находится в режиме хранения информации. Входов разрешения может быть несколько, тогда микросхема отпирается и выполняет свои функции по совпадению сигналов на этих входах.

32. Элементы памяти статических ОЗУ на биполярн транз

Наиболее простым ЭП на биполярных транзисторах для статических ОЗУ ТТЛ-типа является ЭП на основе триггера, выполненного на двух или трёхэмиттерных транзисторах. В ОЗУ с однокоординатной выборкой используются двухэмиттерные МЭТ (рис.16.4,а), нижние эмиттеры которых подключены к адресным шинам, а верхние - к разрядным, связанных со входами усилителей записи и считывания.

Примем устойчивое состояние триггера, когда транзистор VT1 открыт, a VT2 закрыт, за нулевое, а противоположное состояние - за единичное.

В режиме хранения на адресные шины поступает уровень логического 0 и эмиттерный ток открытого транзистора VT1 или VT2 (в зависимости от хранимой информации) будет протекать через адресную шину.

П ри считывании информации на адресной шине устанавливается напряжение логической 1 и ток эмиттера открытого транзистора VT1 или VT2 потечёт в связанную с этим эмиттером разрядную шину. Если, например, хранилась логическая 1, то этот ток поступит РШ1 и на выходе УСч появится напряжение высокого уровня. ри считывании информации на адресной шине устанавливается напряжение логической 1 и ток эмиттера открытого транзистора VT1 или VT2 потечёт в связанную с этим эмиттером разрядную шину. Если, например, хранилась логическая 1, то этот ток поступит РШ1 и на выходе УСч появится напряжение высокого уровня.

В режиме записи на адресной шине, соответствующей заданному адресу, также устанавливается уровень логической 1 и управление триггером становится возможным только по верхним эмиттерам. При этом откроется тот транзистор, верхний эмиттер которого будет иметь более низкий потенциал. Следовательно для записи 1 (отпирания VT2 и запирания VT1) необходимо в РШ1 подать уровень логического 0, а в РШО - уровень логической 1 и наоборот при записи 0.

В ЭП ОЗУ с двухкоординатной выборкой используются трехэмиттерные МЭТ. Третьи эмиттеры МЭТ соединяются с адресными шинами дешифратора DCY. Режим хранения обеспечивается подачей напряжения низкого уровня хотя бы на одну из шин АШХ или AШY, а в режимах записи и считывания на этих шинах выбранного ЭП должны действовать напряжения высокого уровня. В остальном принцип работы таких ЭП аналогичен принципу работы ЭП в ОЗУ с однокоординатной выборкой.

33. Элементы памяти статических ОЗУ на МДП транзисторах

Н а рис. 16.5 приведена принципиальная схема ЭП статического ОЗУ на МДП-транзисторах с каналами одинакового типа электропроводности (n-типа). Запоминающим элементом служит триггер, образованный двумя инверторами с нелинейной нагрузкой (VT1, VT2 и VT3, VT4), соединёнными между собой перекрёстными обратным связями. Транзисторы VT5 и VT6 используются для связи триггера с разрядными шинами РШО и РШ1. В режиме хранения эти транзисторы закрыты, а в режимах записи и считывания - открыты. а рис. 16.5 приведена принципиальная схема ЭП статического ОЗУ на МДП-транзисторах с каналами одинакового типа электропроводности (n-типа). Запоминающим элементом служит триггер, образованный двумя инверторами с нелинейной нагрузкой (VT1, VT2 и VT3, VT4), соединёнными между собой перекрёстными обратным связями. Транзисторы VT5 и VT6 используются для связи триггера с разрядными шинами РШО и РШ1. В режиме хранения эти транзисторы закрыты, а в режимах записи и считывания - открыты.

При считывании информации из ЭП перед поступлением высокого уровня напряжения на затворы транзисторов VT5 и VT6 подаётся напряжение высокого уровня на разрядные шины и паразитные ёмкости Сп1 и Cп2 заряжаются до напряжения, близкого по значению к +ЕП. При поступлении напряжения высокого уровня на адресную шину АШХ открываются транзисторы VT5 и VT6 и происходит разрядка через одну из разрядных шин РШО или РШ1 той паразитной ёмкости, которая оказалась соединённой с открытым транзистором VT2 или VT4. При этом на входном сопротивлении усилителя считывания, подключённого к этой разрядной шине, образуется импульс напряжения, который преобразуется выходным каскадом в сигнал логического 0 или логической 1.

В режиме записи после появления высокого уровня напряжения на адресной шине АШХ и отпирания транзисторов VT5 и VT6 в разрядные шины РШО и РШ1 подаются напряжения разных уровней, вследствие чего один из транзисторов VT2 или VT4 открывается, а другой закрывается. Например, для отпирания VT2 и запирания VT4 (записи 0) в РШО следует подать напряжение логического 0, а в PШ1 - напряжение логической 1.

Режим хранения обеспечивается при низком уровне напряжения в разрядных шинах АШХ. В ОЗУ с двухкоординатной выборкой последовательно с транзисторами VT5 и VT6 включаются ещё по одному МДП-транзистору с каналами такого же типа электропроводности. Затворы этих транзисторов соединяются параллельно между собой и подключаются к адресным шинам AШY.

Элементы памяти статических ОЗУ на КМДП транзисторах

Схема ЭП статического ОЗУ на КМДП-транзисторах показана на рис. 16.6. В его состав входят триггер, образованный двумя КМДП-инверторами с перекрёстными связями (VT1, VT2 и VT3, VT4), и два двунаправленных ключа (VT5 и VT6). В режиме хранения VT5 и VT6 закрыты, т.к. на их затворах действует напряжение низкого уровня. Перед считыванием на разрядных шинах РШО и РШ1 устанавливается низкий потенциал и происходит разрядка паразитных ёмкостей СП1 и СП2. Затем повышается потенциал на АШХ и открываются транзисторы VT5 и VT6. Если в ЭП хранилась 1 (VT2,VT3 - закрыты, a VT1, VT4 - открыты) начинается зарядка паразитной ёмкости Сп1 до порога срабатывания усилителя считывания. Потенциал РШО при этом остаётся низким.

В режиме записи на одной из разрядных шин устанавливается высокий потенциал. Предположим, что в данный ЭП необходимо записать логический 0, т.е. открыть транзистор VT2 и закрыть VT4. Для этого необходимо установить высокий потенциал на РШО и АШХ. В результате высокий потенциал с РШО поступит на затвор VT2 и вызовет его отпирание, потенциал стока VT2 понизится до напряжения логического 0 и приведёт к запиранию VT4.

ЭП на КМДП-транзисторах в режиме хранения потребляют очень малую мощность (десятки-сотни мкВт), обусловленную лишь токами утечки.

34. Элементы памяти и БИС ОЗУ динамического типа

В основе построения ЭП динамического типа используется возможность представления информации в виде заряда на запоминающем конденсаторе. Динамические ЭП реализуются на основе МДП транзисторов. В первых динамических БИС ОЗУ ЭП включал в себя три МДП транзистора.

Ошибка! Объект не может быть создан из кодов полей редактирования.

Современные динамические БИС ЗУ проектируются на основе одно-транзисторных ЭП (рис.16.7). В режиме хранения информации на адресной (АШХ) и разрядной (РШ) шинах действуют нулевые потенциалы, транзистор VT закрыт и запоминающий конденсатор С отключен от РШ. При подаче на АШХ высокого потенциала транзистор VT открывается и ЭП оказывается подготовленным для записи или считывания информации. При записи 1 в РШ подаётся высокий потенциал и происходит зарядка запоминающего конденсатора. Для записи 0 в РШ сохраняется нулевой потенциал и конденсатор разряжается (если он был заряжен) через разрядную шину. При считывании информации состояние ЭП определяется наличием (если запоминающий конденсатор был заряжен) или отсутствием напряжения в РШ.

35. Общие сведения, основные параметры и классификация постоянных запоминающих устройств

Постоянные запоминающие устройства (ПЗУ) предназначены для хранения программ, таблиц, тестов и другой информации, которая не изменяется в процессе работы устройства. Необходимая информация записывается в ПЗУ заблаговременно до ее использования. ПЗУ широко используются для построения управляющих программ или микропрограммных памятей и различных комбинационных схем ЭВМ и систем автоматизации: преобразователей кодов, дешифраторов, генераторов последовательностей сигналов, мультиплексоров, сдвиговых регистров и др. Микропрограммные устройства управления, построенные на основе ПЗУ, отличаются высокой гибкостью, низкой стоимостью и позволяют легко изменять набор команд ЭВМ путем замены ПЗУ. Возможность простого изменения хранимой информации делает ПЗУ незаменимыми в решении проблемы сокращения сроков и стоимости проектирования и эксплуатации, особенно в микропроцессорных системах.

К основным параметрам ПЗУ относятся информационная емкость, быстродействие и потребляемая мощность.

К эксплуатационным параметрам ПЗУ относятся их стоимость, надежность работы, сохранение работоспособности в широком диапазоне температур, в условиях повышенных механических воздействий и др.

По способу записи информации БИС ПЗУ делятся на три группы:

1.Обычные, или масочные ПЗУ (МПЗУ), запись информации в которых осуществляется изготовителем однократно с помощью маски (шаблона) на одном из этапов изготовления кристалла. Из всех методов записи информации в ПЗУ этот метод обладает самой большой надежностью, самой высокой плотностью компоновки, наибольшей простотой изготовления и самой низкой стоимостью при массовом производстве .

2.Программируемые ПЗУ (ППЗУ), заполняемые однородной информацией при изготовлении, которая изменяется однократно после программирования пользователем электрическим способом с помощью стенда-программатора.

З.Репрограммируемые ПЗУ (РПЗУ), в которых записанная электрическим способом информация может быть стерта и вместо нее записана новая. Стирание записанной в РПЗУ информации может быть осуществлено либо электрическим способом, либо ультрафиолетовым облучением.

По способу считывания информации БИС ПЗУ делятся на синхронные (тактируемые) и асинхронные.

По технологическому исполнению БИС ПЗУ делятся на две основные группы: биполярные схемы, использующие схемотехнику ТТЛ или ЭСЛ, и МДП-схемы, использующие р-МДП, n-МДП и КМДП-структуры.

По уровням входных и выходных сигналов БИС ПЗУ совместимы с полупроводниковыми схемами, изготовленными по схемотехнике ЭСЛ, ТТЛ или КМДП-типа, причем возможны построения кристаллов как полностью по одной схемотехнике, так и комбинации ЭСЛ с ТТЛ или КМДП с ТТЛ.

Независимо от способа записи и технологии изготовления все ПЗУ являются устройствами с произвольной выборкой информации, отличающейся наибольшей простотой организации и управления.

Рис.16.8

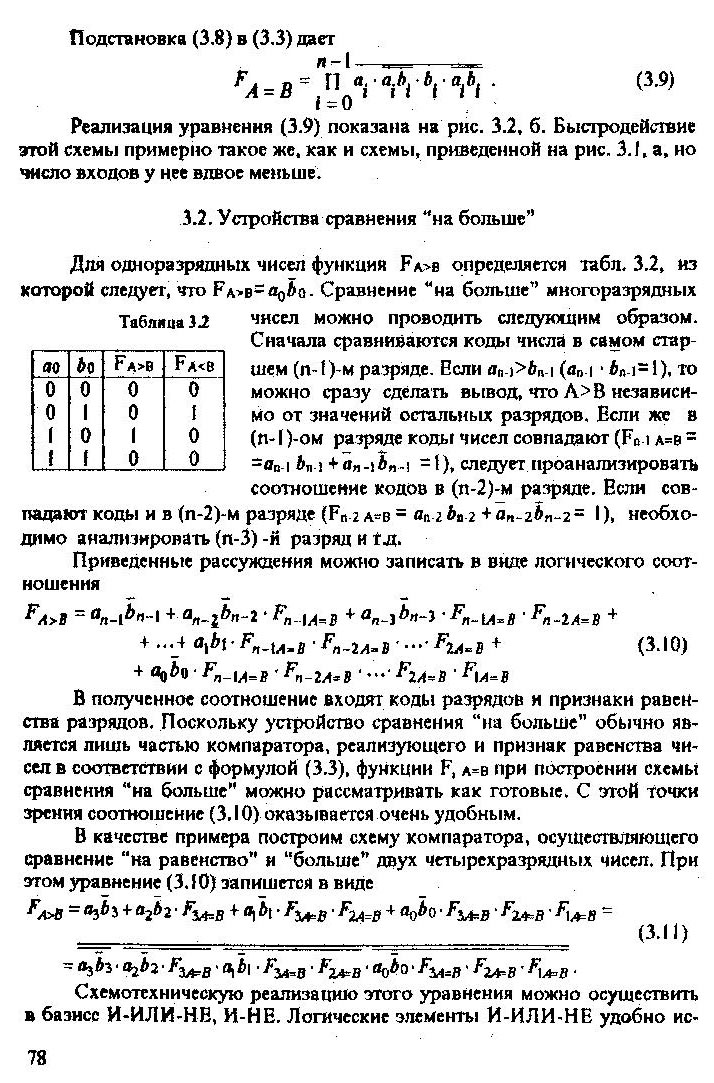

Структурная схема типового полупроводникового ПЗУ показана на рис.16.8,а. Его основу составляет двухкоординатная матрица элементов памяти или запоминающая матрица (ЗпМ) с полным дешифратором.

Элементы памяти (ЭП) располагаются в местах пересечения горизонтальных адресных шин (АШ), соединенных с выходами дешифратора (DC), и вертикальных (разрядных) шин, которые подключаются к информационным входам мультиплексоров. На входы DC подаются младшие разряды адреса Ao...Ak-1, а на адресные входы мультиплексоров - старшие разряды адреса

Ak...An-1. При этом возбуждается одна из адресных шин, и все ЭП, связанные с этой шиной, выдают хранящуюся в них информацию на все разрядные шины. Хранимая в ЭП информация 0 или 1 зависит от того, соединен ли этот ЭП с разрядной шиной (РШ) или не соединен. Нарушение соединения осуществляется разрушением плавкой перемычки, соединяющей его с РШ (на рис.16.8,а эти перемычки показаны волнистыми линиями) путем пропускания через нее импульса тока достаточной силы. Выборка нужного числа бит для подачи на выход ПЗУ осуществляется мультиплексорами. В зависимости от организации ПЗУ дешифратор и мультиплексор могут иметь различную разрядность. Например, ПЗУ с информационной емкостью N=1024 бит может иметь организацию 256x4, что означает использование внутри микросхемы дешифратора 1-256 для возбуждения адресных шин и четырех мультиплексоров 4-1 для считывания выходных данных с разрядных шин.

Микросхемы ПЗУ обычно имеют вход разрешения CS (chipselect), на который подается сигнал обращения к ПЗУ.

На схемах (рис.16.8,б) ПЗУ обозначается ROM (от readonlymemory-память, предназначенная только для чтения).Запись информации в БИС ПЗУ осуществляется с изменением физических свойств кристалла, благодаря чему она сохраняется и после отключения источника питания. Устройства, обладающие этим свойством, называют энергонезависимыми.

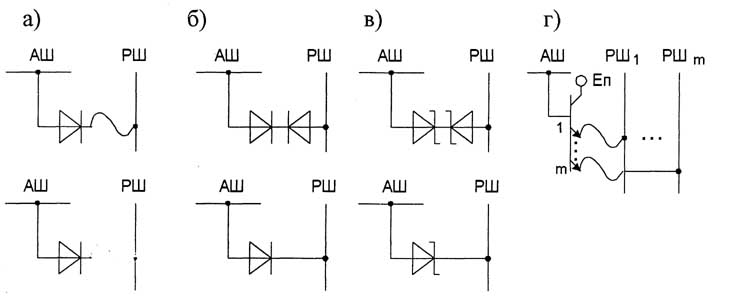

Масочные ПЗУ

Масочные ПЗУ строятся на основе диодов, биполярных и МДП-транзисторов.

+Еп

Рис.16.9

В диодных ПЗУ диоды включаются в те пересечения ЗпМ, которые соответствуют записи 1, а в местах, где должен быть записан 0, они отсутствуют. Исключение диодов из соответствующих пересечений ЗпМ достигается тем, что на последнем этапе изготовления проводящая металлическая пленка, соединяющая катод диода с разрядной шиной, не изготавливается. Вид диодной ЗпМ показан на рис.16.9,а. Так как диодная матрица представляет собой элемент с гальваническими связями, то выходные

сигналы имеют ту же форму и полярность, что и входные. Таким образом, если на ее входы (адресные шины) подаются напряжения постоянных уровней, то и на выходах (разрядных шинах) уровни будут также постоянными, что исключает необходимость применения дополнительных выходных регистров.

Н

Рис.16.10

а рис.16.9,б показана ЗпМ, выполненная на биполярных многоэмиттерных транзисторах (МЭТ). При возбуждении одной из адресных шин на базе связанного с ней МЭТ возникает напряжение высокого уровня, в то время как на базах всех остальных транзисторов напряжение равно нулю. Информация логического 0 или логической 1 в любой разрядной шине зависит от того, есть ли связь разрядной шины с соответствующим эмиттером выбранного МЭТ или нет. Коллекторный ток выбранного МЭТ проходит только в те разрядные шины, которые связаны с эмиттерами этого транзистора, создавая положительные напряжения на этих разрядных шинах, в то время как на разрядных шинах, не связанных с его эмиттерами, напряжение равно нулю.

36. Программируемые ПЗУ

Структура БИС ППЗУ подобна структуре БИС МПЗУ и отличается только видом ЭП. Элементами памяти ППЗУ являются диоды или многоэмиттерные транзисторы (МЭТ).

Программирование ППЗУ осуществляется пережиганием перемычек (рис.16.11,а,г), либо электрическим пробоем р-n перехода (рис.16.11,6) или диодов Шотки (рис.16.11,в). В качестве плавких перемычек применяются тонкие пленки из нихрома или поликристаллического кремния.

Ток пережигания составляет 50... 100 мА. При этом плотность тока в перемычке достигает 107 А/см2, что приводит к ее разрушению. Электрический пробой р-n перехода или диода Шотки осуществляется приложением к паре встречновключенных диодов повышенного напряжения (импульсного), являющегося для одного из них обратным.

Рис. 16.11

Процесс программирования осуществляется с помощью специального устройства - программатора, и заключается в подаче электрических сигналов на соответствующие внешние выводы ППЗУ.

Требуемые токи программирования обеспечиваются повышением приложенного к микросхеме ППЗУ напряжения до 12...20 В. Для рассеивания выделяемой при программировании мощности приходится увеличивать размеры ЭП, что приводит к снижению быстродействия из-за увеличения паразитных емкостей и уменьшению коэффициента интеграции. Коэффициент интеграции снижается также вследствие создания на кристалле БИС ППЗУ электронных схем формирования токов программирования, которые используются только один раз при программировании и в дальнейшей эксплуатации не требуются. На рис.16.12 показаны УГО электрически программируемого (прожигаемого) ПЗУ К155РЕЗ емкостью 256 бит с организацией 32x8, фрагмент (часть) схемы и временные диаграммы режима программирования.

В выпускаемых заводом микросхемах все перемычки целые. При включении питания Uпl = 5 В (Un2 = 0 В) при заданном адресе А4 ... А0 и CS = 0 возбуждается один из выходов дешифратора, например первый, и коллекторный ток МЭТ через нижний эмиттер и резистор R2 втекает в базу транзистора VT2, вводя его в режим насыщения. На открытом коллекторном выходе VT2 образуется напряжение низкого уровня. Следовательно, неразрушенные перемычки соответствуют записи логического 0 во всех ЭП.

Р ежим программирования (запись в нужные ЭП логической 1) осуществляется следующим образом. На адресных входах микросхемы устанавливается требуемый адрес, после чего на шину Unl подается повышенное напряжение Uпl = 12,5 В (момент времени t1 на рис.16.12,в). ежим программирования (запись в нужные ЭП логической 1) осуществляется следующим образом. На адресных входах микросхемы устанавливается требуемый адрес, после чего на шину Unl подается повышенное напряжение Uпl = 12,5 В (момент времени t1 на рис.16.12,в).

Затем на внешний резистор R=390 Ом подается напряжение Uп2 = 12,5 В (момент времени t2). При этом пробивается стабилитрон VD, открывается и входит в режим насыщения транзистор VT1. После этого на вход выбора кристалла подается сигнал C¯S = 0, вызывающий срабатывание дешифратора и появление напряжения высокого уровня на одном из его выходов, которое поступает на базу выбранного МЭТ (например МЭТ1). От источника Unl через МЭТ и насыщенный транзистор VT1 протекает большой ток, пережигающий перемычку. Выход из режима программирования осуществляется в обратной последовательности. В одном цикле допускается программирование только одного разряда.

37. Репрограммируемые ПЗУ

Структура БИС РПЗУ аналогична структуре МПЗУ, но в качестве ЭП используется МДП-структура, механизмом запоминания и хранения информации в которой является процесс накопления заряда. В зависимости от структуры МДП-транзистора различают два основных вида РПЗУ: РПЗУ, стираемые ультрафиолетовым облучением (РПЗУ УФ, EPROM), и электрически – стираемые РПЗУ (РПЗУ ЭС, EEPROM). Запись информации в обоих типах осуществляется электрическим способом.

РПЗУ с электрическим стиранием информации

Основными преимуществами электрически стираемых РПЗУ (РПЗУ ЭС) по сравнению с РПЗУ УФ являются оперативность смены информации (без изъятия микросхем из аппаратуры) и большее число циклов программирования (до103... 105).

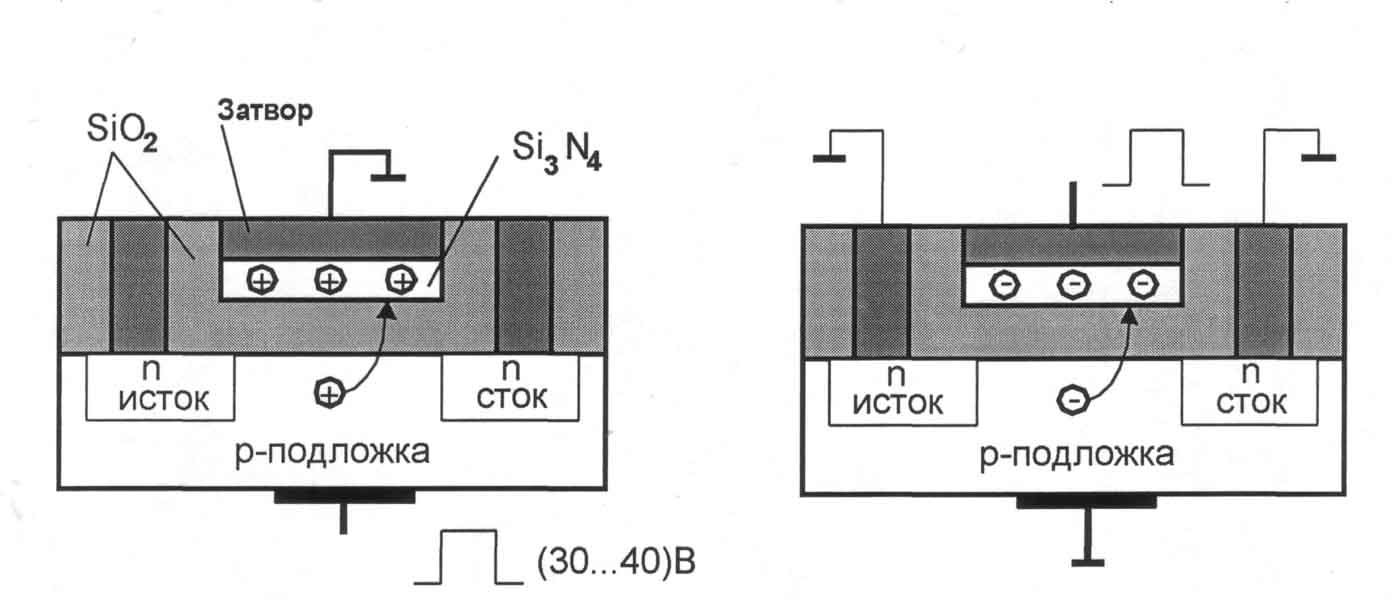

Э

лементом памяти РПЗУ ЭС является МНОП - транзистор, имеющий структуру металл-нитрид-оксид-полупроводник. В отличие от МДП-транзис-тора у МНОП-транзистора металлический затвор отделен от подложки двумя слоями диэлектрика: диоксидом кремния SiO2 толщиной 4 ... 5 нм и нитридом кремния Si3N4 толщиной 80-100 нм (рис.16.17,а).

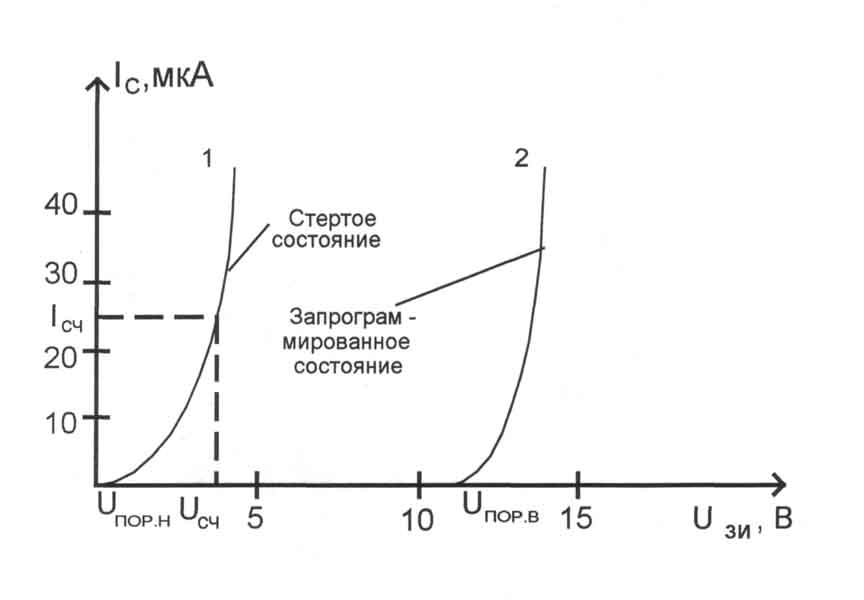

Информация, записанная в МНОП-транзистор, определяется количеством заряда, накопленного на границе двух слоев диэлектриков. Отрицательный заряд повышает пороговое напряжение Uзипор транзистора, а положительный -понижает.

В режиме стирания затвор транзистора заземляется, а на подложку подается положительный импульс напряжения амплитудой 30...4О В. Большая напряженность возникшего при этом электрического поля между подложкой и затвором приводит к туннельному пробою, дырки туннелируют из подложки и накапливаются на границе диоксида кремния и нитрида кремния, создавая положительный заряд. Уход дырок из приповерхностного слоя подложки вызывает обогащение этой области электронами и, следовательно, уменьшение порогового напряжения до значения Uпор.н. .

В режиме программирования выводы подложки, стока и истока заземляются, а положительный импульс напряжения подается на затвор. Поскольку направление напряженности возникшего при этом электрического поля изменилось на противоположное, то из подложки будут туннелировать не дырки, а электроны, которые, накапливаясь на границе диэлектриков, создадут отрицательный заряд (рис.16.17,б).

Обеднение приповерхностной области подложки электронами приведет к увеличению порогового напряжения транзистора до значения Uпор..в. В режиме считывания на затвор МНОП-транзистора с выбранной АШ подается напряжение Uсч, находящееся между значениями пороговых напряжений высокого (Uпор..в) и низкого (Unop.н) уровней (см. рис.16.16).

При этом если на границе диэлектрических пленок был положительный заряд, образованный в режиме стирания, то значение протекающего через транзистор в разрядную шину тока Iсч будет существенно больше, чем при хранении на границе диэлектрических пленок отрицательного заряда, образованного в режиме программирования. Таким образом, режим стирания сопровождается записью в ЭП логической единицы, а режим программирования - записью логического нуля.

38. РПЗУ с ультрафиолетовым стиранием информации

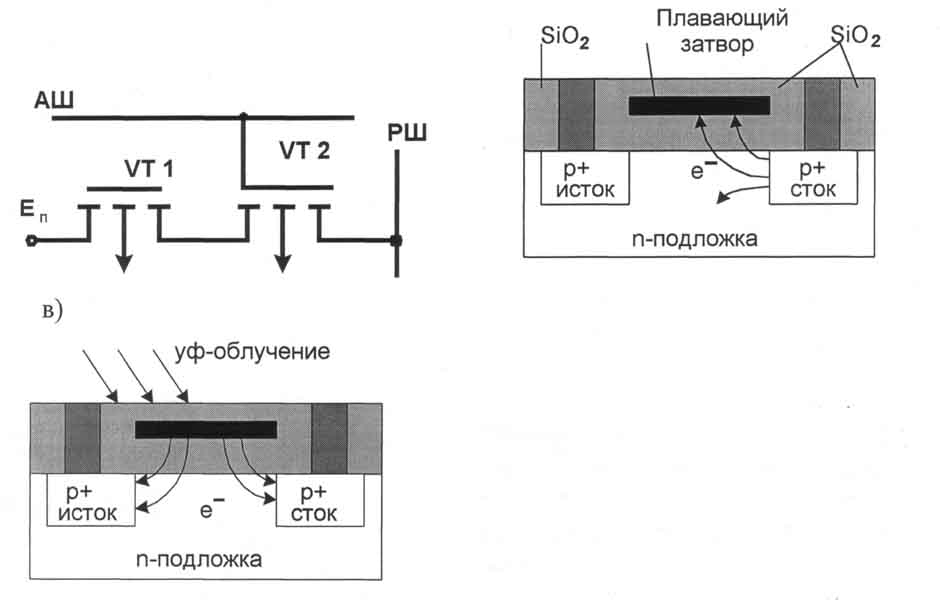

Элементом памяти РПЗУ УФ является МДП-транзистор с плавающим изолированным затвором (ПЗ) с использованием при записи эффекта лавинной инжекции (ЛИПЗ МДП-транзистор) в сочетании с ключевым транзистором либо один запоминающий транзистор с ПЗ и управляющим затвором.

Элемент памяти первого типа показан на рис.16.14,а. Транзистор VT2-адресный (ключевой) ,VT1 -собственно запоминающий транзистор ЭП. В качестве VT2 используется обычный р-МДП-транзистор. Если на возбуждающей АШ низкий уровень напряжения, то он подключает РШ к транзистору VT1, представляющему собой ЛИПЗ МДП-транзистор с каналом р-типа. Этот транзистор может находиться в одном из двух устойчивых состояний: открытом или закрытом, что соответствует хранению 1 или 0. Структура транзистора VT2 приведена на рис.16.14,б. Металлический или кремниевый затвор со всех сторон изолирован диэлектрическим слоем диоксида кремния SiO2 и не имеет наружного вывода.

Из-за отсутствия гальванической связи с другими электродами потенциал его оказывается "плавающим".

Е

а) б)

сли при записи информации между стоком и подложкой приложить напряжение 30...50 В, являющимся обратным для перехода сток-подложка, то в результате лавинного пробоя часть электронов приобретает энергию, достаточную для преодоления энергетического барьера между кристаллом и диэлектриком. Инжектируемые из кристалла электроны дрейфуют в диэлектрике к ПЗ и накапливаются на нем.

Н

Рис. 16.14

акопленные в ПЗ электроны создают отрицательный заряд, под действием которого в приповерхностном слое n-подложки появляется инверсионный слой р-типа, образующий проводящий канал между областями стока и истока.

Через VT1 и VT2 в разрядную шину передается напряжение Еп, т.е. считывается 1. При отсутствии отрицательного заряда на ПЗ канал между стоком и истоком отсутствует и с РШ считывается 0. Поскольку ПЗ окружен изолирующим слоем, заряд сохраняется в течение длительного времени - до 10 лет и более.

Стирание хранимой в РПЗУ информации осуществляется ультрафиолетовым или рентгеновским облучением. При этом за счет ионизации диоксида кремния происходит внутренняя фотоэмиссия электронов ПЗ в подложку (рис.16.14,в)

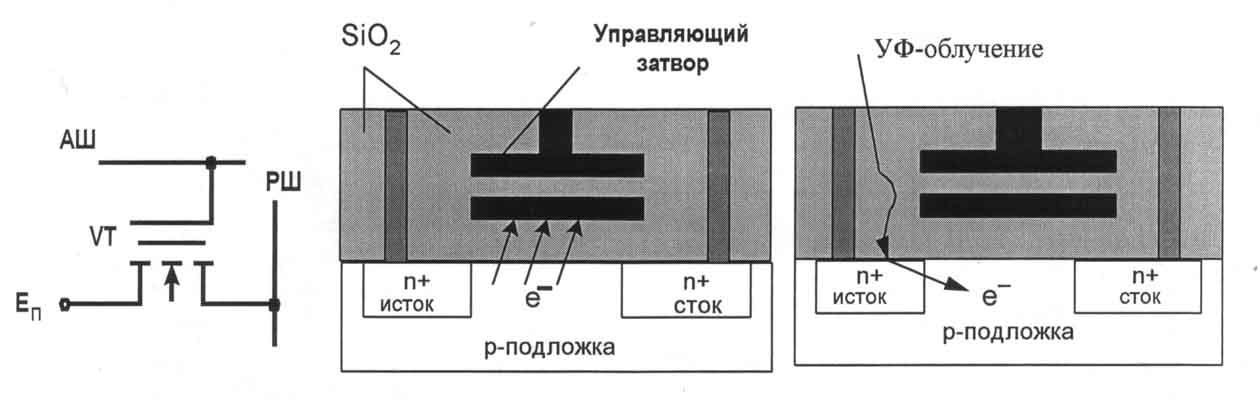

Рассмотренный двухтранзисторный ЭП РПЗУ применялся в первых БИС такого типа ПЗУ.С целью повышения коэффициента интеграции и упрощения схемы ЭП был разработан однотранзисторный ЭП, в котором используется аналогичный принцип записи и стирания информации. Такой ЭП (рис.16.15,а) отличается от рассмотренного тем, что у него кроме ПЗ имеется второй затвор, называемый управляющим, или затвором выборки (рис.16.15,б). Материалом для обоих затворов служит поликристаллический кремний. При отсутствии отрицательного заряда на ПЗ ЛИПЗ МДП- транзистор имеет малое пороговое напряжение Изипор=Uпор.н (рис.16.16). При программировании (записи информации) на затвор подается положительный импульс напряжения амплитудой около 25 В и длительностью в несколько десятков миллисекунд. Это вызывает лавинную инжекцию электронов из подложки через изолирующий диоксид кремния, которые, двигаясь к управляющему затвору, оседают на ПЗ, создавая на нем отрицательный заряд. Отрицательный заряд на ПЗ увеличивает пороговое напряжение транзистора до значения Uзипор = Uпор.в .

В режиме считывания положительное напряжение не более 5В с возбужденной адресной шины поступает на управляющий затвор (см.рис.16.15,а). Если на ПЗ нет отрицательного заряда, т.е. он не подвергался программированию, то между областями стока и истока образуется проводящий канал и в РШ передается напряжение Еп, что соответствует логической 1 (рис.16.16).

а) б) в)

Рис.16.15

Если же транзистор программировался и на его ПЗ имеется отрицательный заряд, канал между стоком и истоком не образуется, и РШ оказывается Если же транзистор программировался и на его ПЗ имеется отрицательный заряд, канал между стоком и истоком не образуется, и РШ оказывается отключенной от шины Еп, что соответствует хранению этим транзистором логического 0. Стирание информации осуществляется ультрафиолетовым облучением через прозрачное кварцевое окошко на поверхности микросхемы в течение нескольких десятков минут сразу во всех ЭП.

Падающий ультрафиолетовый свет увеличивает энергию электронов ПЗ до такого уровня, при котором они преодолевают барьер между ПЗ и изолирующим слоем SiCb и стекают в подложку. В результате ПЗ всех ЭП освобождаются от электронов, т.е. во все ЭП записывается логическая 1.

Рис. 16.16

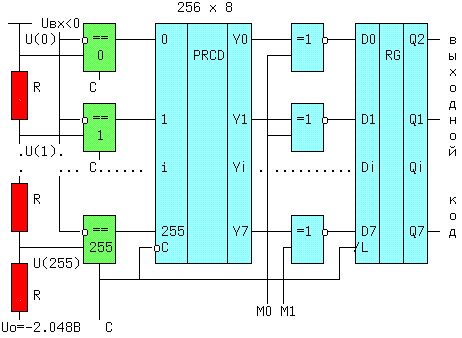

51 АЦП ПАРАЛЛЕЛЬНОГО ТИПА

В таком АЦП весь диапазон входного напряжения разбивается на 2^n интервалов. Каждому интервалу соответствует опорное напряжение Uо(i), снимаемое с делителя напряжения, и свой аналоговый компаратор, сравнивающий Uвх с Uо(i).

Для любого входного напряжения в диапазоне (0 .. ¦Uo¦)В найдется такой i-ый компаратор, входное напряжение на котором будет больше или равно опорному U(i). В этом случае на выходе этого компаратора напряжений и на выходах всех компараторов с номерами меньшими i появится "1", а на выходах остальных "0". Приоритетный шифратор сформирует двоичный код, равный наивысшему номеру входа на котором еще присутствует единица. Полученный код через управляемые инверторы/повторители, выполненные на элементах равнозначности, защелкивается в выходном регистре. Учитывая логику работы шифратора, заключающуюся в том, что если на его входах с 1-го по (n-1)-ый одни нули, то единица обязательно должна быть на нулевом входе, можно сэкономить на нулевом компараторе. В этом случае нулевой вход шифратора постоянно подключен к "1", и если входное напряжение находится в пределах 0 <= ¦Uвх¦ < ¦U(1)¦, то нулевой код на выходе генерируется автоматически. Элементы ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ при значении Mi = 0 инвертируют выходной сигнал шифратора, а при Mi = 1 повторяют его. Зависимость выходного кода от режима дана ниже:

M1 M0 Выходной код

1 1 прямой

0 0 обратный

0 1 дополнительный прямой

1 0 дополнительный обратный.

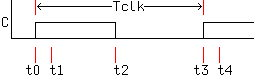

Быстродействие достигается, как за счет параллельного принципа работы, так и за счет конвейерного передвижения информации внутри АЦП (см. рисунок).

В момент t0 положительным фронтом сигнала C происходит защелкивание кода от предыдущего цикла преобразования. В момент t1 компараторы открываются и начинается сравнение входного напряжения с опорным в текущем цикле. Когда тактовый сигнал C станет равным нулю (момент t2), шифратор отпирается по входу C и начинает преобразование текущего значения Uвх в код. Следующий цикл преобразования начинается в момент t3, когда производится запоминание в регистре текущего кода и его появление на выходах в момент t4, одновременно с началом сравнения на входах компараторов следующего значения напряжения. Время преобразования Tпр = Tclk, т.е. примерно на порядок меньше, чем у АЦП последовательных приближений. По такой схеме выполняются преобразователи типа 1107ПВ1,..5.

|

Скачать 8.5 Mb.

Скачать 8.5 Mb.