Шпоры по Схемоте. 1. счетчики основные параметры и классификация

Скачать 8.5 Mb. Скачать 8.5 Mb.

|

|

9. Регистры Назначение и классификация Регистром называют функциональный узел ЭВМ, предназначенный для приема, хранения и передачи информации, представленной в виде двоичного кода, а также для поразрядного выполнения некоторых операций над двумя числами. Он представляет собой совокупность определенным образом соединенных триггерных ячеек с устройством управления входными данными. Число используемых триггеров определяет его разрядность. Каждый триггер регистра имеет прямой и инверсный выходы, что позволяет снимать записанный в нем код в прямом, инверсном (обратном) или парафазном виде. Основными признаками классификации регистров являются способ ввода-вывода и характер представления вводимой информации. По способу ввода и вывода (приема и передачи) информации регистры подразделяются на параллельные, последовательные и параллельно-последовательные. По характеру представления вводимой и выводимой информации регистры делятся на однофазные и парафазные. В однофазных регистрах информация вводится в прямом или инверсном кодах, а в парафазных – одновременно в прямом и инверсном. Вывод информации из регистров обоих типов может осуществляться как в прямом так и в инверсном кодах. По числу тактов управления регистры могут быть однотактными, двухтактными и многотактными. Число тактов определяется типом используемых в регистре триггеров. В зависимости от числа источников, с которых информация поступает на входы регистра, различают одноканальные и многоканальные регистры. 11. Параллельно-последовательные регистры Регистры этого типа представляют собой сочетания схем параллельного и последовательного регистров и служат для преобразования кодов числа из одного вида в другой, а также параллельного вывода предварительно сдвинутого кода числа, хранящегося в регистре. Фрагмент параллельно-последовательного регистра, выполненного на универсальных D-триггерах, показан на рис.13.8.  Ввод числа А параллельным кодом (параллельная загрузка регистра) осуществляется по сигналу PL = 1 (parallel load), а вывод информации параллельным кодом – по сигналу Твыв.парал. При равенстве этих сигналов нулю регистр работает как сдвиговый. Использование установочных входов Параллельно-последовательные регистры называются также регистрами хранения и сдвига. Такие регистры имеются в сериях К155, КМ155(ТТЛ), К176 (КМОП), К500 (ЭСЛ) и др. На рис.13.9,а представлена схема четырехразрядного регистра сдвига и хранения К155ИР1, а на рис.13.9,б – его условное обозначение. Каждый разряд регистра образован синхронным двухступенчатым RS-триггером. Благодаря инверторам на входах S эти триггеры работают как синхронные D-триггеры, управляемые положительным перепадом по входу С. Регистр имеет четыре входа параллельной загрузки (D0,...,D3) и один последовательный вход данных S1, a также 4 параллельных выхода (Q0,...,Q3) от каждого триггера. Управление режимами работы регистра осуществляется сигналами по входу RE (разрешение параллельной загрузки) и тактовым входам С1 и С2. При RE = 1 разрешается работа тактовому входу С2. В момент прихода на вход С2 отрицательного перепада на синхровходах триггеров всех четырех разрядов формируется положительный перепад и в триггеры переписывается информация со входов D1,...,D4 независимо от значений сигналов на входах S1 и С1. Запись информации последовательным кодом осуществляется через вход S1 при сигнале RE = 0. При этом блокируются входы параллельной загрузки. С приходом отрицательных перепадов на вход С1 данные последовательно сдвигаются от входа S1 до выхода Q3, т.е. в сторону старшего разряда. Для сдвига в сторону младшего разряда (от Q3 к Q0) необходимо соединить выход Q3 с входом D2, выход Q2 – с входом D1, выход Q1 – с входом D0 и установить на входе RE напряжение высокого уровня. Входом последовательного кода в этом случае будет являться вход D3, а сдвиг будет осуществляться отрицательными перепадами по входу С2.  12. Использование сдвиговых регистров в качестве счётчиков На рис. 13.10 показана стандартная схема счётчика на сдвиговом регистре, состоящем из JK-триггеров. Прямой и инверсный выходы триггера каждого разряда используются для управления логической схемой, входящей в цепь обратной связи. Цепь обратной связи формирует информационные сигналы J0 и К0, управляющие работой триггера самого младшего разряда Тг0. Такое построение схемы позволяет использовать ее для генерации двоичных последовательностей или в качестве счётчика.  Цепь обратной связи вырабатывает сигнал либо 0, либо 1, который, поступая на входы J0 и К0 (после инвертирования) триггера Тг0 определяет состояние этого триггера. Например, если n-разрядный сдвиговый регистр находится в состоянии Qn-1…Q2Q1Q0=0...001, то в зависимости от значения сигнала обратной связи следующим его состоянием будет либо 0…010, либо 0…011. 13. Кольцевой счётчик В таком счётчике при поступлении тактовых импульсов С единственная 1 перемешается от разряда к разряду. Он выполнен на сдвиговом регистре, у которого сигнал обратной связи подается с прямого выхода триггера последнего разряда на входы первого (рис.13.17). Работа счётчика начинается с режима "Предустановка", в котором сигналом  Достоинством рассмотренного счётчика является простота его реализации, а недостатком – невозможность осушествления вывода информации в двоичном коде. Кроме того, в n-разрядном счётчике подобного типа из 2n возможных состояний 2n-n не используются и являются запрещенными. Если по какой-либо причине счётчик окажется в одном из этих состояний, то без постороннего вмешательства он не сможет перейти к выработке правильной последовательности.

Запрещенными состояниями счётчика являются такие, при которых в его разрядах число единиц оказывается более одной, либо во всех разрядах имеются нули. Для обнаружения запрещенных состояний счётчик снабжается дополнительной комбинационной схемой. Например, для трехразрядного кольцевого счётчика запрещенные состояния возникнут в случае, если единицы будут одновременно присутствовать на выходах первого и второго разрядов (Q0Q1=1), либо первого и третьего (Q0Q2=1), либо второго и третьего (Q1Q2=1), либо на выходах всех трех разрядов (Q0Q1Q2=1). Следовательно, сигнал обнаружения лишней 1 должен формироваться на основании булевого выражения F1=Q0Q1+Q0Q2+Q1Q2+Q0Q1Q2=Q0Q1+Q0Q2+Q1Q2. (13.2) Для обнаружения нулевого состояния триггеров всех разрядов можно использовать функцию Сигналы, сформированные на основании выражений (13.2) и (13.3), могут использоваться не только для обнаружения ошибки в работе счётчика, но и для его предустановки в исходное состояние. Счётчик Джонсона Счётчик Джонсона отличается от рассмотренного кольцевого счётчика тем, что в нем сигнал обратной связи на входы триггера младшего разряда сдвигового регистра подается не с прямого, а с инверсного выхода триггера старшего разряда. Благодаря этому если в исходном состоянии триггеры всех разрядов регистра установлены в 0, то при поступлении импульсов синхронизации начнётся их постепенное переключение в 1. После того как все триггеры окажутся в единичном состоянии, начнется их поочередное (начиная с триггера младшего разряда) переключение в 0 и т.д. Следовательно, число рабочих состояний такого счётчика равно удвоенному числу его разрядов. Функционирование десятичного счётчика Джонсона осуществляется в соответствии с табл.13.4. Смена состояний такого счётчика происходит в соответствии с кодом Либау-Крейга. Для получения двоично-десятичного кода к выходам счётчика необходимо подключить комбинационную схему – преобразователь кодов.

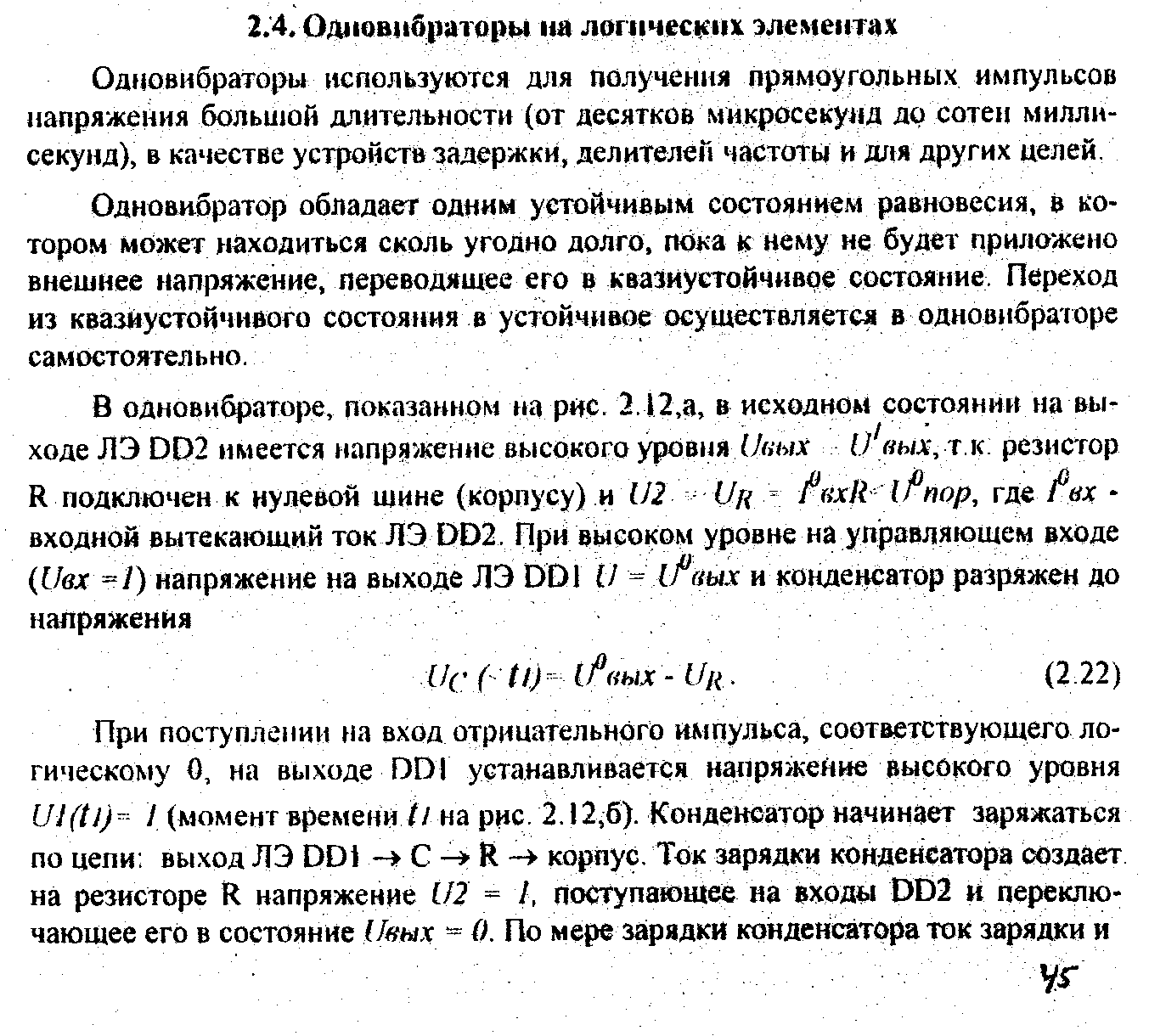

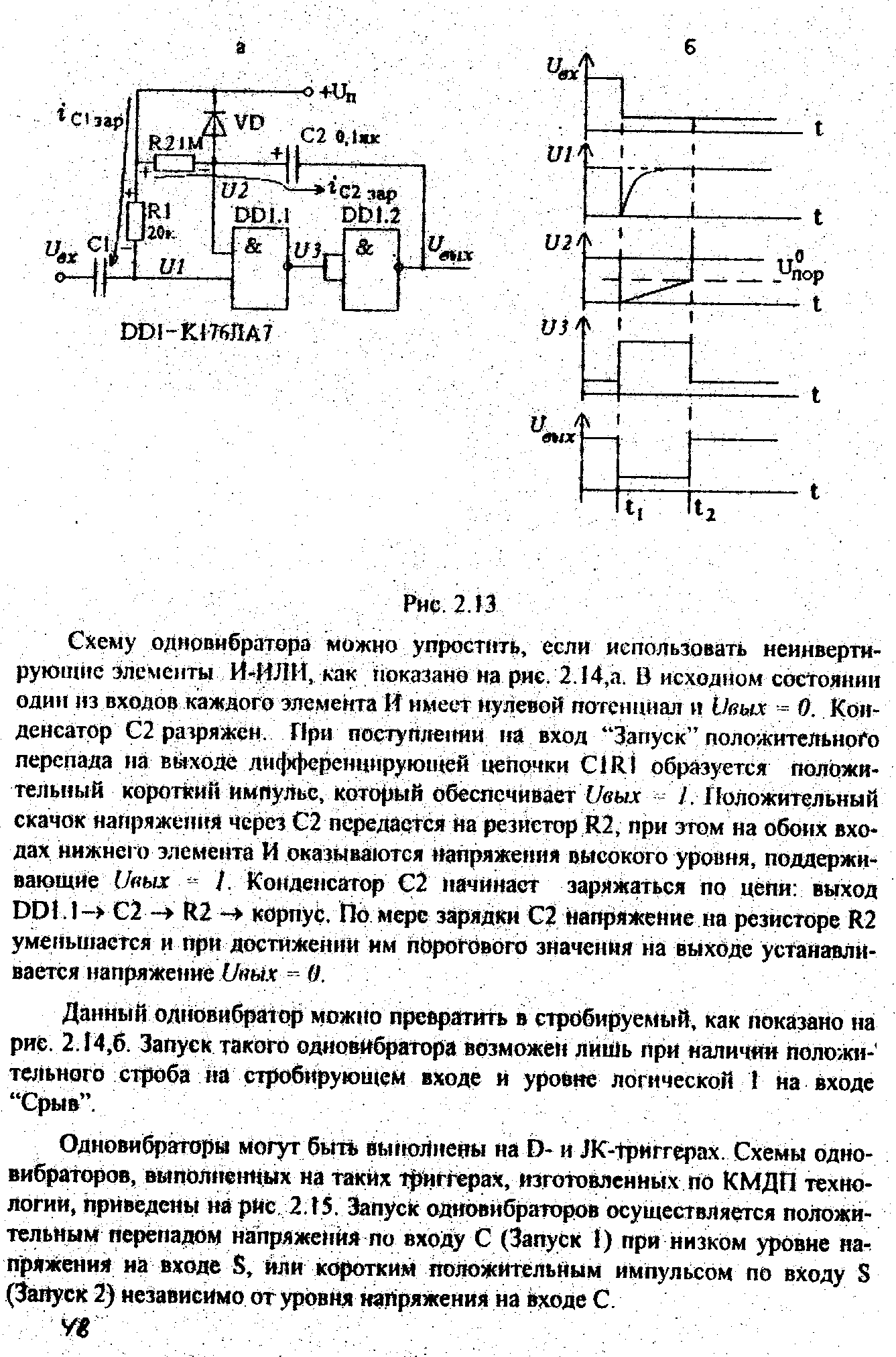

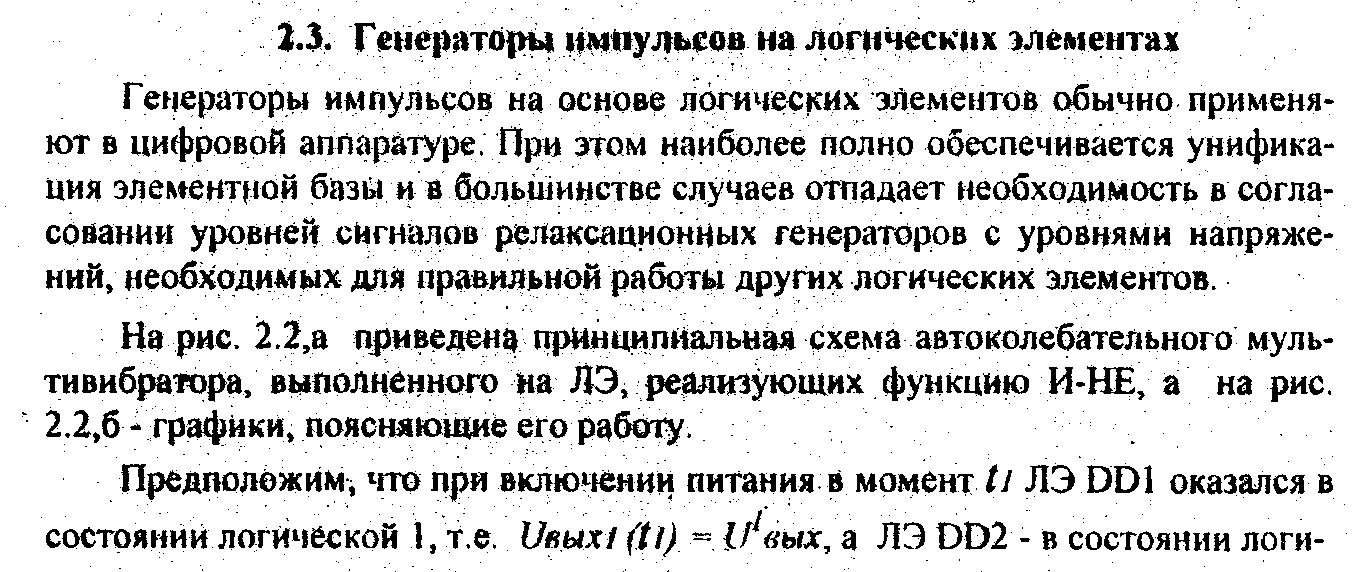

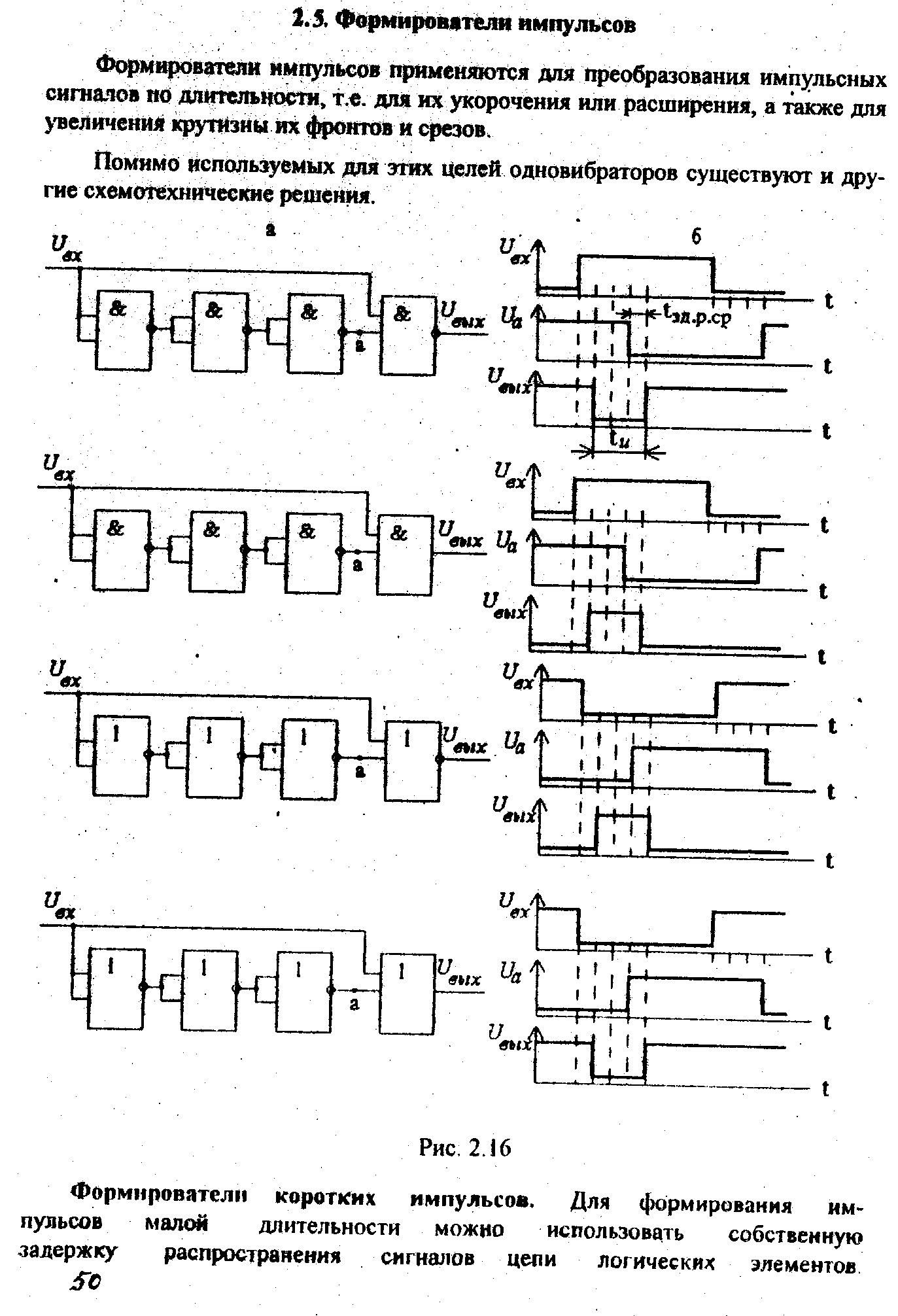

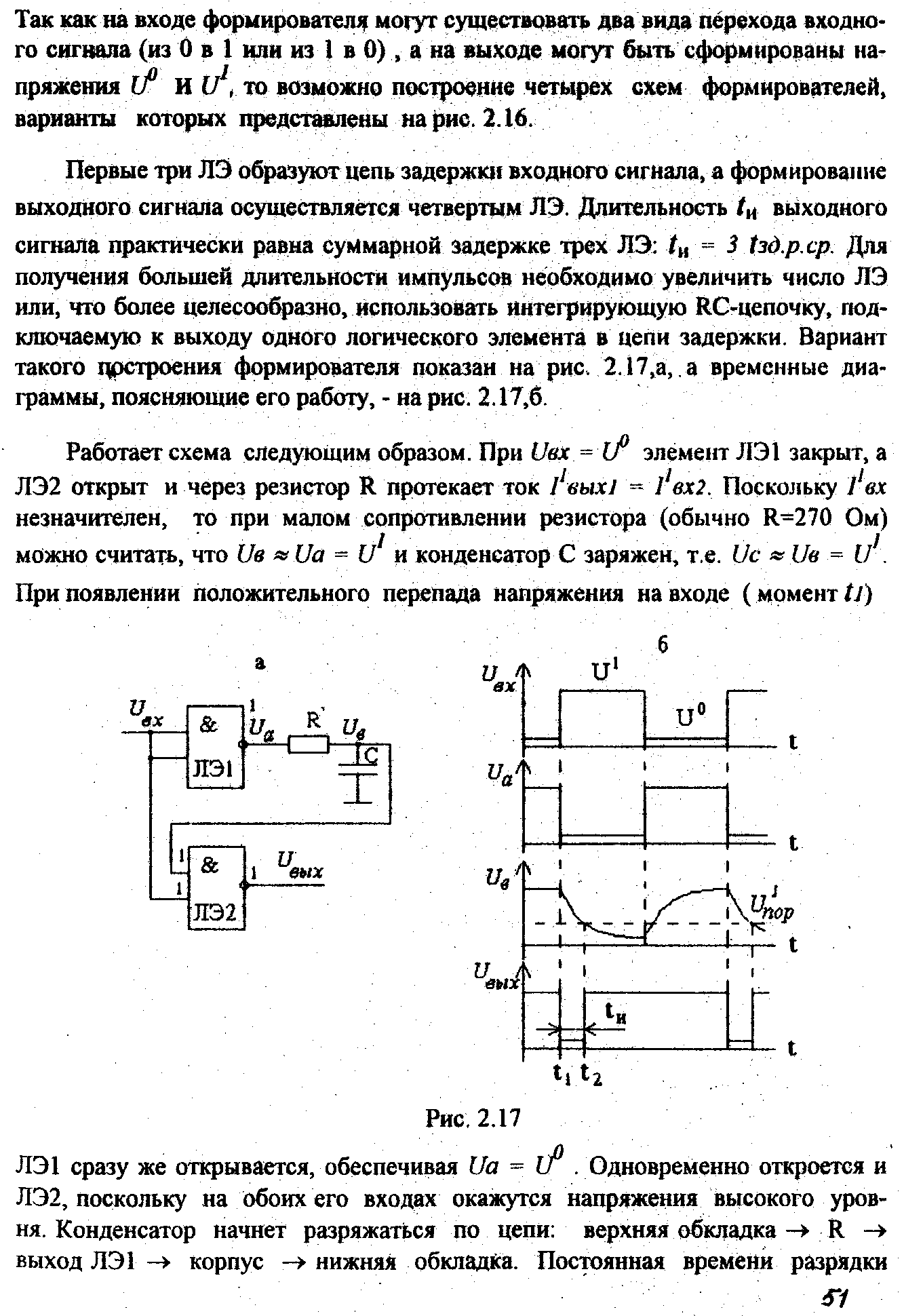

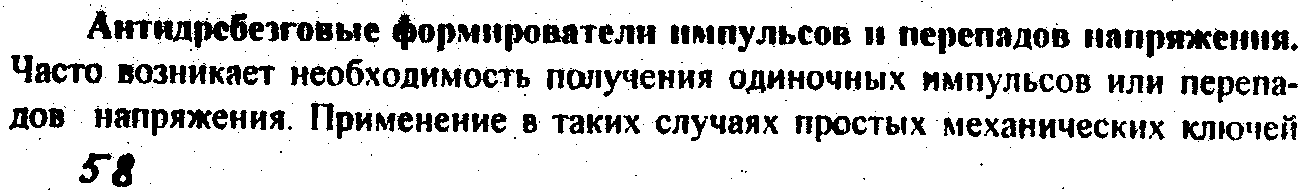

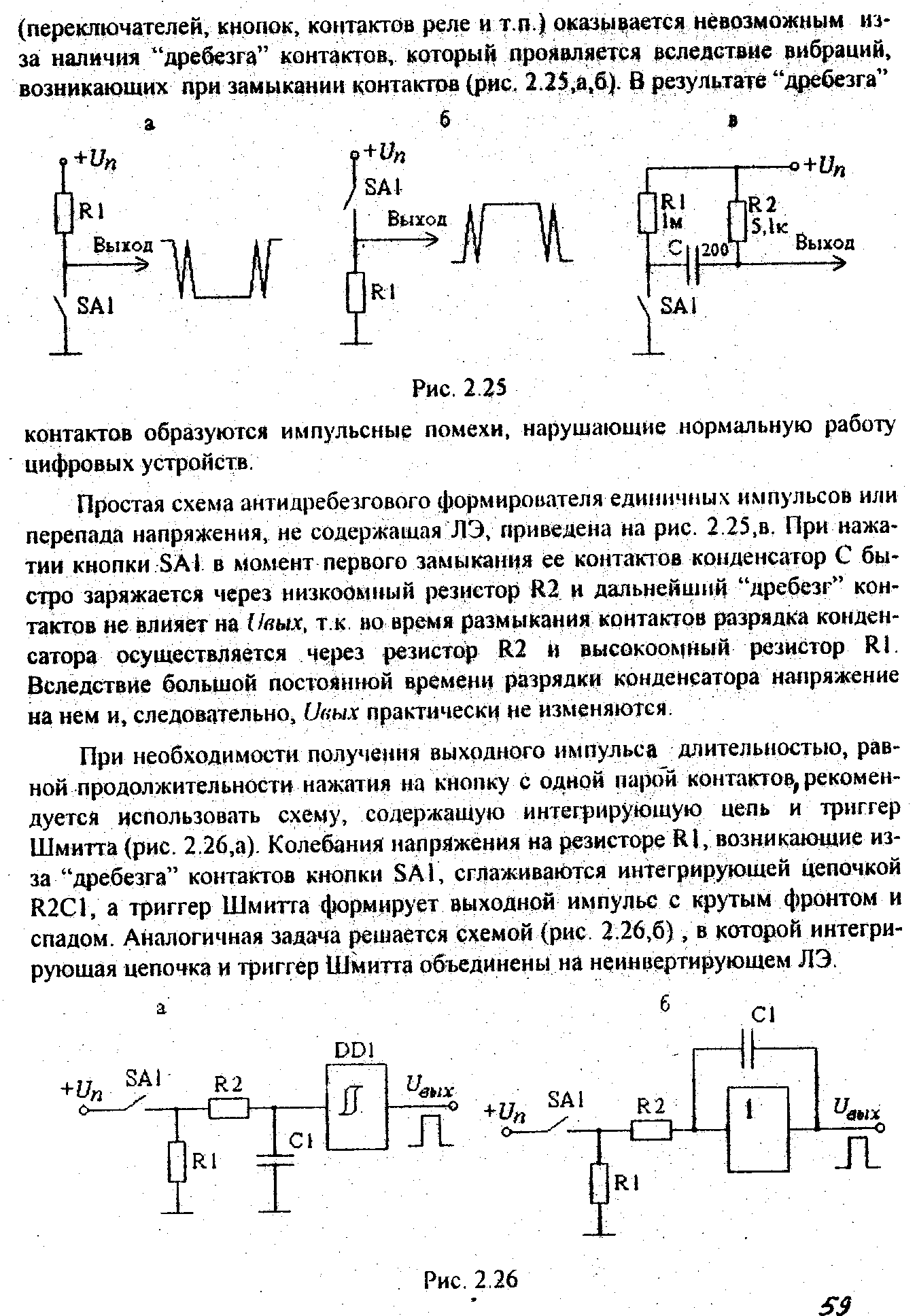

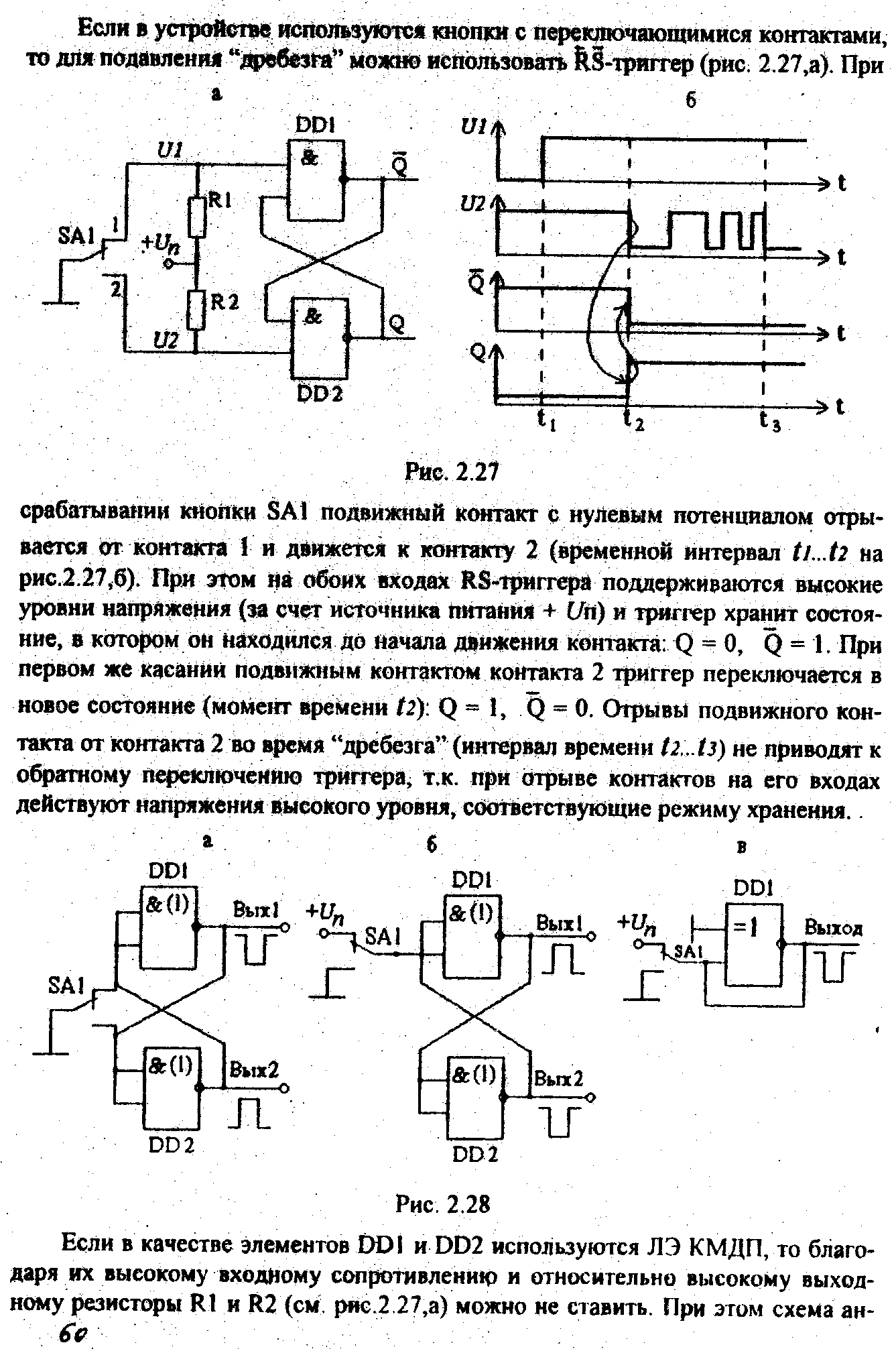

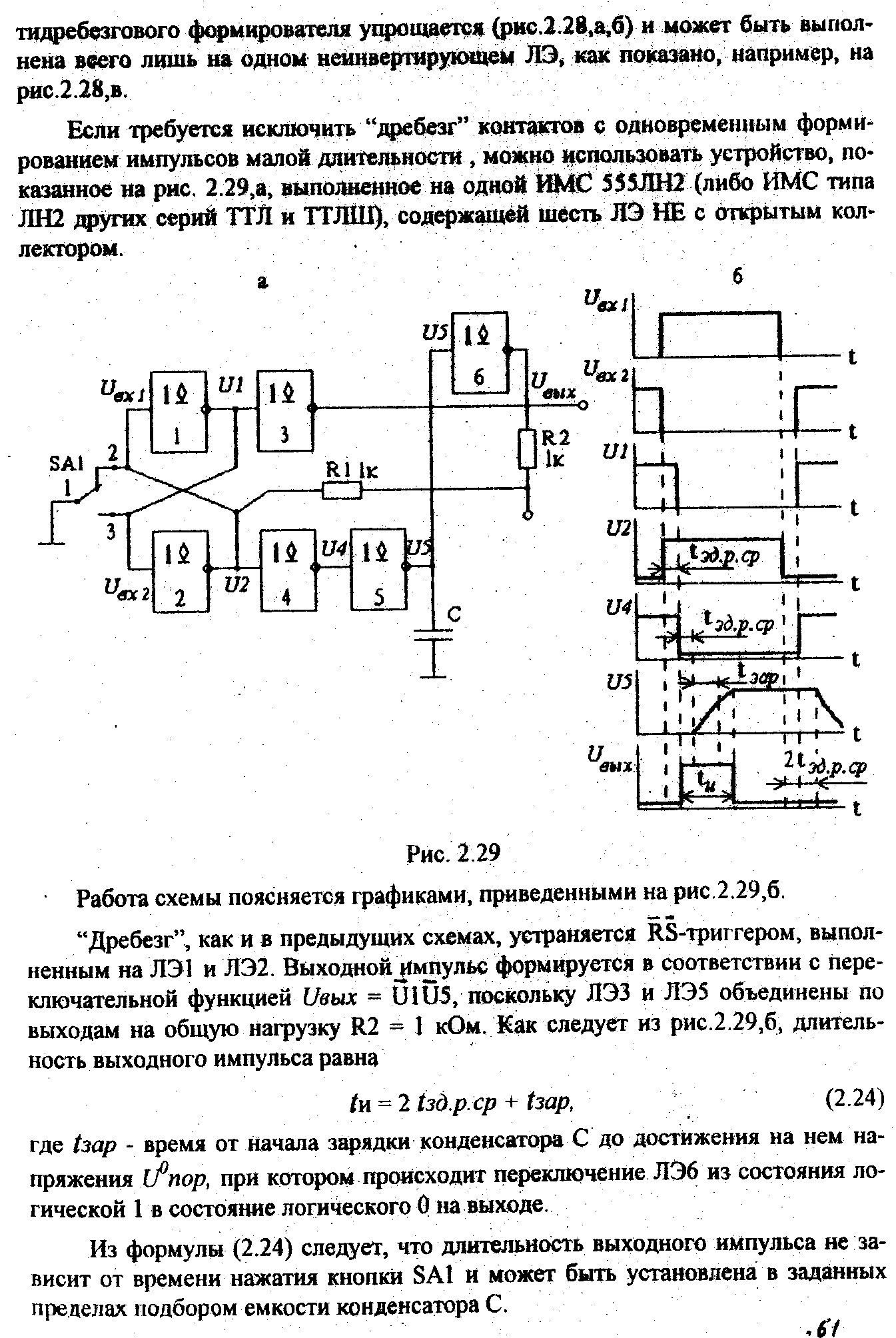

14. Одновибраторы   14_2 Мультивибраторы     15. Формирователи коротких импульсов   16. Антидребезговые формирователи импульсов     17-18. Дешифраторы Дешифратор или декодер (decoder) - это комбинационный операционный узел, преобразующий m-разрядный двоичный позиционный код в n=2m –разрядный унитарный код. Из всех n выходов дешифратора активный уровень появляется только на одном, номер которого определяется двоичным числом, установленном на адресных входах. Дешифраторы применяются в устройствах управления для дешифрации операций или микрокоманд в управляющие сигналы, в запоминающих устройствах для выбора ячейки памяти при записи или считывании информации, для преобразования двоично-десятичного кода в семисегментный, для реализации различных логических функций и др. Если при m входах дешифратор имеет n=2m выходов, то такой дешифратор называется полным. При 2m-1 Условное обозначение дешифратора на 3 входа показано на рис. 14.1.  Входы дешифратора обычно называются адресными и нумеруются не порядковыми номерами, а в соответствии с весами двоичных разрядов, т.е. не 1,2,3,4,5..., а 1, 2, 4, 8, ... Число входов и выходов дешифратора указывают таким бразом: 3-8 (читается «три в восемь»); 4-16, 4-10 (это неполный дешифратор). Функционирование полного дешифратора с m входами определяется табл. 14.1.

В соответствии с этой таблицей список функций, отрабатываемых каждым выходом дешифратора, будет иметь вид:  В зависимости от способа реализации уравнений (14.1) дешифраторы делятся на линейные (одноступенчатые) и матричные (многоступенчатые). | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||