Цифровые устройства. Что такое цифровые микросхемы. Виды цифровых микросхем

Скачать 2.25 Mb. Скачать 2.25 Mb.

|

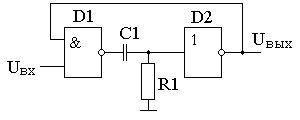

Расширяющие одновибраторы (ждущие мультивибраторы)В расширяющих одновибраторах (ждущих мультивибраторах) длительность входного (запускающего) импульса должна быть короче длительности формируемого импульса. Схема расширяющего одновибратора приведена на рисунке 5. Он выполнен на двух логических элементах. Схема охвачена положительной обратной связью, так как выход второго элемента соединен с входом первого.  Рисунок 5.5. Схема расширяющего одновибратора (ждущего мультивибратора). В исходном состоянии на выходе элемента D2 имеется уровень логической единицы, а на выходе элемента D1 — уровень логического нуля, так как на обоих его входах присутствуют логические единицы. При поступлении на вход запускающего импульса с нулевым потенциалом, на выходе первого логического элемента появится уровень логической единицы, который через конденсатор С поступит на вход второго логического элемента. Логический элемент D2 инвертирует этот сигнал и уровень «0» по цепи обратной связи подается на второй вход логического элемента D1. Теперь даже если на входе снова появится уровень логической единицы, на выходе логического элемента D1 будет сохраняться высокое напряжение. На выходе элемента D2 уровень логического нуля будет присутствовать до тех пор, пока конденсатор C не зарядится до уровня Uc = U1 – Uпор, а напряжение на резисторе R не достигнет порогового уровня Uпор(рисунок 4). Длительность выходного импульса одновибратора может быть определена с помощью выражения где Rвых — выходное сопротивление первого элемента. Uпор — пороговое напряжение логического элемента. Раздел 6 Последовательностные устройства (цифровые устройства с памятью) Глава 1 ТриггерыТриггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки. Простейшая схема, позволяющая запоминать двоичную информацию, может быть построена на двухинверторах, охваченных положительной обратной связью. Эта схема приведена на рисунке 1.1 Рисунок 1.1 Схема простейшего триггера, построенного на инверторах. В этой схеме может быть только два состояния – на выходе Q присутствует логическая единица и на выходе Q присутствует логический ноль. Если логическая единица присутствует на выходе Q, то на инверсном выходе будет присутствовать логический ноль, который после очередного инвертирования подтверждает уровень логической единицы на выходе Q. И наоборот, если на выходе Q присутствует логический ноль, то на инверсном выходе будет присутствовать логическая единица. Такая ситуация будет сохраняться до тех пор пока включено питание. Но вот вопрос — а как записывать в такой триггер информацию? Нам потребуются входы записи нуля и записи единицы. Триггер с подобной возможностью получил название RS триггер. Его мы рассмотрим в следующей главе. Глава 2 RS триггерRS триггер получил название по названию своих входов. Вход S (Set — установить англ.) позволяет устанавливать выход триггера Q в единичное состояние. Вход R (Reset — сбросить англ.) позволяет сбрасывать выход триггера Q (Quit — выход англ.) в нулевое состояние. Для реализации RS триггера воспользуемся логическими элементами "2И-НЕ". Его принципиальная схема приведена на рисунке 2.2 Рисунок 2.2 Схема простейшего rs триггера на схемах "2И-НЕ". Входы R и S инверсные (активный уровень'0'). Рассмотрим работу изображенной на рисунке 2 схемы RS триггера подробнее. Пусть на входы R и S подаются единичные потенциалы. Если на выходе верхнего логического элемента "2И-НЕ" Q присутствует логический ноль, то на выходе нижнего логического элемента "2И-НЕ" появится логическая единица. Эта единица подтвердит логический ноль на выходе Q. Если на выходе верхнего логического элемента "2И-НЕ" Q первоначально присутствует логическая единица, то на выходе нижнего логического элемента "2И-НЕ" появится логический ноль. Этот ноль подтвердит логическую единицу на выходе Q. То есть при единичных входных уровнях схема RS триггера работает точно так же как и схема на инверторах. Подадим на вход S нулевой потенциал. Согласно таблице истинности логического элемента "И-НЕ" на выходе Q появится единичный потенциал. Это приведёт к появлению на инверсном выходе триггера нулевого потенциала. Теперь, даже если снять нулевой потенциал с входа S, на выходе триггера останется единичный потенциал. То есть мы записали в триггер логическую единицу. Точно так же можно записать в триггер и логический ноль. Для этого следует воспользоваться входом R. Так как активный уровень на входах оказался нулевым, то эти входы — инверсные. Составим таблицу истинности RS триггера. Входы R и S в этой таблице будем использовать прямые, то есть и запись нуля, и запись единицы будут осуществляться единичными потенциалами (таблица 2.1). Таблица 2.1. Таблица истинности RS триггера.

RS триггер можно построить и на логических элементах "ИЛИ". Схема RS триггера, построенного на логических элементах "ИЛИ" приведена на рисунке 3. Единственное отличие в работе этой схемы по сравнению с предыдущей схемой RS триггера будет заключаться в том, что сброс и установка триггера будет производиться единичными логическими уровнями. Эти особенности связаны с принципами работы инверсной логики, которые рассматривались ранее. Рисунок 2.3. Схема простейшего RS триггера на схемах "ИЛИ". Входы R и S прямые (активный уровень '1'). Так как RS триггер при построении его на логических элементах "И" и "ИЛИ" работает одинаково, то его условно-графическое изображение на принципиальных схемах тоже одинаково. Условно-графическое изображение RS триггера на принципиальных схемах приведено на рисунке 2.4. Рисунок 2.4. Условно-графическое обозначение RS триггера. |