Цифровые устройства. Что такое цифровые микросхемы. Виды цифровых микросхем

Скачать 2.25 Mb. Скачать 2.25 Mb.

|

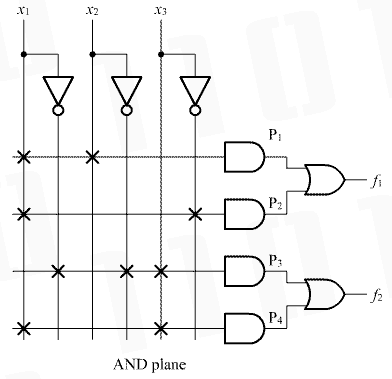

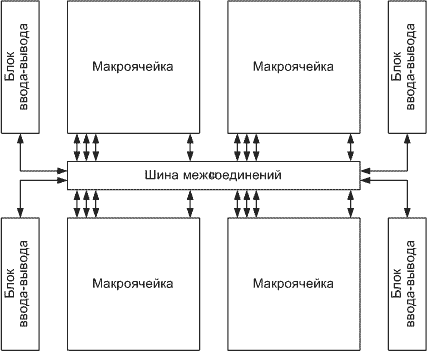

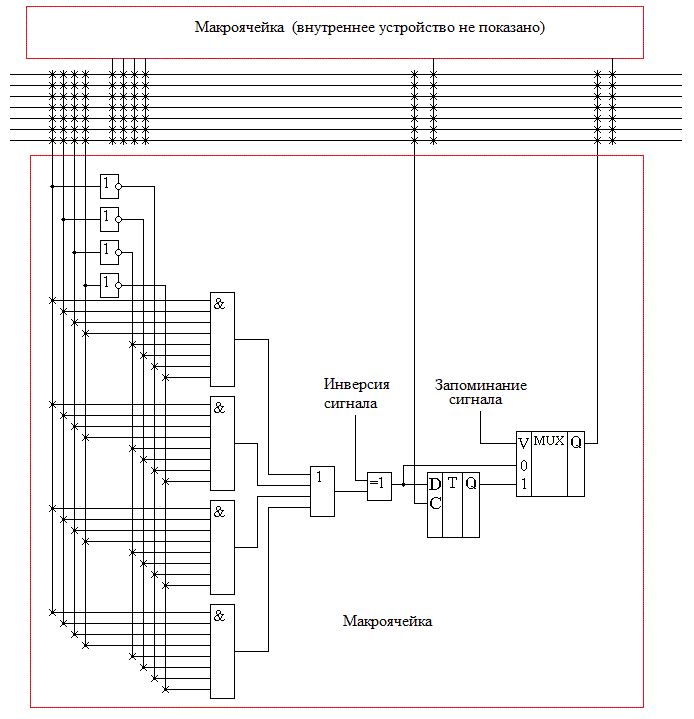

Глава 4Программируемые матрицы логики (PAL).В программируемой логической матрице (ПЛМ) обе матрицы логических элементов "И" и "ИЛИ" программируемы. ПЛИС, в которых матрица логических элементов "И" является программируемой, а матрица логических элементов "ИЛИ" фиксированной, получили название программируемых матриц логики ПМЛ или PAL — Programmable Array Logic (англ.). Поскольку изготовить такие устройства проще, чем ПЛМ, они имеют меньшую стоимость и обладают улучшенными характеристиками, что привело к их высокой популярности. Пример ПМЛ с тремя входами, четырьмя логическими элементами "4ИЛИ", реализующими четыре минтермашестого ранга и двумя выходами представлен на рисунке 4.1.  Рисунок 4.1. Обобщенная структура программируемых матриц логики (ПМЛ) Напомню, что в схеме, приведенной на рисунке 4.1, действует следующее соглашение: Количество входов у логических элементов "И" равно количеству проводников на входе схемы (в данном случае шесть). Соединения, помеченные крестиком подключены ко входам логического элемента, остальные входы логического элемента "И" подключены через резистор к источнику питания, а значит не влияют на результат работы. Представленные на рисунке 4.1 запрограммированные соединения реализуют следующие логические функции: Логические элементы "4И", реализующие термы P1 и P2 аппаратно соединены с первым элементом ИЛИ, а логические элементы "4И", реализующие термы P3 и P4 аппаратно соединены со вторым элементом. Эти соединения не могут программироваться. По сравнению с ПЛМ, программируемые матрицы логики обладает меньшей гибкостью программирования. ПМЛ позволяет использовать четыре терма в качестве входов для элементов ИЛИ, а элементы ИЛИ в ПМЛ имеют только два фиксированных входа. Для компенсации этого недостатка производители ПМЛ производят микросхемы разного объема с различным числом входов и выходов, а также различным числом входов логических элементов "ИЛИ". К программируемым матрицам логики относятся большинство современных ПЛИС небольшой степени интеграции. В качестве примера подобных микросхем можно привести отечественные ИС КМ1556ХП4, КМ1556ХП6, КМ1556ХП8, КМ1556ХЛ8, ранние разработки микросхем ПЛИС (середина-конец 1980-х годов) фирм INTEL, ALTERA, AMD, LATTICE и др. Разновидностью этого класса микросхем являются ПЛИС, имеющие только одну (программируемую) матрицу логических элементов "И", например, микросхема 85C508 фирмы INTEL. Следующий традиционный тип ПЛИС — программируемая макрологика. Подобные микросхемы содержат единственную программируемую матрицу "И-НЕ" или "ИЛИ-НЕ", но за счёт многочисленных инверсных обратных связей способны формировать сложные логические функции. К этому классу относятся, например,ПЛИС PLHS501 и PLHS502 фирмы SIGNETICS, имеющие матрицу "И-НЕ", а также схема XL78C800 фирмы EXEL, реализованная на матрице логических элементов "ИЛИ-НЕ" Глава 5Сложные программируемые логические устройства (CPLD).Программируемые логические матрицы к настоящему времени морально устарели и применяются для реализации относительно простых устройств, для которых не существует готовых микросхем средней степени интеграции. При реализации сложных цифровых схем обычно применяются программируемые логические интегральные схемы (ПЛИС) одним из видов ПЛИС являются сложные программируемые логические устройства (CPLD — Complex PLD). Внутреннее устройство CPLDПрограммируемая логическая интегральная схема CPLD состоит из нескольких макроячеек, расположенных на одном кристалле. Каждая макроячейка соединена с блоками ввода-вывода, осуществляющими формирование необходимого вида входов или выходов для работы с внешними схемами. Кроме того, все макроячейки и блоки ввода-вывода связаны между собой внутренними параллельными шинами. Пример внутренней схемы CPLD приведен на рисунке 5.1.  Рисунок 5.1. Пример внутренней схемы CPLD Приведенная на рисунке 5.1 микросхема CPLD состоит из четырех макроячеек, которые связаны между собой внутренними шинами и соединяются с блоками ввода-вывода. Макроячейка построена подобно ПЛМ микросхеме, к которой на выходе подключен D-триггер. На рисунке 5.2 приведен пример внутренней схемы макроячейки и ее подключение к шине межсоединений.  Рисунок 5.2. Внутренняя схема макроячейки микросхемы CPLD В состав приведенной на рисунке 5.2 макроячейки входят четыре шестивходовых логических элемента "6-И" и 4-входовый логический элемент "4-ИЛИ". Его выход соединен со входом логического элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ". Этот логический элемент предназначен для реализации инверсии логической функции, реализованной ПЛМ-подобной схемой макроячейки. Для этого на его второй вход может подаваться логический ноль или логическая единица. Если этот вход запрограммирован на подачу логической единицы, то логический элемент "ИСКЛЮЧАЮЩЕЕ ИЛИ" будет инвертировать значение, поступающее с выхода логического элемента "4-ИЛИ". Если же на него поступает логический ноль, то схема "ИСКЛЮЧАЮЩЕЕ ИЛИ" будет передавать на выход сигнал без изменения. На выходе макроячейки поставлен двухвходовый мультиплексор, который позволяет передавать на выход текущее значение сигнала с выхода ПЛМ-схемы, или сохраненное в D-триггере. Блок ввода-вывода состоит из элементов с тремя состояниями (буферов). Буфер позволяет настраивать выводы микросхемы на ввод или и на вывод сигналов. Чтобы вывод микросхемы настроить на ввод информации, достаточно перевести буфер, подключенный к данному выводу, в высокоимпедансное состояние. Дальнейший путь прохождения сигнала по микросхеме может быть запрограммирован МОП-ключами, размещенными на пересечениях вертикальных проводников и горизонтальных проводников шинымежсоединений. На схеме это соединение помечается символом 'x'. Необходимо отметить, что если вывод запрограммирован на прием информации, то он не может быть использован в качестве выхода микросхемы. Обычно фирмы-изготовители указывают максимально возможное число входных и выходных линий. Разработка цифровых устройств на CPLDРазработка цифровых устройств на программируемых логических интегральных схемах CPLD практически не отличается от разработки обычных цифровых устройств. Для этого не требуется разбираться в особенностях внутренней структуры микросхемы или проектировать матрицу межсоединений. Разработчики ПЛИС предоставляют пакет САПР в составе которого можно вести разработку цифрового устройства в виде обычных схем в схемном редакторе, а затем транслировать эту схему в файл коммутаций внутренней матрицы межсоединений CPLD. Этот файл загружается в ПЗУ микросхемы CPLD и микросхема превращается в разработанное нами цифровое устройство, фактически в заказную СБИС. В настоящее время разработка цифровых устройств чаще ведется с применением языков программирования схем, таких как AHDL или VHDL. Применение языков программирования вместо примитивов, являющихся аналогами микросхем средней интеграции, позволяет значительно оптимизировать внутреннюю структуру прошивки микросхемы. В качестве примера системы автоматизированного проектирования (САПР) программируемых логических интегральных схем можно привести пакет Quartus II, предлагаемый фирмой Alterra. С работой программного пакета Quartus II можно познакомиться в лабораторной работе 1 " Исследование цифровых устройств на основе программируемых логических интегральных схем (ПЛИС) в среде Quartus II" |