Цифровые устройства. Что такое цифровые микросхемы. Виды цифровых микросхем

Скачать 2.25 Mb. Скачать 2.25 Mb.

|

Глава 7jk триггерПрежде чем начать изучение jk триггера, вспомним принципы работы RS-триггера. Напомню, что в этом триггере есть запрещённые комбинации входных сигналов. Одновременная подача единичных сигналов на входы R и S запрещены. Очень хотелось бы избавиться от этой неприятной ситуации. Таблица истинности jk триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, схема триггера изменена таким образом, что при подаче двух единиц jk триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов jk триггер изменяет своё состояние на противоположное. Таблица истинности jk триггера приведена в таблице 7.1. Таблица 7.1. Таблица истинности jk триггера.

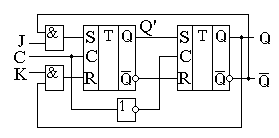

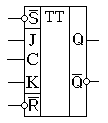

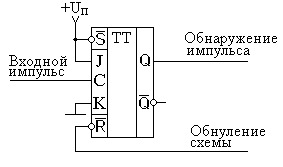

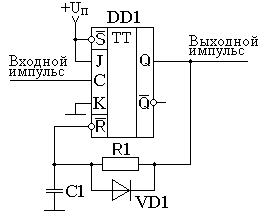

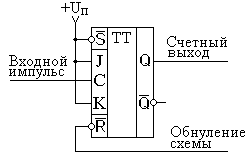

Один из вариантов внутренней схемы JK-триггера приведен на рисунке 7.1.  Рисунок 7.1. Внутренняя схема jk триггера Для реализации счетного режима в схеме jk триггера, приведенной на рисунке 7.1, введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря этой обратной связи на входах R и S первого триггера никогда не может возникнуть запрещенная комбинация. При подаче на входы j и k логической единицы одновременно триггер переходит в счетный режим, подобно T триггеру. Приводить временные диаграммы работы JK-триггера не имеет смысла, так как они совпадают с приведёнными ранее временными диаграммами RS- и T-триггера. Условно-графическое обозначениеJK-триггера приведено на рисунке 7.2.  Рисунок 7.2. Условно-графическое обозначение jk триггера На этом рисунке приведено обозначение типовой цифровой микросхемы jk триггера, выполненной по ТТЛ технологии. В промышленно выпускающихся микросхемах обычно кроме входов jk триггера реализуются входы RS-триггера, которые позволяют устанавливать триггер в заранее определённое исходное состояние. В названиях отечественных микросхем для обозначения jk триггера присутствуют буквы ТВ. Например, микросхема К1554ТВ9 содержит в одном корпусе два jk триггера. В качестве примеров иностранных микросхем, содержащих jk триггеры можно назвать такие микросхемы, как 74HCT73 или 74ACT109. Так как jk триггер является универсальной схемой, то рассмотрим несколько примеров использования этого триггера. Начнем с примера использования JKтриггера в качестве обнаружителя коротких импульсов.  Рисунок 7.3. Схема обнаружения короткого импульса на jk триггере В данной схеме при поступлении на вход "C" импульса триггер переходит в единичное состояние, которое затем может быть обнаружено последующей схемой (например, микропроцессором). Для того, чтобы привести схему в исходное состояние, необходимо подать на вход R уровень логического нуля. Теперь рассмотрим пример построения на jk триггере ждущего мультивибратора. Один из вариантов подобной схемы приведен на рисунке 7.4.  Рисунок 7.4. Схема ждущего мультивибратора, собранного на jk триггере Схема работает подобно предыдущей схеме. Длительность выходного импульса определяется постоянной времени RC цепочки. Диод VD1 предназначен для быстрого восстановления исходного состояния схемы (разряда емкости C). Если быстрое восстановление схемы не требуется, например, когда длительность выходных импульсов гарантированно меньше половины периода следования входных импульсов, то диод VD1 можно исключить из схемы ждущего мультивибратора. В качестве последнего примера применения универсального jk триггера, рассмотрим схему счетного T-триггера. Схема счетного триггера приведена на рисунке 7.5.  Рисунок 7.5. Схема счетного триггера, построенного на jk триггере В схеме, приведенной на рисунке 7.5, для реализации счетного режима работы триггера на входы J и K подаются уровни логической единицы. Если эти входы вывести в качестве отдельного входа, то они образуют отдельный вход разрешения счета T |