Цифровые устройства. Что такое цифровые микросхемы. Виды цифровых микросхем

Скачать 2.25 Mb. Скачать 2.25 Mb.

|

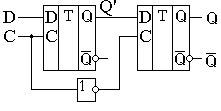

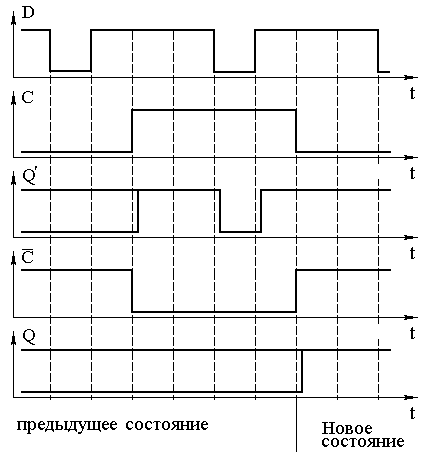

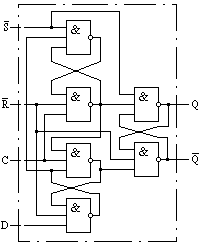

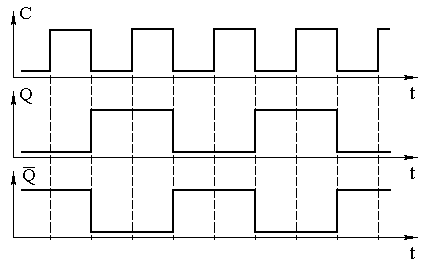

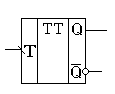

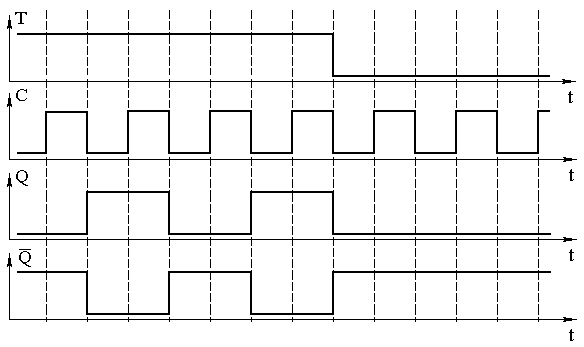

D триггеры, работающие по фронту (динамические D триггеры)Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеальном случае длительность фронта импульса равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять требования к длительности тактового сигнала. Динамический D триггер, запоминающий входную информацию по фронту, может быть построен из двух D триггеров, работающих по потенциалу (статических D триггеров). Сигнал синхронизации C будем подавать на статические D триггеры в противофазе. Схема триггера, запоминающего входную информацию по фронту (динамического D триггера) приведена на рисунке 5.1.  Рисунок 5.1. Схема динамического D триггера, работающего по фронту Рассмотрим работу схемы триггера, приведенной на рисунке 5.1 подробнее. Для этого воспользуемся временными диаграммами, показанными на рисунке 5.2. На этих временных диаграммах обозначение Q' соответствует сигналу на выходе первого статического D триггера. Так как на вход синхронизации второго статического D триггера тактовый сигнал поступает через инвертор, то когда первый D триггер находится в режиме хранения, второй D триггер пропускает сигнал на выход схемы. И наоборот, когда первый D триггер пропускает сигнал с входа схемы на свой выход, второй D триггер находится в режиме хранения.  Рисунок 5.2. Временные диаграммы D триггера Обратите внимание, что сигнал на выходе всей схемы D триггера в целом не зависит от сигнала на входе "D". Если первый D триггер пропускает сигнал данных со своего входа на выход, то второй статический D триггер в это время находится в режиме хранения и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться. В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 5.1 запоминается только в момент изменения сигнала на синхронизирующем входе "C" с единичного потенциала на нулевой. Динамические D триггеры выпускаются в виде готовых микросхем или входят в виде готовых блоков в составе больших интегральных схем, таких как базовый матричный кристалл (БМК) или программируемых логических интегральных схем (ПЛИС). Условно-графическое обозначение динамического D триггера, запоминающего информацию по фронту тактового сигнала, приведено на рисунке 5.3. Рисунок 5.3. Условно-графическое обозначение динамического D триггера То, что триггер запоминает входной сигнал по фронту, отображается на условно-графическом обозначении треугольником, изображённым на выводе входа синхронизации. То, что внутри этого триггера находится два триггера, отображается в среднем поле условно-графического изображения двойной буквой T. Иногда при изображении динамического входа указывают, по какому фронту триггер (или триггеры) изменяет своё состояние. В этом случае используется обозначение входа, как это показано на рисунке 4. Рисунок 5.4. Обозначение динамических входов На рисунке 5.4 (а) обозначен динамический вход, работающий по переднему (нарастающему) фронту сигнала. На рисунке 5.4( б) обозначен динамический вход, работающий по заднему (спадающему) фронту сигнала. Промышленностью выпускаются готовые микросхемы, содержащие динамические триггеры. В качестве примера можно назвать микросхему 1533ТМ2. В этой микросхеме содержится сразу два динамических триггера. Они изменяют своё состояние по переднему (нарастающему) фронту сигнала синхронизации. Внутренняя схема D-триггеров, примененных в микросхеме 1533ТМ2, содержит дополнительные асинхронные входы R и S. Они позволяют принудительно записывать в D-триггер логический ноль или логическую единицу. Принципиальная схема одного триггера микросхемы 1533ТМ2 приведена на рисунке 5.5.  Рисунок 5.5 Принципиальная схема одного триггера микросхемы 1533ТМ2 Глава 6T триггерыT триггер — это счетный триггер. У T триггера имеется только один вход. После поступления на этот вход импульса, состояние T триггера меняется на прямо противоположное. Счётным он называется потому, что он как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггерумеет только до одного. При поступлении второго импульса T триггер снова сбрасывается в исходное состояние. T триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному ранее D триггеру. Использование двух триггеров позволяет избежать неопределенного состояния схемы при разрешающем потенциале на входе синхронизации "C", так как счетные триггеры строятся при помощи схем с обратной связью T триггер можно синтезировать из любого двухступенчатого триггера. Рассмотрим пример синтеза T триггера из динамического D триггера. Для того чтобы превратить D триггер в счётный, необходимо ввести цепь обратной связи с инверсного выхода этого триггера на вход, как показано на рисунке 6.1. Рисунок 6.1. Схема T триггера, построенная на основе D триггера Временная диаграмма T триггера приведена на рисунке 6.2. При построении этой временной диаграммы был использован триггер, работающий по заднему фронту синхронизирующего сигнала.  Рисунок 6.2. Временные диаграммы T триггера Т-триггеры используются при построении схем различных счётчиков, поэтому в составе БИС различного назначения обычно есть готовые модули этих триггеров. Условно-графическое обозначение T триггера приведено на рисунке 6.3.  Рисунок 6.3. Условно-графическое обозначение T триггера Существует еще одно представление T триггера. При разработке схем синхронных двоичных счетчиков важно осуществлять одновременную запись во все его триггеры. В этом случае вход T триггера служит только для разрешения изменения состояния на противоположное, а синхронизация производится отдельным входом "C". Подобная схема T триггера приведена на рисунке 6.4. Рисунок 6.4. Схема синхронного T триггера, построенная на основе D триггера Подобная схема счетного триггера может быть реализована и на JK триггере. Временная диаграмма синхронного T триггера приведена на рисунке 6.5, а его условно-графическое обозначение — на рисунке 6.  Рисунок 6.5. Временные диаграммы синхронного T триггера Рисунок 6.6. Условно-графическое обозначение синхронного T триггера |