(последовательных приближений)

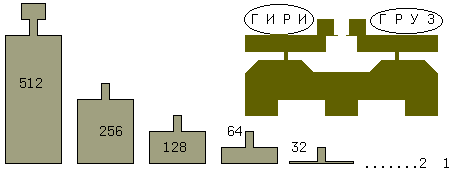

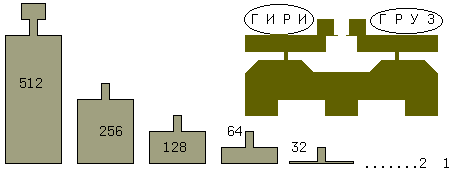

Метод аналогичен взвешиванию груза. В старший разряд регистра записывается 1 (на весы кладется самая большая гиря). Если входное напряжение больше напряжения соответствующего этой единице (груз тяжелее гири), единица в старшем разряде сохраняется (гиря остается на весах), если наоборот - единица заменяется нулем (гиря снимается). Затем единица записывается в предпоследний разряд (ставится следующая гиря) и процесс уравновешивания повторяется. Количество приближений равно числу разрядов преобразователя.

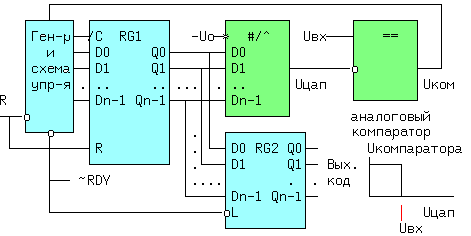

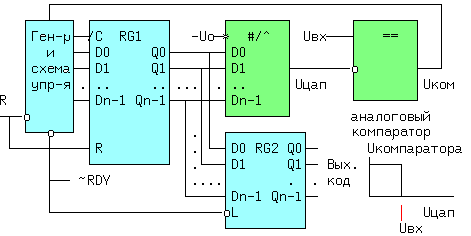

Пусть число разрядов АЦП равно 10 (см. рисунок внизу). ЦАП начинает цикл преобразования с приходом "положительного" импульса на вход R. Высоким уровнем этого сигнала регистр RG1 обнуляется, а переход сигнала R к нулю запускает внутренний генератор и схему управления.

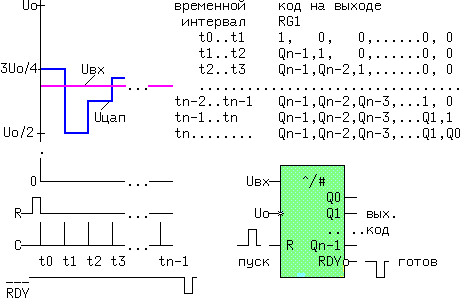

В момент t0 в старший разряд регистра RG1 записывается лог."1" (гиря с наибольшим весом). На выходах регистра RG1 появляется код 10..00(BIN) = 2^(n-1) = 512. ЦАП генерирует напряжение Uцап(n-1) = Uо * 2^(n-1) / 2^n = Uо / 2. Аналоговый компаратор сравнивает напряжения, и если Uцап(n-1) <= Uвх, то единица в старшем разряде сохраняется, если Uцап(n-1) > Uвх, в старший разряд записывается ноль.

В момент t1 единица записывается в предпоследний разряд (n-2) и на выходах регистра RG1 появится код: Qn-1,1,0,0,..,0 равный сумме двух кодов: (Qn-1) * 2^(n-1) - значения старшего бита, полученного в предыдущем такте, и 2^(n-2) = 0100..0(BIN) = 256 - цифрового кода с уменьшенным в два раза "весом". Выходное напряжение Uцап(n-2) = Uцап(n-1) * Q(n-1) + Uо *2^(n-2) / 2^n = (Uo / 2) * Q(n-1) + Uо / 4 опять сравнивается с входным. Если Uцап(n-2) <= Uвх, то единица в предпоследнем разряде сохраняется, если Uцап(n-2) > Uвх, в (n-2)-ой разряд записывается ноль.

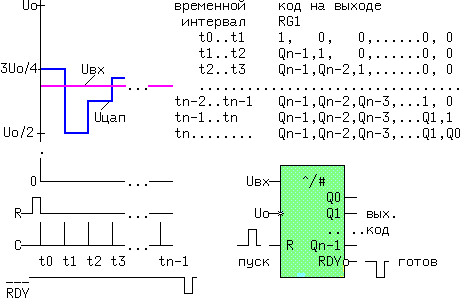

Описанный процесс производится в общей сложности n-раз. В конце цикла преобразования схема управления вырабатывает импульс готовности RDY, который записывает полученный код в выходной регистр. Этот же импульс выводится наружу, для оповещения. Время преобразования Tпреобр = tclk*n. где tclk = t(i+1)-ti период повторения тактовых импульсов внутреннего генератора. Временные диаграммы и условное обозначение АЦП приведены рисунке.

По этому принципу действия выпускаются преобразователи типов 572ПВ1 и 1113ПВ1(А..В). Зависимость прямого двоичного кода D от входного напряжения: D = |(Uвх * 2^n)| / Uo, где D десятичный эквивалент кода на входе АЦП.

7.5 АЦП параллельного типа

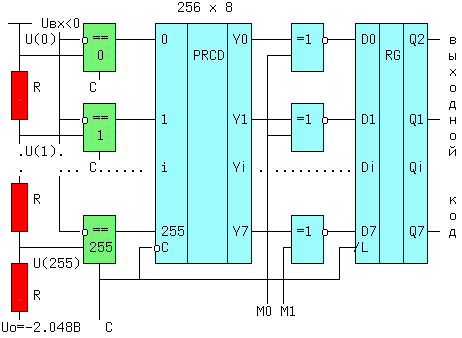

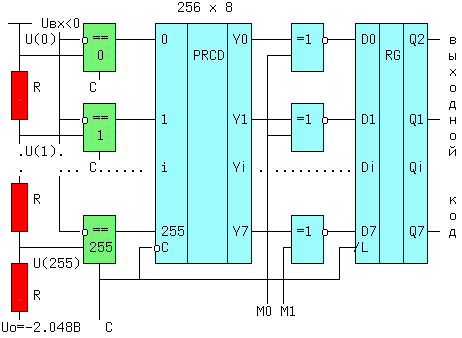

В таком АЦП весь диапазон входного напряжения разбивается на 2^n интервалов. Каждому интервалу соответствует опорное напряжение Uо(i), снимаемое с делителя напряжения, и свой аналоговый компаратор, сравнивающий Uвх с Uо(i).

Для любого входного напряжения в диапазоне (0 .. ¦Uo¦)В найдется такой i-ый компаратор, входное напряжение на котором будет больше или равно опорному U(i). В этом случае на выходе этого компаратора напряжений и на выходах всех компараторов с номерами меньшими i появится "1", а на выходах остальных "0". Приоритетный шифратор сформирует двоичный код, равный наивысшему номеру входа на котором еще присутствует единица. Полученный код через управляемые инверторы/повторители, выполненные на элементах равнозначности, защелкивается в выходном регистре.Учитывая логику работы шифратора, заключающуюся в том, что если на его входах с 1-го по (n-1)-ый одни нули, то единица обязательно должна быть на нулевом входе, можно сэкономить на нулевом компараторе. В этом случае нулевой вход шифратора постоянно подключен к "1", и если входное напряжение находится в пределах 0 <= ¦Uвх¦ < ¦U(1)¦, то нулевой код на выходе генерируется автоматически. Элементы ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ при значении Mi = 0 инвертируют выходной сигнал шифратора, а при Mi = 1 повторяют его. Зависимость выходного кода от режима дана ниже:

M1

|

M0

|

Выходной

код

|

1

|

1

|

прямой

|

0

|

0

|

обратный

|

0

|

1

|

дополнительный прямой

|

1

|

0

|

Дополнительный обратный.

|

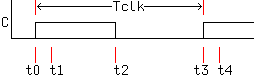

Быстродействие достигается, как за счет параллельного принципа работы, так и за счет конвейерного передвижения информации внутри АЦП (см.рисунок).

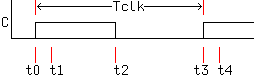

В момент t0 положительным фронтом сигнала C происходит защелкивание кода от предыдущего цикла преобразования. В момент t1 компараторы открываются и начинается сравнение входного напряжения с опорным в текущем цикле. Когда тактовый сигнал C станет равным нулю (момент t2), шифратор отпирается по входу C и начинает преобразование текущего значения Uвх в код. Следующий цикл преобразования начинается в момент t3, когда производится запоминание в регистре текущего кода и его появление на выходах в момент t4, одновременно с началом сравнения на входах компараторов следующего значения напряжения. Время преобразования Tпр = Tclk, т.е. примерно на порядок меньше, чем у АЦП последовательных приближений. По такой схеме выполняются преобразователи типа 1107ПВ1,..5.

|

Скачать 5.23 Mb.

Скачать 5.23 Mb.