КУРС ЛЕКЦИЙ ПО МИКРОПРОЦЕССОРНОЙ ТЕХНИКЕ. Курс лекций по микропроцессорной технике. Введение

Скачать 1.34 Mb. Скачать 1.34 Mb.

|

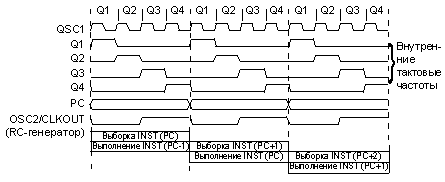

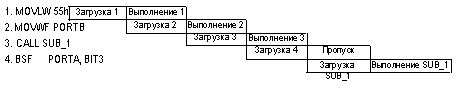

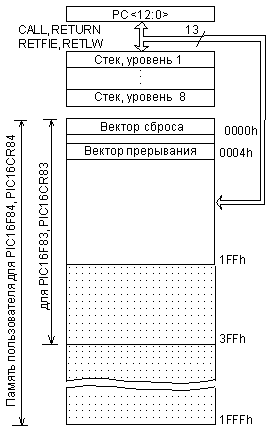

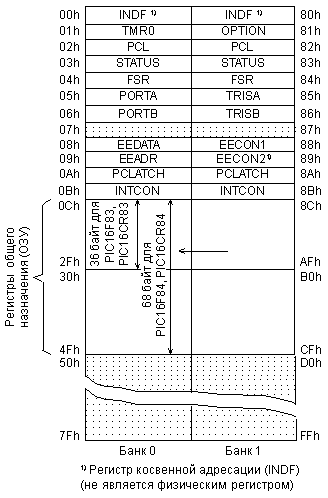

5.2.3. Схема тактирования и цикл выполнения командыВходная тактовая частота, поступающая с вывода OSC1/CLKIN, делится внутри на четыре, и из нее формируются четыре циклические не перекрывающиеся тактовые последовательности Q1, Q2, Q3 и Q4. Счетчик команд увеличивается в такте Q1, команда считывается из памяти программы и защелкивается в регистре команд в такте Q4. Команда декодируется и выполняется в течение последующего цикла в тактах Q1...Q4. Схема тактирования и выполнения команды изображена на рис. 5.2. Цикл выполнения команды состоит из четырех тактов: Q1...Q4. Выборка команды и ее выполнение совмещены по времени таким образом, что выборка команды занимает один цикл, а выполнение – следующий цикл. Эффективное время выполнения команды составляет один цикл. Если команда изменяет счетчик команд (например, команда GOTO), то для ее выполнения потребуется два цикла, как показано на рис. 5.3.  Рис. 5.2. Схема тактирования и выполнения команды.  Рис. 5.3. Выборка команд. Цикл выборки начинается с увеличения счетчика команд в такте Q1. В цикле выполнения команды выбранная команда защелкивается в регистр команд в такте Q1. В течение тактов Q2, Q3 и Q4 происходит декодирование и выполнение команды. В такте Q2 считывается память данных (чтение операнда), а запись происходит в такте Q4. 5.2.4. Организация памяти программ и стекаСчетчик команд в МК PIC16F8Х имеет ширину 13 бит и способен адресовать 8Кх14бит объема программной памяти. Однако физически на кристаллах PIC16F83 и PIC16CR83 имеется только 512х14 памяти (адреса 0000h-01FFh), а в МК PIC16F84 и PIC16CR84 – 1Кх14 памяти (адреса 0000h-03FFh). Обращение к адресам выше 1FFh (3FFh) фактически есть адресация в те же первые 512 адресов (первые 1К адресов). Организация памяти программ и стека приведена на рис. 5.4. В памяти программ есть выделенные адреса. Вектор сброса находится по адресу 0000h, вектор прерывания – по адресу 0004h. Обычно по адресу 0004h располагается подпрограмма идентификации и обработки прерываний, а по адресу 0000h – команда перехода на метку, расположенную за подпрограммой обработки прерываний.  Рис. 5.4. Организация памяти программ и стека. 5.2.5. Организация памяти данныхПамять данных МК разбита на две области. Первые 12 адресов – это область регистров специальных функций (SFR), а вторая – область регистров общего назначения (GPR). Область SFR управляет работой прибора. Обе области разбиты в свою очередь на банки 0 и 1. Банк 0 выбирается обнулением бита RP0 регистра статуса (STATUS). Установка бита RP0 в единицу выбирает банк 1. Каждый банк имеет протяженность 128 байт. Однако для PIC16F83 и PIC16CR83 память данных существует только до адреса 02Fh, а для PIC16F84 и PIC16CR84 – до адреса 04Fh. На рис. 5.5 изображена организация памяти данных.  Рис. 5.5. Организация памяти данных. Некоторые регистры специального назначения продублированы в обоих банках, а некоторые расположены в банке 1 отдельно. Регистры с адресами 0Ch-4Fh могут использоваться как регистры общего назначения, которые представляют собой статическое ОЗУ. Адреса регистров общего назначения банка 1 отображаются на банк 0. Следовательно, когда установлен банк 1, то обращение к адресам 8Ch-CFh фактически адресует банк 0. В регистре статуса помимо бита RP0 есть еще бит RB1, что позволяет обращаться к четырем страницам (банкам) будущих модификаций этого кристалла. К ячейкам ОЗУ можно адресоваться прямо, используя абсолютный адрес каждого регистра, или косвенно, через регистр указатель FSR. Косвенная адресация использует текущее значение разрядов RP1:RP0 для доступа к банкам. Это относится и к EEPROM памяти данных. В обоих случаях можно адресовать до 512 регистров. 5.2.6. Регистры специального назначенияРегистр статуса (STATUS) содержит признаки операции (арифметические флаги) АЛУ, состояние контроллера при сбросе и биты выбора страниц для памяти данных. Назначение бит регистра приведено в табл. 5.3.

Здесь и далее: R — читаемый бит; W — записываемый бит; S — устанавливаемый бит; U — неиспользуемый бит (читается как «0»); -n = 0 или 1 — значение бита после сброса. Регистр статуса доступен для любой команды так же, как любой другой регистр. Однако если регистр STATUS является регистром назначения для команды, влияющей на биты Z, DC или C, то запись в эти три бита запрещается. Кроме того, биты /TO и /PD устанавливаются аппаратно и не могут быть записаны в статус программно. Это следует иметь в виду при выполнении команды с использованием регистра статуса. Например, команда CLRF STATUS обнулит все биты, кроме битов /TO и /PD, а затем установит бит Z=1. После выполнения этой команды регистр статуса может и не иметь нулевого значения (из-за битов /TO и /PD) STATUS=000uu1uu, где u – неизменяемое состояние. Поэтому рекомендуется для изменения регистра статуса использовать только команды битовой установки BCF, BSF, MOVWF, которые не изменяют остальные биты статуса. Воздействие всех команд на биты статуса рассматривается в разделе «Описание системы команд». Регистр конфигурации (OPTION) является доступным по чтению и записи регистром, который содержит управляющие биты для конфигурации предварительного делителя (пределителя), внешних прерываний, таймера, а также резисторов «pull-up» на выводах PORTB. Назначение бит регистра приведено в табл. 5.4.

В том случае, когда пределитель обслуживает сторожевой таймер WDT, таймеру TMR0 назначается коэффициент предварительного деления 1:1. Регистр условий прерывания (INTCON) является доступным по чтению и записи регистром, который содержит биты доступа для всех источников прерываний. Назначение бит регистра приведено в табл. 5.5.

Бит разрешения всех прерываний GIE сбрасывается автоматически при следующих обстоятельствах:

Прерывание INT может вывести процессор из режима SLEEP, если перед входом в этот режим бит INTE был установлен в единицу. Состояние бита GIE также определяет: будет ли процессор переходить на подпрограмму прерывания после выхода из режима SLEEP. Сброс битов – запросов прерываний – должен осуществляться соответствующей программой обработки. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||