КУРС ЛЕКЦИЙ ПО МИКРОПРОЦЕССОРНОЙ ТЕХНИКЕ. Курс лекций по микропроцессорной технике. Введение

Скачать 1.34 Mb. Скачать 1.34 Mb.

|

20 нс). | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Таблица 5.6. Назначение бит регистра EECON1 (адреса 88h). | |||||||

| U | U | U | R/W-0 | R/W-x | R/W-0 | R/S-0 | R/S-x |

| - | - | - | EEIF | WRERR | WREN | WR | RD |

| Бит 7 | Бит 6 | Бит 5 | Бит 4 | Бит 3 | Бит 2 | Бит 1 | Бит 0 |

| Биты 7:5 не используются (читаются как ‘0’) | |||||||

| Бит 4: EEIF: бит запроса прерывания по записи в EEPROM 0 = операция записи не завершена или не начиналась 1 = операция записи завершена (должен быть сброшен программно) | |||||||

| Бит 3: WRERR: бит признака ошибки записи в EEPROM 0 = операция записи завершена 1 = операция записи прервана преждевременно (сбросом по /MCLR или сбросом от WDT) | |||||||

| Бит 2: WREN: бит разрешения записи в EEPROM 0 = запрещена запись в EEPROM 1 = разрешены циклы записи | |||||||

| Бит 1: WR: бит управления записью 0 = цикл записи данных в EEPROM завершен 1 = инициирует цикл записи (сбрасывается аппаратно по завершении записи. Бит WR может быть только установлен (но не сброшен) программно) | |||||||

| Бит 0: RD: бит управления чтением 0 = чтение данных EEPROM не инициировано 1 = инициирует чтение данных EEPROM (чтение занимает один цикл. Бит RD сбрасывается аппаратно. Бит RD может быть только установлен (но не сброшен) программно) | |||||||

Регистр EECON2 не является физическим регистром. Он используется исключительно при организации записи данных в EEPROM. Чтение регистра EECON2 дает нули.

При считывании данных из памяти EEPROM необходимо записать нужный адрес в EEADR регистр и затем установить бит RD EECON1<0> в единицу. Данные появятся в следующем командном цикле в регистре EEDATA и могут быть прочитаны. Данные в регистре EEDATA фиксируются.

При записи в память EEPROM необходимо сначала записать адрес в EEADR-регистр и данные в EEDATA-регистр. Затем следует выполнить специальную последовательность команд, производящую непосредственную запись:

movlw 55h

movwf EECON2

movlw AAh

movwf EECON2

bsf EECON1,WR;установить WR бит, начать запись

Во время выполнения этого участка программы все прерывания должны быть запрещены, для точного выполнения временной диаграммы. Время записи – примерно 10 мс. Фактическое время записи может изменяться в зависимости от напряжения, температуры и индивидуальных свойств кристалла. В конце записи бит WR автоматически обнуляется, а флаг завершения записи EEIF, он же запрос на прерывание, устанавливается.

Для предотвращения случайных записей в память данных предусмотрен специальный бит WREN в регистре EECON1. Рекомендуется держать бит WREN выключенным, кроме тех случаев, когда нужно обновить память данных. Более того, кодовые сегменты, которые устанавливают бит WREN, и те, которые выполняют запись, следует хранить на различных адресах, чтобы избежать случайного выполнения их обоих при сбое программы.

5.2.12. Организация прерываний

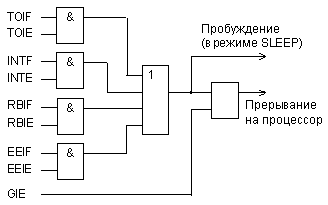

МК подгруппы PIC16F8X имеют четыре источника прерываний:

внешнее прерывание с вывода RB0/INT;

прерывание от переполнения счетчика/таймера TMR0;

прерывание от изменения сигналов на линиях порта RB<7:4>;

прерывание по окончании записи данных в EEPROM.

Все прерывания имеют один и тот же вектор/адрес – 0004h. Однако в управляющем регистре прерываний INTCON соответствующим битом-признаком записывается, от какого именно источника поступил запрос прерывания. Исключение составляет прерывание по завершении записи в EEPROM, признак которого находится в регистре EECON1.

Бит общего разрешения/запрещения прерывания GIE (INTCON <7>) разрешает (если = 1) все индивидуально незамаскированные прерывания или запрещает их (если = 0). Каждое прерывание в отдельности может быть дополнительно разрешено/запрещено установкой/сбросом соответствующего бита в регистре INTCON.

Бит GIE при сбросе обнуляется. Когда начинает обрабатываться прерывание, бит GIE обнуляется, чтобы запретить дальнейшие прерывания, адрес возврата посылается в стек, а в программный счетчик загружается адрес 0004h. Время реакции на прерывание для внешних событий, таких как прерывание от ножки INT или порта B, составляет приблизительно пять циклов. Это на один цикл меньше, чем для внутренних событий, таких как прерывание по переполнению от таймера TMR0. Время реакции всегда одинаковое.

В подпрограмме обработки прерывания источник прерывания может быть определен по соответствующему биту в регистре признаков. Этот флаг-признак должен быть программно сброшен внутри подпрограммы. Признаки запросов прерываний не зависят от соответствующих маскирующих битов и бита общего маскирования GIE.

Команда возврата из прерывания RETFIE завершает прерывающую подпрограмму и устанавливает бит GIE, чтобы опять разрешить прерывания.

Логика прерываний контроллера изображена на рис. 5.14.

Рис. 5.14. Логика прерываний микроконтроллера.

Внешнее прерывание на ножке RB0/INT осуществляется по фронту: либо по нарастающему (если в регистре OPTION бит INTEDG=1), либо по спадающему (если INTEDG=0). Когда фронт обнаруживается на ножке INT, бит запроса INTF устанавливается в единицу (INTCON <1>). Это прерывание может быть замаскировано сбросом управляющего бита INTE в ноль (INTCON <4>). Бит запроса INTF необходимо очистить прерывающей программой перед тем, как опять разрешить это прерывание. Прерывание INT может вывести процессор из режима SLEEP, если перед входом в этот режим бит INTE был установлен в единицу. Состояние бита GIE также определяет, будет ли процессор переходить на подпрограмму прерывания после выхода из режима SLEEP.

Переполнение счетчика TMR0 (FFh->00h) устанавливает в единицу бит запроса T0IF (INTCON<2>). Это прерывание может быть разрешено/запрещено установкой/сбросом бита маски T0IE (INTCON<5>). Сброс запроса T0IF – дело программы обработки.

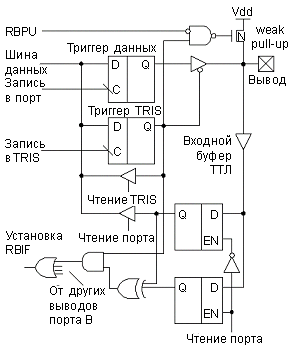

Любое изменение сигнала на одном из четырех входов порта RB<7:4> устанавливает в единицу бит RBIF (INTCON<0>). Это прерывание может быть разрешено/запрещено установкой/сбросом бита маски RBIE (INTCON<3>). Сброс запроса RBIF – дело программы обработки.

Признак запроса прерывания по завершении записи в EEPROM, EEIF (EECON1<4>) устанавливается в единицу по окончании автоматической записи данных в EEPROM. Это прерывание может быть замаскировано сбросом бита EEIE (INTCON<6>). Сброс запроса EEIF – дело программы обработки.

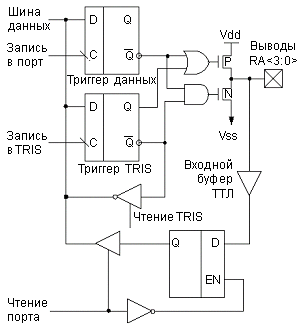

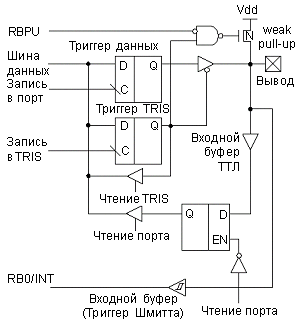

1) Этот буфер имеет вход триггера Шмитта, когда конфигурируется в режиме RC-генератора и КМОП-вход в остальных случаях.

2) Этот буфер имеет вход триггера Шмитта, когда конфигурируется в качестве входа внешнего прерывания.

3) Этот буфер имеет вход триггера Шмитта, когда используется в режиме последовательного программирования.

4) Этот буфер имеет вход триггера Шмитта, когда используется в режиме последовательного программирования.

5.2.13. Специальные функции

Микроконтроллеры подгруппы PIC16F8X имеют набор специальных функций, предназначенных для расширения возможностей системы, минимизации стоимости, исключения навесных компонентов, обеспечения минимального энергопотребления и защиты кода от считывания. В PIC16F8X реализованы следующие специальные функции:

сброс;

сторожевой таймер (WDT);

режим пониженного энергопотребления (SLEEP);

выбор типа генератора;

защита кода от считывания;

биты идентификации;

последовательное программирование в составе схемы.

В PIC16F8X существуют различия между вариантами сбросов:

сброс по включению питания;

сброс по внешнему сигналу /MCLR при нормальной работе;

сброс по внешнему сигналу /MCLR в режиме SLEEP;

сброс по окончании задержки таймера WDT при нормальной работе;

сброс по окончании задержки таймера WDT в режиме SLEEP.

Для реализации сброса по включению питания в МК подгруппы PIC16F8X предусмотрен встроенный детектор включения питания. Таймер установления питания (PWRT) начинает отсчет времени после того, как напряжение питания пересекает уровень около 1,2…1,8 Вольт. По истечении выдержки около 72мс считается, что напряжение достигло номинала и запускается другой таймер – таймер запуска генератора (OST), формирующий выдержку на стабилизацию кварцевого генератора. Программируемый бит конфигурации позволяет разрешать или запрещать выдержку от встроенного таймера установления питания. Выдержка запуска меняется в зависимости от экземпляров кристалла, от питания и температуры. Таймер на стабилизацию генератора отсчитывает 1024 импульса от начавшего работу генератора. Считается, что кварцевый генератор за это время выходит на режим. При использовании RC генераторов выдержка на стабилизацию не производится.

Если сигнал /MCLR удерживается в низком состоянии достаточно долго (дольше времени всех задержек), тогда после перехода /MCLR в высокое состояние программа начнет выполняться немедленно. Это необходимо в тех случаях, когда требуется синхронно запустить в работу несколько PIC-контроллеров через общий для всех сигнал /MCLR.

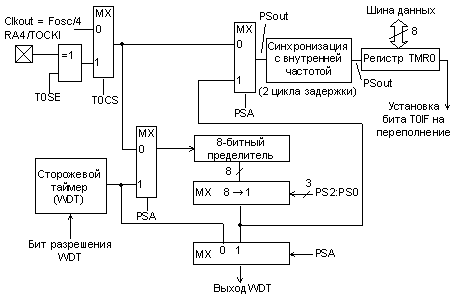

Микроконтроллеры подгруппы PIC16F8X имеют встроенный сторожевой таймер WDT. Для большей надежности он работает от собственного внутреннего RC-генератора и продолжает функционировать, даже если основной генератор остановлен, как это бывает при исполнении команды SLEEP. Таймер вырабатывает сигнал сброса. Выработка таких сбросов может быть запрещена путем записи нуля в специальный бит конфигурации WDTE. Эту операцию производят на этапе прожига микросхем.

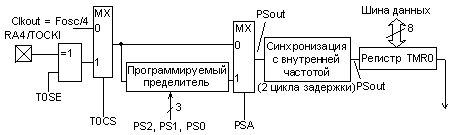

Номинальная выдержка WDT составляет 18 мс (без использования делителя). Она зависит от температуры, напряжения питания, особенностей типов микросхем. Если требуются большие задержки, то к WDT может быть подключен встроенный пределитель с коэффициентом деления до 1:128, который программируется битами PS2:PS0 в регистре OPTION. В результате могут быть реализованы выдержки до 2,3 секунд.

Команды «CLRWDT» и «SLEEP» обнуляют WDT и пределитель, если он подключен к WDT. Это запускает выдержку времени сначала и предотвращает на некоторое время выработку сигнала сброса. Если сигнал сброса от WDT все же произошел, то одновременно обнуляется бит /TO в регистре статуса. В приложениях с высоким уровнем помех содержимое регистра OPTION подвержено сбою. Поэтому регистр OPTION должен обновляться через равные промежутки времени.

Состояние регистров МК после сброса представлено в табл. 5.7.

Некоторые из специальных регистров при сбросе не инициализируются. Они имеют случайное состояние при включении питания и не изменяются при иных видах сброса. Другая часть специальных регистров инициализируется в «состояние сброса» при всех видах сброса, кроме сброса по окончанию задержки таймера WDT в режиме SLEEP. Просто этот сброс рассматривается как временная задержка в нормальной работе. Есть еще несколько исключений. Счетчик команд всегда сбрасывается в ноль (0000h). Биты регистра статуса /TO и /PD устанавливаются или сбрасываются в зависимости от варианта сброса. Эти биты используются программой для определения природы сброса (см. табл. 5.3).

| Таблица 5.7. Состояние регистров МК после сброса. | |||

| Регистр | Адрес | Сброс по включению | Другие виды питания сброса |

| W | - | xxxx xxxx | uuuu uuuu |

| INDF | 00h | —— —— | —— —— |

| TMR0 | 01h | xxxx xxxx | uuuu uuuu |

| PCL | 02h | 0000 0000 | 0000 0000 |

| STATUS | 03h | 0001 1xxx | 000q quuu |

| FSR | 04h | xxxx xxxx | uuuu uuuu |

| PORT A | 05h | —x xxxx | —u uuuu |

| PORT B | 06h | xxxx xxxx | uuuu uuuu |

| TRIS A | 85h | —1 1111 | —1 1111 |

| TRIS B | 86h | 1111 1111 | 1111 1111 |

| OPTION | 81h | 1111 1111 | 1111 1111 |

| EEDATA | 08h | xxxx xxxx | uuuu uuuu |

| EEADR | 09h | xxxx xxxx | uuuu uuuu |

| EECON1 | 88h | —0 0000 | —0 q000 |

| EECON2 | 89h | —— —— | —— —— |

| PCLATH | 0Ah | —0 0000 | —0 0000 |

| INTCON | 0Bh | 0000 000x | 0000 000u |

| Здесь: x — неизвестное значение; u — неизменяемый бит; «–» — неиспользуемый бит (читается как «0»); q — значение бита зависит от условий сброса. | |||

Режим пониженного энергопотребления SLEEP предназначен для обеспечения очень малого тока потребления в ожидании (менее 1 мкА при выключенном сторожевом таймере). Выход из режима SLEEP возможен по внешнему сигналу сброса или по окончании выдержки сторожевого таймера.

Кристаллы PIC16F8X могут работать с четырьмя типами встроенных генераторов. Пользователь может запрограммировать два конфигурационных бита (FOSC1 и FOSC0) для выбора одного из четырех режимов: RC, LP, XT, HS. Здесь XT – стандартный кварцевый генератор, HS – высокочастотный кварцевый генератор, LP – низкочастотный генератор для экономичных приложений. Микроконтроллеры PIC16F8X могут тактироваться и от внешних источников.

Генератор, построенный на кварцевых или керамических резонаторах, требует периода стабилизации после включения питания. Для этого встроенный таймер запуска генератора держит устройство в состоянии сброса примерно 18 мс после того, как сигнал на /MCLR ножке кристалла достигнет уровня логической единицы.

Возможность выбора типа генератора позволяет эффективно использовать микроконтроллеры семейства в различных приложениях. Применение RC генератора позволяет уменьшить стоимость системы, а низкочастотный LP-генератор сокращает энергопотребление.

Программный код, который записан в кристалл, может быть защищен от считывания при помощи установки бита защиты (CP) в слове конфигурации в ноль. Содержимое программы не может быть прочитано так, чтобы с ним можно было работать. Кроме того, при установленном бите защиты невозможно изменять программу. То же относится и к содержимому памяти данных EEPROM.

Если установлена защита, то бит CP можно стереть только вместе с содержимым кристалла. Сначала будет стерта EEPROM программная память и память данных, и в последнюю очередь – бит защиты кода CP. При считывании защищенного кристалла чтение любого адреса памяти даст результат вида 0000000XXXXXXX(двоичный код), где X – это 0 или 1.

Память данных EEPROM невозможно проверить после установки бита защиты.

Для выбора различных режимов работы используются биты конфигурации. Микроконтроллеры подгруппы PIC16F8X имеют 5 или 6 бит конфигурации, которые хранятся в EEPROM и устанавливаются на этапе программирования кристалла. Эти биты могут быть запрограммированы (читается как «0») или оставлены незапрограммированными (читается «1«) для выбора подходящего варианта конфигурации устройства. Они расположены в EEPROM-памяти по адресу 2007h. Пользователю следует помнить, что этот адрес находится ниже области кодов и недоступен программе.

Назначение бит конфигурации МК PIC16CR83 и PIC16CR84 приведено в табл. 5.8.

| Таблица 5.8. Назначение бит конфигурации МК PIC16CR83 и PIC16CR84. | ||||||

| R-u | R/P-u | R-u | R-u | R-u | R-u | R-u |

| CP | DP | CP | /PWRTE | WDTE | FOSC1 | FOSC0 |

| Бит 13:8 | Бит 7 | Бит 6:4 | Бит 3 | Бит 2 | Бит 1 | Бит 0 |

| Биты 13:8 CP: бит защиты памяти программ 0 = память программ защищена 1 = защита отсутствует | ||||||

| Бит 7 DP: бит защиты памяти данных 0 = память данных защищена 1 = защита отсутствует | ||||||

| Биты 6:4 CP: бит защиты памяти программ 0 = память программ защищена 1 = защита отсутствует | ||||||

| Бит 3 /PWRTE: бит использования таймера по включению питания 0 = таймер используется (есть задержка) 1 = таймер не используется | ||||||

| Бит 2: WDTE: бит использования сторожевого таймера 0 = WDT не используется 1 = WDT используется | ||||||

| Биты 1:0 FOSC1:FOSC0: бит выбора типа генератора 11 = генератор RC 10 = генератор HS 01 = генератор XT 00 = генератор LP | ||||||

| Здесь: P — программируемый бит; – n = значение по сбросу после включения питания. | ||||||

Назначение бит конфигурации МК PIC16F83 и PIC16F84 приведено в табл. 5.9.

| Таблица 5.9. Назначение бит конфигурации МК PIC15F83 и PIC16F84. | ||||

| R-u | R-u | R-u | R-u | R-u |

| CP | /PWRTE | WDTE | FOSC1 | FOSC0 |

| Бит 13:4 | Бит 3 | Бит 2 | Бит 1 | Бит 0 |

| Биты 13:4 CP: бит защиты памяти программ 0 = память программ защищена 1 = защита отсутствует | ||||

| Бит 3 /PWRTE: бит использования таймера по включению питания 0 = таймер используется (есть задержка) 1 = таймер не используется | ||||

| Бит 2: WDTE: бит использования сторожевого таймера 0 = WDT не используется 1 = WDT используется | ||||

| Биты 1:0 FOSC1:FOSC0: бит выбора типа генератора 11 = генератор RC 10 = генератор HS 01 = генератор XT 00 = генератор LP | ||||

Четыре слова памяти, расположенные по адресам 2000h-2003h, предназначены для хранения идентификационного кода (ID) пользователя, контрольной суммы или другой информации. Как и слово конфигурации, они могут быть прочитаны или записаны только с помощью программатора. Доступа из программы к ним нет.

Микроконтроллеры подгруппы PIC16F8X могут быть запрограммированы последовательным способом в составе устройства. Для этого используется всего пять линий: две для данных и тактового сигнала и три для земли, напряжения питания и программирующего напряжения. Разработчик может создать и смакетировать устройство с незапрограммированным прибором, а перед использованием ввести в него программу.