Преобразователи кодов. Лекция 15. Преобразователи кодов, шифраторы и дешифраторы Преобразователи кодов. Операция изменения кода числа называется его перекодированием.

Скачать 180.73 Kb. Скачать 180.73 Kb.

|

|

Преобразователи кодов, шифраторы и дешифраторы Лекция 15. Преобразователи кодов, шифраторы и дешифраторы Преобразователи кодов. Операция изменения кода числа называется его перекодированием. Интегральные микросхемы, выполняющие эти операции, называются преобразователями кодов. Преобразователи кодов бывают простые и сложные. К простым относятся преобразователи, которые выполняют стандартные операции изменения кода чисел, например, преобразований двоичного кода в одинарный или обратную операцию. Сложные преобразователи кодов выполняют нестандартные преобразования кодов и их схемы приходится разрабатывать каждый раз с помощью алгебры логики. Будем считать, что преобразователи кодов имеют п входов и k выходов. Соотношения между п и k могут быть любыми: n=k, n

низкий и максимальная частота счета /„акс- Большинство перечисленных параметров определяется серией микросхем и типом применяемой логики. Интегральные микросхемы регистров. В наименовании регистров их функциональное назначение обозначается буквами ИР. В остальном условное обозначение регистров совпадает с обозначением счетчиков. В табл. 14.6 приведены некоторые типы регистров различных серий Лекция 15. Преобразователи кодов, шифраторы и дешифраторы Преобразователи кодов. Операция изменения кода числа называется его перекодированием. Интегральные микросхемы, выполняющие эти операции, называются преобразователями кодов. Преобразователи кодов бывают простые и сложные. К простым относятся преобразователи, которые выполняют стандартные операции изменения кода чисел, например, преобразований двоичного кода в одинарный или обратную операцию. Сложные преобразователи кодов выполняют нестандартные преобразования кодов и их схемы приходится разрабатывать каждый раз с помощью алгебры логики. Будем считать, что преобразователи кодов имеют п входов и k выходов. Соотношения между п и k могут быть любыми: n=k, n • преобразователи двоично-десятичного кода в двоичный код; • преобразователи двоичного кода в двоично-десятичный код; • преобразователи двоичного кода в код Грея, • преобразователи двоичного кода в код управления сегментными индикаторами, • преобразователи двоичного или двоично-десятичного кода в код управления шкальными или матричными индикаторами. В качестве примера рассмотрим преобразователь двоичного кода в код управления семисегментным цифровым индикатором, приведенный на рис. 15.1 а Сам индикатор представляет собой полупроводниковый прибор, в котором имеются семь сегментов, выполненных из светодиодов. Включением и выключением отдельных сегментов можно получить светящееся изображение отдельных цифр или знаков. Конфигурация и расположение сегментов индикатора показаны на рис. 15.1 а. Каждой цифре соответствует свой набор включения определенных сегментов индикатора. Соответствующая таблица приведена на рис 15 1 б В этой таблице также приведены двоичные коды соответствующих цифр Такие индикаторы позволяют получить светящееся изображение не только цифр от 0 до 9, но других знаков, используемых в 8- и 16-ричной системах счисления. Для управления такими индикаторами выпускаются интегральные микросхемы типов КР514ИД1, К514ИД2, К133ПП1, 176ИД2, 176ИДЗ, 564ИД4, 564ИД5 и др. Преобразователи кодов, выполненные по технологии КМОП, можно использовать не только со светодиодными индикаторами, но и с жидкокристаллическими или катодолюминисцентными Шкальные индикаторы представляют собой линейку светодиодов с одним общим анодом или катодом. Преобразователи двоичного кода в код управления

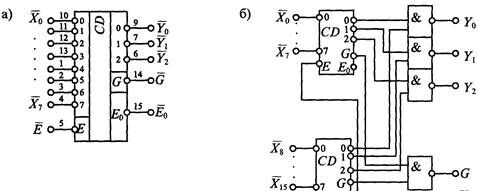

Рис 15 1 Схема преобразователя кода для семисегментного индикатора (а) и таблица соотвествия кодов (б) шкальным индикатором обеспечивают перемещение светящегося пятна, определяемое двоичным кодом на адресном входе Матричные индикаторы представляют собой наборы светодиодов, расположенных по строкам и столбцам Наиболее распространенными матричними индикаторами являются индикаторы, имеющие 5 столбцов и 7 строк (формат 5х7). Количество светодиодов в таких матричных индикаторах равно 35 Управление такими индикаторами производится путем выбора номера строки и номера столбца, на пересечении которых находится нужный светодиод Примером такого матричного индикатора является прибор АЛС340А с форматом 5х7 светодиодов (рис 15 2 а) Для управления матричными индикаторами вьшускаются микросхемы, в которых положение светодиода задается номерами столбца i и строки ], причем не все комбинации ; и у используются Такие преобразователи кодов называются неполными К ним относятся микросхемы К155ИД8 и К155ИД9 (рис. 15.26). Примерами простейших преобразователей кодов, которые широко применяются в цифровых устройствах, являются шифраторы и дешифраторы. Шифратором называют кодовый преобразователь, который имеет п входов и k выходов, и при подаче сигнала на один из входов (обязательно только на один) на выходах появляется двоичный код возбужденного входа Очевидно, что число выходов и входов в полном шифраторе связано соотношением Рассмотрим принцип построения шифратора на примере преобразования 8-разрядного единичного кода в двоичный код Схема такого шифратора приведена на рис 15 3 а, а его условное схематичное обозначение — на рис 15.3 б. Если все входные сигналы имеют нулевое значение, то на выходе шифратора будем иметь нулевой код Yo=Y=Yi=0 Младший выход, т е. выход с весовым коэффициентом, равным 1, должен возбуждаться при входном сигнале на любом из нечетных входов, так как все  Рис 152 Устройство матричного индикатора формата 7х5 (а) и включение микросхемы К155ИД9 неполного дешифратора матричного индикатора (б)  Рис 15.3. Схема шифратора восьмиразрядного единичного кода (а) и его условное схематическое обозначение (б) нечетные номера в двоичном представлении содержат единицу в младшем разряде. Следовательно, младший выход — это выход схемы ИЛИ, к входам которой подключены все входы с нечетными номерами. Следующий выход имеет вес два. Он должен возбуждаться при подаче сигналов на входы с номерами 2, 3, 6, 7, т. е. с номерами, имеющими в двоичном представлении единицу во втором разряде. Таким образом, входы элемента ИЛИ должны быть подключены к входным сигналам, имеющим указанные номера. Старший разряд двоичного кода формируется из входных сигналов с номерами 4, 5, 6 и 7, т. е. из четырех старших разрядов единичного кода. Все рассмотренные состояния шифратора можно увидеть в таблице, приведенной на рис. 15.1 б. Как следует из выполненного построения, при помощи шифратора можно сократить (сжать) информацию для передачи ее по меньшему числу линий связи, так как k В цифровых системах с помощью шифраторов обеспечивается связь между различными устройствами посредством ограниченного числа линий связи. Так, например, в кнопочных пультах управления ввод числовых данных обычно выполняется в унитарном коде посредством нажатия одной из десяти кнопок, а ввод данных в микропроцессор выполняется в двоичном коде. Для преобразования кода кнопочного пульта в код микропроцессора также используется шифратор «из 10 в 4». Однако, поскольку четырехразрядный двоичный код имеет не 10, а 16 возможных комбинаций, такой шифратор будет неполным. Состояние выходов шифратора, изображенного на рис. 15.3 а, приведено в табл. 15.1. Из этой таблицы следует, что для шифраторов должно выполняться условие ;с,х,=0 при i^j. Если сигналы, поступающие на вход шифратора, являются независимыми, что бывает, например, при нажатии одновременно нескольких кнопок на кнопочном пульте управления, то условие х,х,=0 не выполняется. В этом случае каждому входу х, шифратора назначают свой приоритет. Обычно считают, что чем выше номер входа, тем выше его приоритет. В этом случае шифратор должен выдавать на выходе двоичный код числа ;', если х,=1, а на все входы х,, имеющие больший приоритет, поданы нули. Такие шифраторы называются приоритетными, например, если на входе шифратора установлен код 0011, то на выходе будет код 01. В качестве примера рассмотрим функционирование приоритетного шифратора К555ИВ1. Функцонирование этого шифратора описывается табл. 15.2. Условное схематическое изрбражение шифратора К555ИВ1 приведено на рис. 15.4 а. Назначение сигналов на входе шифратора: Е — сигнал включения шифратора (0 — выключен, 1 — включен). Сигналы на выходе: G — сигнал, свидетельствующий о наличии хотя бы одного возбужденного входа х, при включенном состоянии шифратора (7=1 при х<=1, хотя бы для одного г при £=1); ЕО— сигнал разрешения, свидетельствующий об отсутствии возбужденных входов Xi при включенном состоянии шифратора (Е0=1 при Е=1 и х,=0 для всех i). Таким образом, трехразрядный двоичный код можно считывать с выхода шифратора только при условии, что (7=1. Выходной сигнал ЕО можно использовать при каскадном включении шифраторов. Схема расширенного шифратора на ИМС Таблица 15.1 Состояния выходов шифратора 8х3

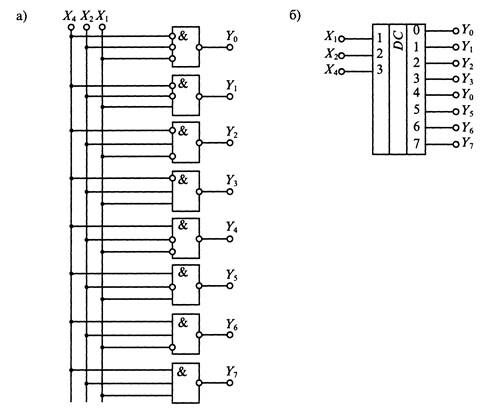

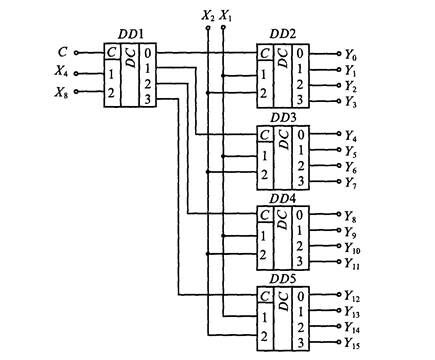

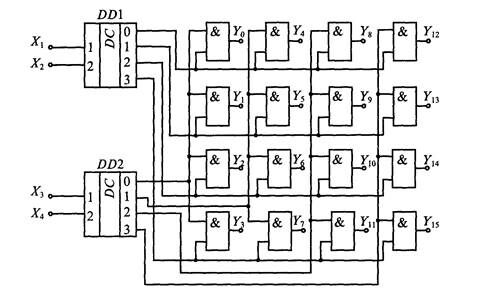

Таблица 15 2 Состояние входов и выходов приоритетного шифратора К555ИВ1 К555ИВ1 форматом 16х4 приведена на рис. 15.46. В этой схеме наивысший приоритет имеет вход Х15. Первый шифратор (верхний по схеме) включается только в том случае, если не возбужден ни один вход второго (нижнего) шифратора. Сигнал G=1, если возбужден хотя бы один вход Хц...Хц. Аналогично функционирует приоритетный шифратор К555ИВ2, отличительной особенностью которого является наличие выходов с тремя состояниями, что  Рис. 15.4. Условное схематичное изображение шифратора К555ИВ1 (а) и расширенный шифратор форматом 16х4 (б) облегчает каскадирование шифраторов. Другой приоритетный шифратор К555ИВЗ имеет формат 10х4 и функционирует аналогично предыдущему. Дешифратором называют преобразователь двоичного я-разрядного кода в унитарный 2"-разрядный код, все разряды которого, за исключением одного, равны нулю. Дешифраторы бывают полные и неполные. Для полного дешифратора выполняется условие: где п — число входов, а N — число выходов. В неполных дешифраторах имеется п входов, но реализуется N<2" выходов. Так, например, дешифратор, имеющий 4 входа и 10 выходов будет неполным, а дешифратор, имеющий 2 входа и 4 выхода, будет полным. Рассмотрим принцип построении дешифратора на примере преобразования трехразрядного двоичного кода в унитарный код. Если считать, что входы и выходы упорядочены по возрастающим номерам, т. е. считать, что коду 000 соответствует выход Ко, коду 001 — выход у) и т. д., то для полного дешифратора можно записать восемь упорядоченных уравнений:  Реализовать восемь уравнений (15.3) можно с помощью восьми трехвходовых элементов И. Полученная схема дешифратора приведена на рис. 15.5 а, а его условное схематичное изображение приведено на рис. 15.5 б. Для расширения числа входов и выходов используют каскадное включение дешифраторов. На рис. 15.6 показана группа из пяти дешифраторов, соединенних последовательно в два каскада. Все дешифраторы одинаковые. Кроме кодовых входов каждый дешифратор имеет вход стробирующего сигнала (вход С). Сигнал на выходе дешифратора появляется только при С=1. Если С=0, то на всех выходах дешифратора будут нули, т. е. дешифратор заперт. На входы первого дешифратора DD подаются старшие разряды Хц и Xs. числа, которое нужно дешифрировать. Таким образом, дешифратор DDI определяет, какой из четырех дешифраторов DD2... DD5 из подключенных к нему будет выполнять дешифрирование младших разрядов числа. Выходные сигналы первого дешифратора подключены к стробирующим входам С остальных и разрешают их работу. Младшие разряды дешифрируемого числа X, и Х-г подаются на входы дешифраторов DD2... DD5. Однако выполнять дешифрирование этих разрядов будет только тот дешифратор, который включен сигналом, поданным на вход С от дешифратора старших разрядов.  Рис. 15.5. Схема дешифратора 3х8 (а) и его условное схематичное изображение (б) Так, например, при дешифрировании числа 1001 на вход поступает код 10, которым возбуждается выход 2. В этом случае включается дешифратор DD4 , на вход которого подан код 01 младших разрядов дешифрируемого числа. В результате будет возбужден выход 1 дешифратора Z)D4, при этом на выходе появится сигнал У9, что соответствует выбранному входному коду. Для расширения числа входов и выходов дешифраторов можно также воспользоваться параллельным или прямоугольным дешифратором, схема которого приведена на рис. 15.7. Схема прямоугольного дешифратора состоит из двух ступеней. Первая ступень состоит из двух дешифраторов DD и DD2, первый из которых дешифрует младшие разряды Х и Х^ входного числа, а второй — старшие разряды Х^ и Х^ Вторая ступень состоит из N элементов 2И-НЕ. Все элементы 2И-НЕ разделены на строки и столбцы: строками управляет дешифратор первой ступени на DD, а столбцами управляет дешифратор DD2, Схема, приведенная на рис. 15.7, соответствует полному дешифратору. Если исключить некоторые из элементов 2И-НЕ, то получим неполный дешифратор с уменьшенным числом выходов.  Рис 156 Каскадное включение дешифраторов  Рис 157 Схема прямоугольного дешифратора Интегральные микросхемы преобразователей кодов, шифраторов и дешифраторов. Промышленность выпускает большое количество различных микросхем преобразователей кодов, шифраторов и дешифраторов, некоторые из которых приведены в табл. 15.3. Таблица 15.3 Интегральные микросхемы преобразователей кодов, шифраторов и дешифраторов

На базе микросхем, приведенных в табл. 15.3, возможно проектирование преобразователей кодов, шифраторов и дешифраторов различной степени сложности. Кроме приведенных специализированных микросхем иногда используют программируемые запоминающие устройства, которые применяют для вывода различных символов на экран монитора при управлении от двоичного кода. К таким элементам относятся микросхемы ПЗУ типа К155РЕ21...К155РЕ24, которые используются в качестве преобразователей двоичного кода в код русского, латинского алфавита, код арифметических и дополнительных символов. |