0_МПиИСТС_Все главы. Микропроцессоры и интерфейсные средства транспортных средств

Скачать 10.01 Mb. Скачать 10.01 Mb.

|

1.12 Контрольные вопросы и задания1. Приведите определение микропроцессора. 2. Что понимается под микропроцессорным комплектом? 3. Из каких блоков состоит микропроцессорная система? 4. В чем состоят различия между принстонской и гарвардской архитектурами? 5. Охарактеризуйте понятия линии, шины и магистрали. 6. Как работает мультиплексированная шина? 7. В чем особенности CISC, RISC и VLIW архитектур? 8. Чем отличается структура МП от архитектуры МП? 9. Дайте определение синхронных и асинхронных магистралей. 10. В чем состоит специфика шин адреса, данных и управления? 11. Как работает конвейер в МП? 12. Что такое суперскалярная структура МП? Глава 2 Режимы работы МПСВыделяют следующие основные режимы работы МПС: 1) Обмен данными под управлением МП. 2) ПДП (прямой доступ к памяти), другие названия этого же режима – DMA, «захват магистрали». 3) Режим прерывания. 2.1 Режим обмена данными под управлением процессораЭтот режим включает следующие подрежимы:

Первые четыре режима применяются только для МП, у которых разделены адресные пространства памяти и внешних устройств. Если же такого деления нет, то 4 режима переходят в 2 режима: чтение и запись данных. Пятый подрежим встречается только в мультиплексированных магистралях. Если данные считываются из той же ячейки куда возвращаются, то нет необходимости повторно выставлять данные и это повышает производительность процессора. При выполнении цикла записи (рис. 2.2) микропроцессор вначале выставляет адрес, затем – данные и после этого активирует сигнал записи (ЗП). После определенной выдержки времени вначале снимается сигнал ЗП, затем снимаются данные, адрес может не сниматься до начала очередного цикла обмена.

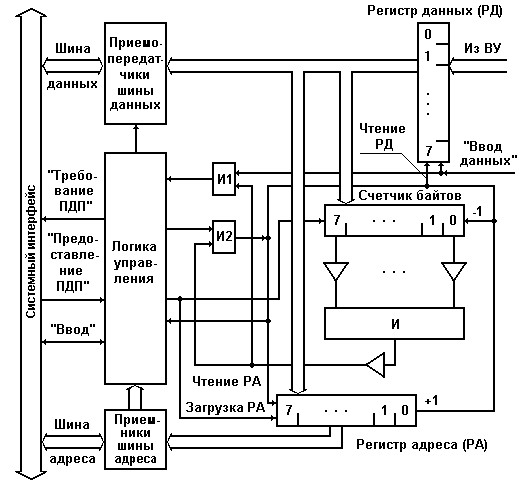

Алгоритм работы в цикле чтения следующий: - МП выставляет адрес; - затем через время переходного процесса – сигнал ЧТ (чтение); - в ответ память или ВУ выставляет данные; - МП снимает сигнал чтения; - память или ВУ снимают данные. 2.2 Режим ПДПИспользуется при обмене большими массивами данных. Осуществляется обмен между памятью и устройством прямого доступа. Устройство должно не только иметь возможность запросить переход в режим прямого доступа и обеспечить выход из режима, но и также должно формировать адрес, сигналы управления обменом и воспринимать сигналы обратной связи. Устройство прямого доступа по своей инициативе (или нескольких устройств одновременно) выставляет сигнал запроса прямого доступа. Процессор, обнаружив сигнал запроса, безусловно завершает текущий цикл обмена по магистрали, причем команда может быть не завершена и содержимое регистра общего назначения нигде не сохранится, после чего формируется сигнал разрешения прямого доступа. Этот сигнал соответствует существующей структуре приоритетов, поступает на вход наиболее приоритетного из устройств. Одним из способов обмена данными с ВУ является обмен в режиме прямого доступа к памяти (ПДП). В этом режиме обмен данными между ВУ и основной памятью микроЭВМ происходит без участия процессора. Обменом в режиме ПДП управляет не программа, выполняемая процессором, а электронные схемы, внешние по отношению к процессору. Обычно схемы, управляющие обменом в режиме ПДП, размещаются или в специальном контроллере, который называется контроллером прямого доступа к памяти, или в контроллере самого ВУ. Обмен данными в режиме ПДП позволяет использовать в микроЭВМ быстродействующие внешние запоминающие устройства, такие, например, как накопители на жестких магнитных дисках, поскольку ПДП может обеспечить время обмена одним байтом данных между памятью и ВЗУ, равное циклу обращения к памяти. Для реализации режима прямого доступа к памяти необходимо обеспечить непосредственную связь контроллера ПДП и памяти микропроцессора. Для этой цели можно было бы использовать специально выделенные шины адреса и данных, связывающие контроллер ПДП с основной памятью. Но такое решение нельзя признать оптимальным, так как это приведет к значительному усложнению микропроцессора в целом, особенно при подключении нескольких ВЗУ. В целях сокращения количества линий в шинах микропроцессора контроллер ПДП подключается к памяти посредством шин адреса и данных системного интерфейса. При этом возникает проблема совместного использования шин системного интерфейса процессором и контроллером ПДП. Можно выделить два основных способа ее решения: реализация обмена в режиме ПДП с «захватом цикла» и в режиме ПДП с блокировкой процессора. Существуют две разновидности прямого доступа к памяти с «захватом цикла». Наиболее простой способ организации ПДП состоит в том, что для обмена используются те машинные циклы процессора, в которых он не обменивается данными с памятью. В такие циклы контроллер ПДП может обмениваться данными с памятью, не мешая работе процессора. Однако возникает необходимость выделения таких циклов, чтобы не произошло временного перекрытия обмена ПДП с операциями обмена, инициируемыми процессором. В некоторых процессорах формируется специальный управляющий сигнал, указывающий циклы, в которых процессор не обращается к системному интерфейсу. При использовании других процессоров для выделения таких циклов необходимо применение в контроллерах ПДП специальных селектирующих схем, что усложняет их конструкцию. Применение рассмотренного способа организации ПДП не снижает производительности микроЭВМ, но при этом обмен в режиме ПДП возможен только в случайные моменты времени одиночными байтами или словами. Более распространенным является ПДП с «захватом цикла» и принудительным отключением процессора от шин системного интерфейса. Для реализации такого режима ПДП системный интерфейс микропроцессора дополняется двумя линиями для передачи управляющих сигналов «Требование прямого доступа к памяти» (ТПДП) и «Предоставление прямого доступа к памяти» (ППДП). Управляющий сигнал ТПДП формируется контроллером прямого доступа к памяти. Процессор, получив этот сигнал, приостанавливает выполнение очередной команды, не дожидаясь ее завершения, выдает на системный интерфейс управляющий сигнал ППДП и отключается от шин системного интерфейса. С этого момента все шины системного интерфейса управляются контроллером ПДП. Контроллер ПДП, используя шины системного интерфейса, осуществляет обмен одним байтом или словом данных с памятью микропроцессора и затем, сняв сигнал ТПДП, возвращает управление системным интерфейсом процессору. Как только контроллер ПДП будет готов к обмену следующим байтом, он вновь «захватывает» цикл процессора и т.д. В промежутках между сигналами ТПДП процессор продолжает выполнять команды программы. Тем самым выполнение программы замедляется, но в меньшей степени, чем при обмене в режиме прерываний. Применение в микропроцессоре обмена данными с ВУ в режиме ПДП всегда требует предварительной подготовки, а именно: для каждого ВУ необходимо выделить область памяти, используемую при обмене, и указать ее размер, т.е. количество записываемых в память или читаемых из памяти байт (слов) информации. Следовательно, контроллер ПДП должен обязательно иметь в своем составе регистр адреса и счетчик байт (слов). Перед началом обмена с ВУ в режиме ПДП процессор должен выполнить программу загрузки. Эта программа обеспечивает запись в указанные регистры контроллера ПДП начального адреса выделенной ВУ памяти и ее размера в байтах или словах в зависимости от того, какими порциями информации ведется обмен. Сказанное не относится к начальной загрузке программ в память в режиме ПДП. В этом случае содержимое регистра адреса и счетчика байт слов устанавливается переключателями или перемычками непосредственно на плате контроллера. Блок-схема простого контроллера ПДП, обеспечивающего ввод данных в память микропроцессора по инициативе ВУ в режиме ПДП «Захват цикла», приведена на рис. 2.4.

Перед началом очередного сеанса ввода данных из ВУ процессор загружает в регистры его контроллера следующую информацию: в счетчик байт - количество принимаемых байт данных, а в регистр адреса - начальный адрес области памяти для вводимых данных. Тем самым контроллер подготавливается к выполнению операции ввода данных из ВУ в память микропроцессора в режиме ПДП. Байты данных из ВУ поступают в регистр данных контроллера в постоянном темпе. При этом каждый байт сопровождается управляющим сигналом из ВУ «Ввод данных», который обеспечивает запись байта данных в регистр данных контроллера. По этому же сигналу и при ненулевом состоянии счетчика байт контроллер формирует сигнал ТПДП. По ответному сигналу процессора ППДП контроллер выставляет на шины адреса и данных системного интерфейса содержимое своих регистров адреса и данных соответственно. Формируя управляющий сигнал «Вывод», контроллер ПДП обеспечивает запись байта данных из своего регистра данных в память микропроцессора. Сигнал ППДП используется в контроллере и для модификации счетчика байт и регистра адреса. По каждому сигналу ППДП из содержимого счетчика байт вычитается единица, и как только содержимое счетчика станет равно нулю, контроллер прекратит формирование сигналов «Требование прямого доступа к памяти». На примере простого контроллера ПДП мы рассмотрели только процесс подготовки контроллера и непосредственно передачу данных в режиме ПДП. На практике любой сеанс обмена данными с ВУ в режиме ПДП всегда инициируется программой, выполняемой процессором, и включает два следующих этапа. 1. На этапе подготовки ВУ к очередному сеансу обмена процессор в режиме программно-управляемого обмена опрашивает состояние ВУ (проверяет его готовность к обмену) и посылает в ВУ команды, обеспечивающие подготовку ВУ к обмену. Такая подготовка может сводиться, например, к перемещению головок на требуемую дорожку в накопителе на жестком диске. Затем выполняется загрузка регистров контроллера ПДП. На этом подготовка к обмену в режиме ПДП завершается и процессор переключается на выполнение другой программы. 2. Обмен данными в режиме ПДП начинается после завершения подготовительных операций в ВУ по инициативе либо ВУ, как это было рассмотрено выше, либо процессора. В этом случае контроллер ПДП необходимо дополнить регистром состояния и управления, содержимое которого будет определять режим работы контроллера ПДП. Один из разрядов этого регистра будет инициировать обмен данными с ВУ. Загрузка информации в регистр состояния и управления контроллера ПДП производится программным путем. Наиболее распространенным является обмен в режиме прямого доступ к памяти с блокировкой процессора. Он отличается от ПДП с «захватом цикла» тем, что управление системным интерфейсом передается контроллеру ПДП не на время обмена одним байтом, а на время обмена блоком данных. Такой режим ПДП используется в тех случаях, когда время обмена одним байтом с ВУ сопоставимо с циклом системной шины. В микропроцессоре можно использовать несколько ВУ, работающих в режиме ПДП. Предоставление таким ВУ шин системного интерфейса для обмена данными производится на приоритетной основе. Приоритеты ВУ реализуются так же, как и при обмене данными в режиме прерывания, но вместо управляющих сигналов «Требование прерывания» и «Предоставление прерывания» используются сигналы «Требование прямого доступа» и «Предоставление прямого доступа» соответственно. Структура приоритетов устройств прямого доступа к памяти: - радиальная (рис. 2.5); - цепочечная (рис. 2.6); - смешанная (рис. 2.7).

Если устройство ПДП активировало сигнал запроса, то, получив сигнал разрешения, оно снимает сигнал запроса, блокирует распространение сигнала разрешения и выставляет сигнал подтверждения выбора. УПДП начинает осуществлять требуемый обмен. По завершению обмена УПДП снимает сигнал подтверждения выбора и процессор, обнаружив эту ситуацию, вновь анализирует состояния выбора запросов. |