5fan_ru_Проектирование простейших цифровых электронных схем (1).. Министерство образования республики беларусь белорусский государственный университет информатики и радиоэлектроники

Скачать 390.5 Kb. Скачать 390.5 Kb.

|

|

МИНИСТЕРСТВО ОБРАЗОВАНИЯ РЕСПУБЛИКИ БЕЛАРУСЬ БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИ Факультет компьютерных технологий и систем Кафедра ЭВМ ПАНАРАД СЕРГЕЙ ВЛАДИМИРОВИЧ ВМИС Проектирование простейших цифровых электронных схем Отчёт по лабораторной работе №2 (вариант 17) студента 3 курса 221902 группы

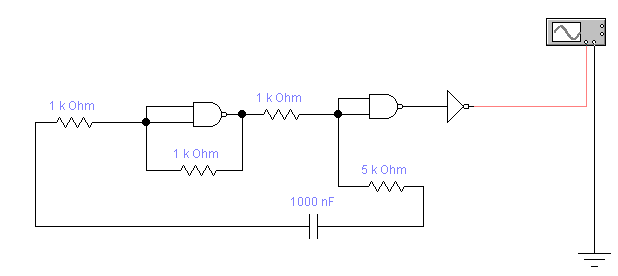

Минск 2014 Задание 1 Моделирование автогенератора на логических элементах Выберем из таблицы 1 схему генератора согласно варианту задания. Таблица 1

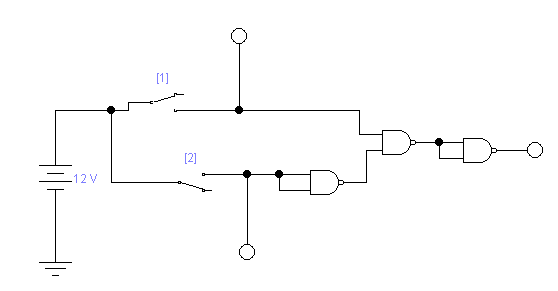

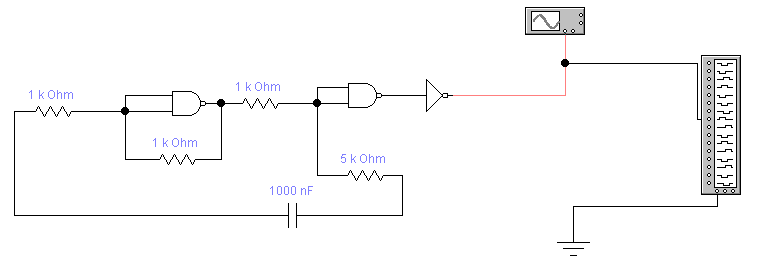

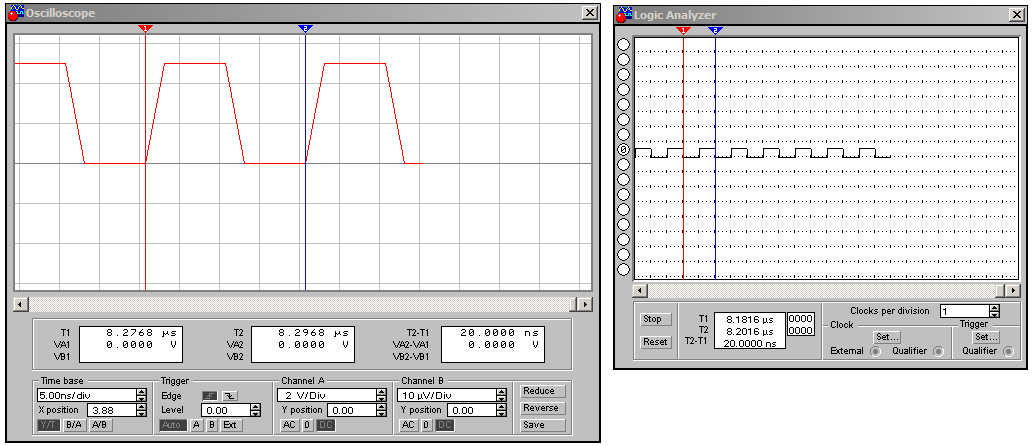

Рис.1. Исследуемая схема. Развёрнутые осциллограммы представлены на рисунках 2 (а, б):

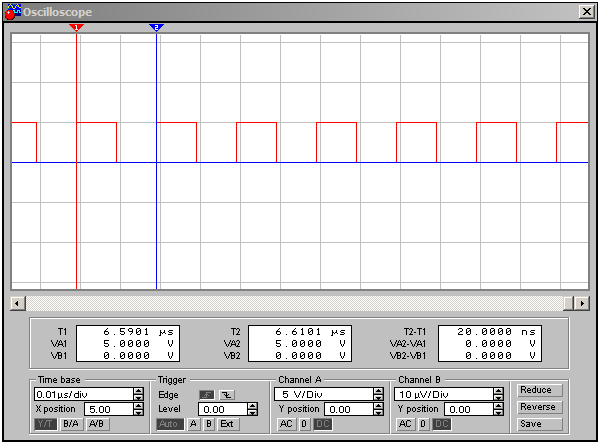

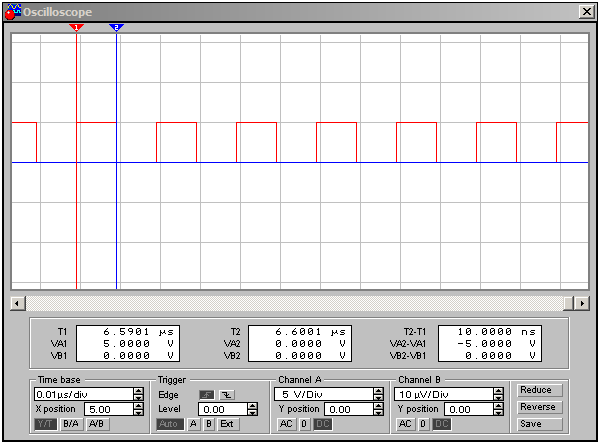

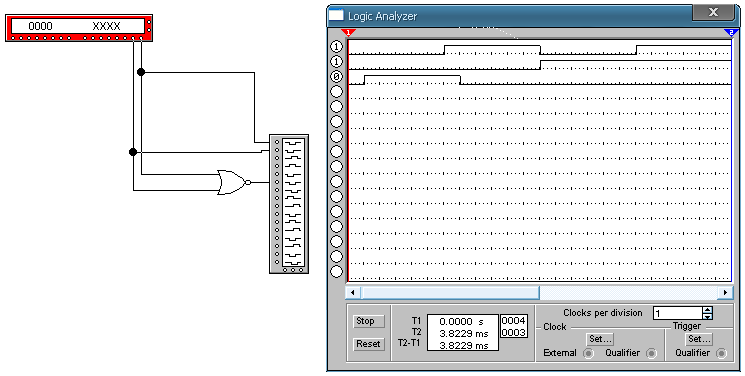

Рис.2. Осциллограмма сигнала а) с выделенным периодом, б) с выделенной длительностью импульса. Из рисунков 2 (а) и 2 (б) видно, что амплитуда Зная период найдем частоту сигнала: Определим скважность по формуле  где Не прямые фронты импульса объясняются тем, что изображение сигнала получено через осциллограф, а не через логический анализатор. И, как известно, любой логический элемент и конденсатор является инертным, то есть не может изменить своё значение мгновенно. Любой сигнал имеет фронты, которые осциллограф может различить и показать. За начало импульса стоит принимать значение времени, когда напряжение начинает возрастать, за конец импульса – когда начинает спадать. Постоянное периодическое появление импульсов связано с тем, что в логических элементах периодически возникают 0 или 1, которые идут на входы друг друга и образуют на выходах других 1 или 0. Процесс циклически повторяется, из-за чего получается автогенерация импульсов. Подключим логический анализатор   Рис.3. Осциллограмма сигнала с подключённым логическим анализатором. Из рисунка 3 видно, что амплитуда Зная период найдём частоту сигнала: Определим скважность по формуле:  где Задание 2 Проектирование простейших логических схем Протестируем функцию Таблица истинности для этой функции представлена в таблице 2 Таблица 2

Составление логических схем с использованием двухвходового элемента Шеффера. Элемент Шеффера представляет собой полный базис и выполняет функцию И-НЕ. Схемы функции

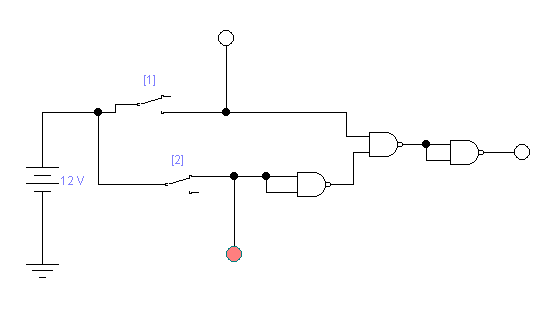

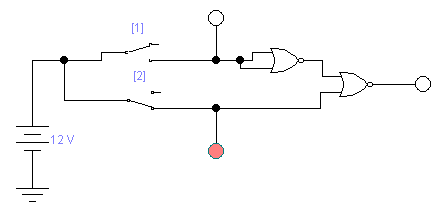

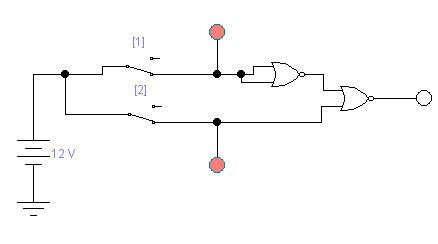

Рис.4. Схемы, реализующие функцию Лампочки показывают значения сигналов на данном участке цепи в данный момент времени. Не горящей лампочке соответствует логический 0, горящей – логическая 1. По полученным результатам видим, что требуемая функция выполняется. Составление логических схем с использованием двухвходового элемента Вебба. Элемент Вебба представляет собой полный базис и выполняет функцию ИЛИ-НЕ. Схемы функции

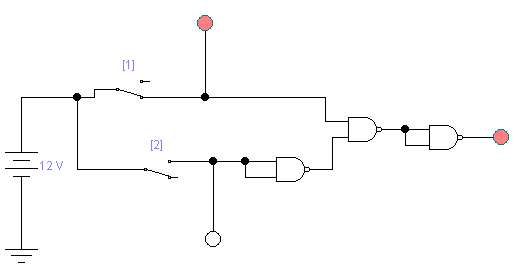

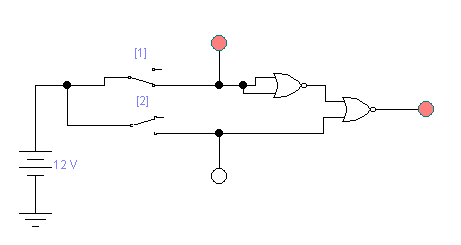

Рис.5. Схемы, реализующие функцию Лампочки показывают значения сигналов на данном участке цепи в данный момент времени. Не горящей лампочке соответствует логический 0, горящей – логическая 1. По полученным результатам видим, что требуемая функция выполняется. Протестируем функцию Таблица истинности для этой функции представлена в таблице 3 Таблица 3

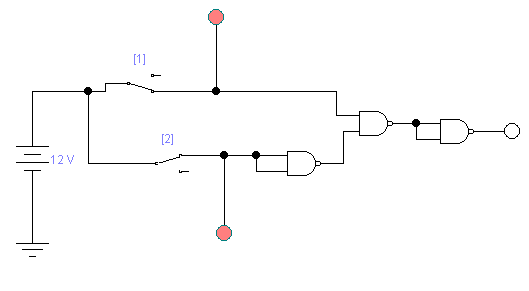

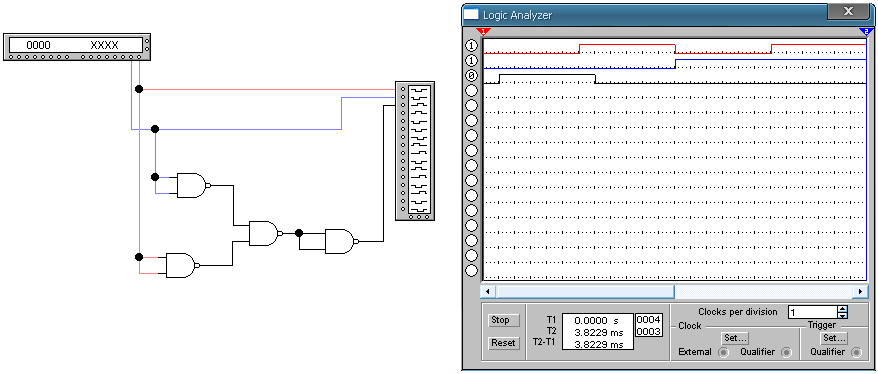

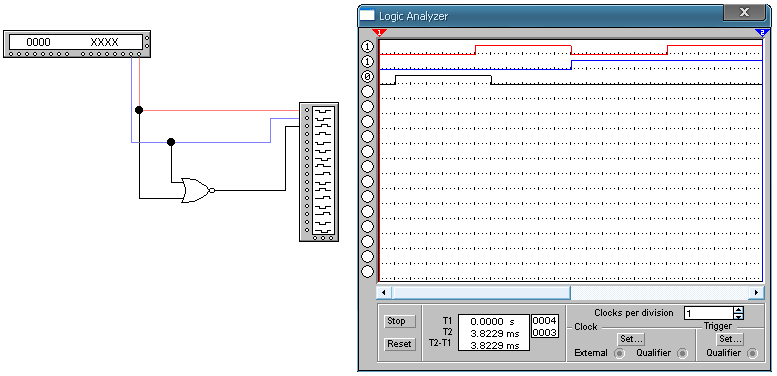

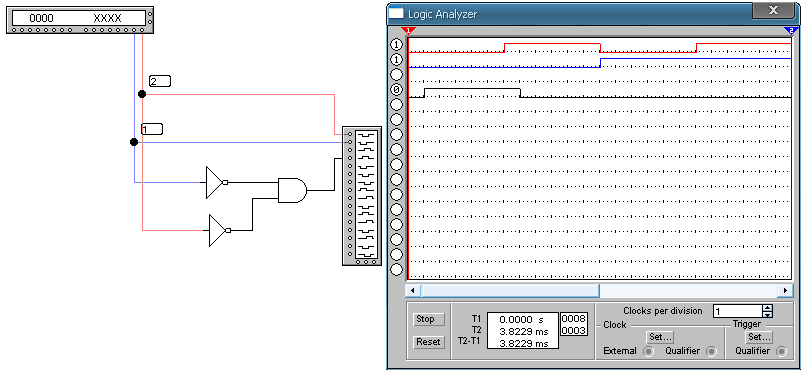

Спроектируем схему в базисе И-НЕ: Схема функции  Рис.6. Схема, реализующая функцию Из результатов, показываемых логическим анализатором видно, что схема выполняет требуемую функцию. Также заметна задержка сигнала на выходе. При изменении входной переменной значение выходной функции изменяется не сразу, а через какой-то промежуток времени, это связано с тем, что элементы схемы не могу моментально изменить свои значения, а имеют какой-то время срабатывания. Спроектируем схему в базисе ИЛИ-НЕ: Схема функции  Рис.7. Схема, реализующая функцию Из результатов, показываемых логическим анализатором видно, что схема выполняет требуемую функцию. Также из результатов видно, что изменение выходного сигнала отстает от входного. Это связано с тем, что элементы схемы не могут моментально изменить свои состояния, а обладают некоторым временем срабатывания, из-за чего появляется задержка на выходе схемы. Протестируем функцию Таблица истинности для этой функции представлена в таблице 3 Таблица 4

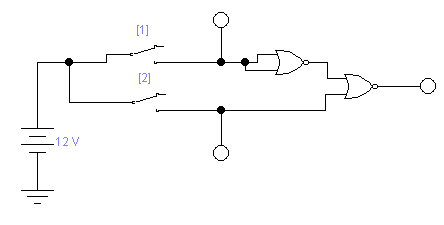

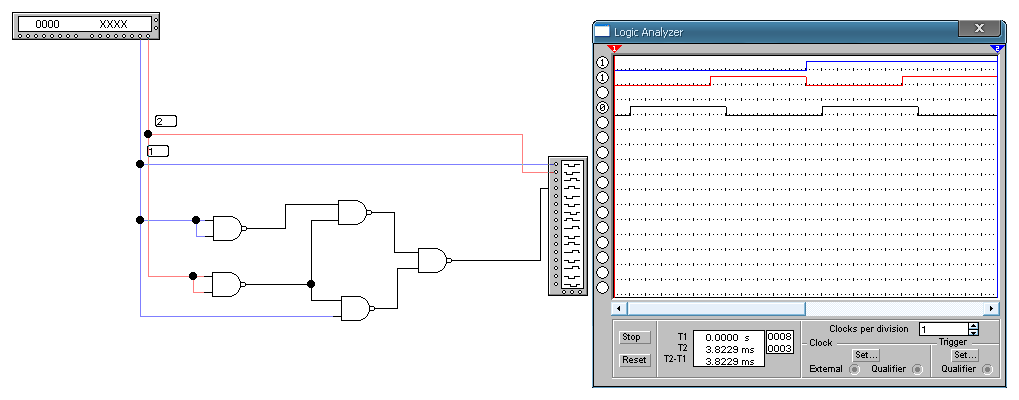

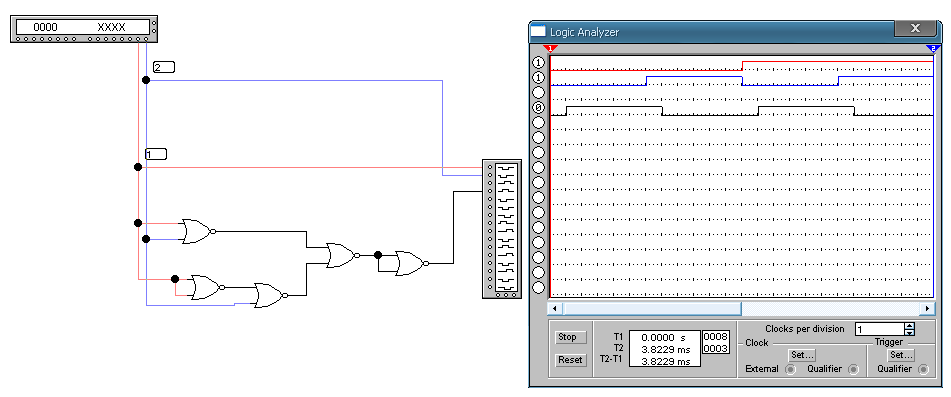

Спроектируем схему в базисе И-НЕ: Схемы функции  Рис.8. Схема, реализующая функцию Из результатов, показываемых логическим анализатором видно, что схема выполняет требуемую функцию. Причина задержки выходного сигнала описана выше. Спроектируем схему в базисе ИЛИ-НЕ: Схема функции  Рис.9. Схемы, реализующие функцию 3.1. Доказательство основных тождеств булевой алгебры Согласно варианту необходимо доказать следующее тождество: Соберём логическую схему для доказательства тождества. Собранная схема с показаниями логического анализатора представлены на рисунке 10.   Рис.10. Схемы для доказательства тождества. Из показаний логического анализатора видно, что тождество справедливо и выполняется схемой. При любом значении х на выходе схемы получаем единицу. Задержка выходного сигнала в самом начале обусловлена временем срабатывания логических элементов. Исследование проводилось в динамическом режиме. Вывод: исследовали работу автогенератора. Составили схемы, выполняющие простые логические функции в базисах И-НЕ и ИЛИ-НЕ. Провели исследования в статическом и динамическом режимах. Доказали одно из тождеств булевой алгебры с помощью логической схемы. |