схематехника. Схемотехника

Скачать 0.84 Mb. Скачать 0.84 Mb.

|

|

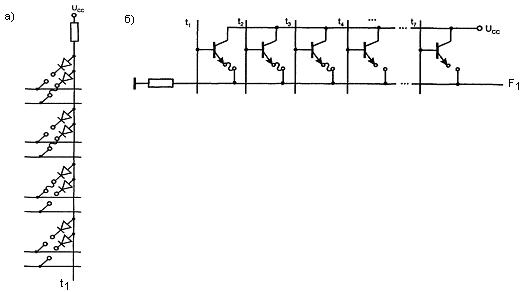

8.3 Кез-келген модульді екілік-кодталған есептегіштер 2 санының бүтін дәрежесіне тең емес, яғни кез-келген модульді есептегіш бірнеше әдістер негізінде іске асырылады. Осындай екілік есептегіштің 2n - М = L шығарып тастауға жататын артық жағдайлары бар. Артық жағдайларды шығарып тастау әдістері сан алуан және кез-келген М үшін есептегіштің көптеген мүмкіндіктерін қарастыруға болады. Бірінші күйлердің небір санын шығару арқылы есептегіштің алғашқы нөлдік күйін аламыз, бұл есептің табиғи ретінің жоқтығына және есептегіште артық кодты тіркеуге әкеліп соғады. Соңғы күйлерді шығарып тастау есептеудің табиғи ретін сақтауға мүмкіндік береді. Кез-келген модульді есептегіштерді құрудың 2 тәсілін қарастыралық: разрядаралық модификациялы байланыстар және ауытқуды басқару. Модификациялық разрядаралық байланысты есептегіштерді құрастыру кезінде, соңғы, артық күйлер есептегіштің жұмыс істеу кестелерінен тікелей шығарылып тасталады. Осы кезде сызбаны құрғаннан кейін автоматтар синтезі үшін кәдімгі әдіспен есептегіш алынады, оның спецификасы стандартты емес функцияларда триггерлердің қозуы және сәйкесінше, триггерлердің арасындағы стандартты емес байланыста болып отыр. Осы оның атауын да түсіндіреді. 8.3.1 Есептегіштерді құрудың бірінші тәсілі. Бірінші әдіс бойынша есептегіштерді құруды М = 5 арналған мысалмен көрсетейік, 8.1 кестеден басталық. 8.1 кесте

Триггерлердің қозу функцияларын табуда 8.2 кестенің «сөздігі» қолданылған. 8.2 кесте

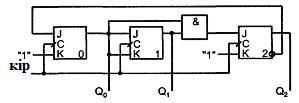

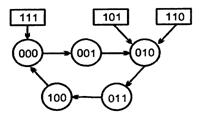

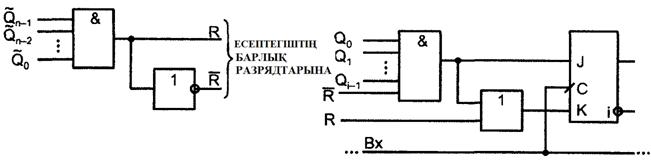

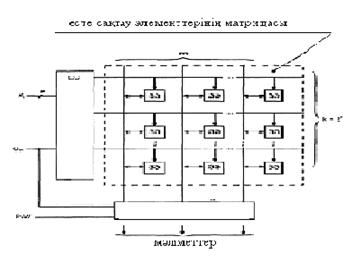

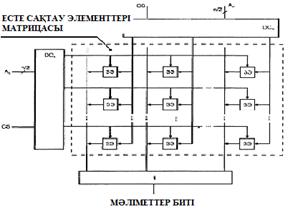

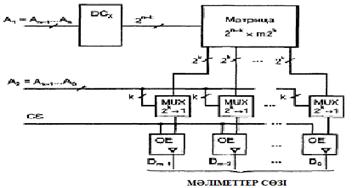

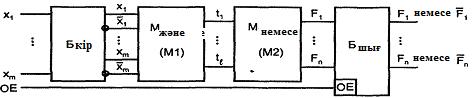

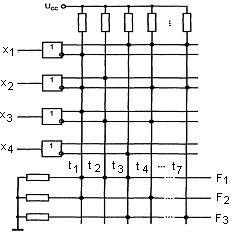

Ерікті Х сигналының символының орнына кез-келген айнымалыны (0 немесе 1) қоюға болады. 8.1 кестенің негізінде жазалық: Есептегіш сызбасы 8.6-суретте келтірілген. Есептегіштің жобаланған жүйесінде артық күйлер олар есептегіштің қалыпты жұмысында пайдаланылмайтындықтан алынып тасталған. Бірақ бұзылуларда немесе сызбаға қоректену кернеуінің берілуінен кейін оның жұмысының басында артық күйлер орын алуы мүмкін.  8.6 сурет – Модулі 5 болатын есептегіш сызбасы Әрбір артық күйді алып, олардың келесі күйлерге өтуін анықтайтын триггерлердің қозу күйін анықтаймыз. Қажет болған жағдайда дәл осы әдіспен келесі ауысымды да және т.б анықтаймыз. Алынған мысал үшін артық болып 101, 110 және 111 күйлері табылады. 101 жағдайында Q2 = 1, Q1 = 0 және Q0 = 1. Триггерлердің қозу фунциясын біле отырып, J0 = 0, К0 = 1, J1 = K1 = 1, J2 = 0, К2 = 1 екендігін анықтаймыз. Демек, 0 және 2 триггерлері лақтырылады, ал триггер 1 ағымдағы күйге қарама-қарсыға қайта қосылады және 101 артық күйінен есептегіш 010 күйіне өтеді. Ұқсас әдіспен 100 және 111 күйлеріне нәтижелер алуға болады. Нәтижесінде есептегіштің күй диаграммасын тұрғызуға болады (ауысымдар графигі), мұнда тек жұмыс циклі (күйлер - айналмалар) ғана емес, қолданылмайтын күйге түскен (тікбұрыштар) автоматтар мінезі есепке алынған. Мұндай диаграмма 8.7 суретте көрсетілген.  8.7 сурет – Модулі 5 болатын есептегіштің күй диаграммасы Диаграммадан қарастырылған есептегіштің өздігінен қосылу қасиеті бар екендігін көре аламыз – бастапқы жағдайына тәуелсіз ол жұмыс цикліне жұмыс басталғаннан кейін келеді. 8.3.2 Есептегішті құрудың екінші тәсілі. Кез-келген модульді есептегішті құрудың екінші әдісі – лақтыруды басқару әдісі - есеп модулін есептегіштің сызбасын өзгертуді қажет етпейтін өте қарапайым әдіспен модуль есебін өзгертуге мүмкіндік береді. Параллельді ауыстыруы бар синхронды есептегішті енгізуде қолдануға байланысты әдісті қарастырайық (8.3 суретті қара). Аталған типті екілік есептегіштің қозу функциясы, біз білетіндей, мына түрге Jj = Kj = Q0Q1…Qi-1 (J0 = K0 = 1 кіші триггерде) келтірілген. Бұл функцияларға оларды келесідей өзгертіп, лақтыру сигналы R енгізейік: Кi = Ji v R.  8.8 сурет – Лақтыруды басқаруы бар есептегіштің сызбасы Сигнал болмағанға дейін (R = 0), Jj и Kj функцияларының сәйкес екілік есептегіш функцияларынан айырмашылығы болмайды. R сигналы бірлік мәніне ие болғанда, Ji барлық функциялары нольдік, Kj – бірлік болады, бұл барлық келесі такті келгенде лақтырылуына мәжбүрлейді. Егер R есептегіште М-1 санының пайда болуы салдарынан орын алса, онда есептің 0, 1, 2,..., М-1, 0... кезегі, яғни М модульді есептегіш жүзеге асырылады. Лақтыруды басқаруы бар есептегіштердің барлық разрядтарының сызбасы есеп модуліне тәуелді болмайды. Разрядты сызбалардан басқа, М-1 есептегіш мәніне жеткенде лақтыру сигналын қамтамасыз ететін бір коньюктор болады (8.8 суретті қара). 9 Дәріс. Есте сақтау құрылғылары 9.1 Есте сақтау құрылғыларының классификациясы Есте сақтау құрылғыларын классификациялаудың маңызды белгісі мәліметтерге рұқсат алу әдісі болып табылады. Мекен-жайлық рұқсат кезінде мекен-жайлық кірістегі код алмасу жүретін торшаны көрсетеді. Мекен-жайлық жадының барлық ұяшықтарына айналу мезетінде бірдей қол жетерлік болады. Мекен-жайлық есте сақтау құрылғылары RAM (Random Access Memory) және ROM (Read-Only Memory) болып бөлінеді. Терминдердің орысша аударылған синонимдері RAM: ОЕСҚ (оперативті есте сақтау құрылғылары) немесе ЕТБЕСҚ (ерікті таңдауы бар есте сақтау құрылғылары). Оперативті есте сақтау құрылғылары ерікті уақыт мезетінде өзгертіле алатын, ағымдағы бағдарламаны жүзеге асыру кезінде ауыстыруға қатысатын мәліметтерді сақтайды. Оперативті есте сақтау құрылғыларының есте сақтау элементтері энергиялық тәуелсіздікке ие емес. ROM (аударғандағы эквиваленті – ТЕСҚ, яғни тұрақты есте сақтау құрылғылары) құрылғысында мазмұны мүлдем өзгермейді, немесе өзгерсе де, бірақ өте сирек және арнайы режимде болады. Жұмыс режимі үшін бұл «оқуға ғана арналған жады». RAM статикалық және динамикалық болып бөлінеді. Бірінші нұсқа бойынша есте сақтау элементі болып триггерлер табылады, олар өз қалпын сызба қорек алып тұрғанда және жаңа жазбалар болмаған жағдайда сақтап тұрады. Екінші нұсқада мәліметтер МОП-құрылымды элементтерден түзілетін конденсатор зарядтарының түрінде сақталады. Конденсаторлардың өздігінен разрядталуы мәліметтердің жойылуына әкеліп соғады, сондықтан олар периодты түрде (әрбір бірнеше миллисекунд сайын) регенерациялануы тиіс. Динамикалық есте сақтау құрылғыларында мәліметтердің регенерациялануы (қалпына келуі) арнайы контроллердің көмегімен жүзеге асырылады. Статикалық есте сақтау құрылғылары – SRAM (Static RAM), ал динамикалық – DRAM (Dynamic RAM) деп аталады. Динамикалық есте сақтау құрылғылары көбірек ақпараттық сыйымдылықпен және бағасының жоғары болмауымен сипатталады, осы себепті оларды ЭЕМ негізгі жады ретінде пайдаланады. Flash типіндегі жады есте сақтау элементі бойынша EEPROM (немесе басқаша E2PROM) типіндегі жадыға ұқсас, бірақ өзін бөлек түрге бөлуге мүмкіндік беретін құрылымдық және технологиялық ерекшеліктері бар. Тізбекті ену есте сақтау құрылғыларында жазылатын мәліметтер белгілі бір кезекті түзеді. Санау сөзбе сөз жазылу кезегімен немесе кері кезекпен жүзеге асырылады. Бұндай есте сақтау элементтерінің моделі болып мәліметтер көршілес элементтердің арасында алмасатын есте сақтау элементінің кезекті тізбегі болып табылады. Тура санау реті «бірінші келді –бірінші кетті» тәртібімен жүретін FIFO буферлерінде (First In - First Out), сонымен қатар файлды және циклдық есте сақтау құрылғыларында орын алады. FIFO жадысы мен файлды есте сақтау құрылғыларының арасындағы айырмашылық мынада: FIFO жадысындағы бос буферге түскен жазу бірден оқуға ашық болып келеді, яғни тізбектің (есте сақтау құрылғысының моделінің) соңына барып түседі. Файлды есте сақтау құрылғыларында мәліметтер тізбек басына келіп түседі де тізбек элементтерінің санына тең өңдеулерден кейін ғана оқылады. Жазылатын мәліметтерді аяқ жағының және басының арнайы символдарымен белгіленген блоктарға біріктіреді. Файлды есте сақтау құрылғыларынан мәліметтерді қабылдау қабылдауышпен блок басының символы анықталған соң ғана басталады. Циклдық құрылғыларда сөздерге бірінен кейін біріне жадының сыйымдылығымен анықталатын тұрақты периодпен қол жеткізуге болады. Жартылай өткізгішті есте сақтау құрылғыларының ішінде бұндай типке видеожады (VRAM) жатады. Кері ретпен оқу стекті есте сақтау құрылғыларына тиесілі, олар үшін «соңғы келді – бірінші кетті» тәртібі жүзеге асырылады. Бұндай есте сақтау құрылғыларын LIFO (Last In — First Out) буферлері деп атайды. Ассоциативті қол жеткізу ақпаратты өңдеуді кейбір белгілері бойынша жүзеге асырылады, бірақ оның жадыда орын алуы (мекен-жайы немесе кезектегі орны) бойынша емес. Толығырақ версияда жадыда сақталатын барлық сөздер бір уақытта белгіге сәйкес келуі, мысалы, белгілі сөздер өрісінің (ағылшын тілінен tag сөзінен) кіру сөзімен (типтік мекен-жайымен) берілген белгімен сәйкес келуіне тексеріледі. Шығысқа белгіні қанағаттандыратын сөздер жіберіледі. Заманауи ЭЕМ-нда ассоциативті жадыны қолданудың негізгі аясы-мәліметтерді жүктеу. 9.2 Есте сақтау құрылғыларының негізгі құрылымдары Статикалық оперативті есте сақтау құрылғылары және ROM типті жадылар үшін 2D, 3D және 2DM құрылғылары сипатты. 9.2.1 2D құрылымы . 2D құрылымында (9.1 суретті қара) ЕСЭ есте сақтау элементтері М = k x m өлшемді тік бұрышты матрицаға ұйымдастырылады, мұндағы: М – жадының ақпараттық сыйымдылығы, бит; k – сақталу сөздерінің саны; m – олардың разрядтылығы.  9.1 сурет – 2D типті есте сақтау құрылғыларының құрылымы DC адресті кодының ДШ рұқсат беру сигналы CS (Chip Select – микросызбаны таңдау сигналы) бар болған жағдайда таңдалған жолдың барлық элементтеріне бір уақытта қол жеткізуді рұқсат ететін мекен-жайы нөміріне сәйкес келетін сөзді сақтайтын шығу сызықтарының біреуін активтендіреді. Алмасу бағыттары R/W (Read - оқу, Write - жазу) сигналдарының әсеріндегі оқу/жазу күшейткіштерімен анықталады. 2D типіндегі құрылым тек аз сыймдылықты ЕСҚ қолданылады, яғни дешифратордың шығу саны сақталушы сөздер санына тең. 9.2.2 3D құрылымы. 3D құрылымы есте сақтау элементтерінің екі координатты таңдамасына ие (9.2 суретті қара). n разрядты мекен-жай коды екі жартыға бөлінеді, олардың кодтары жеке-жеке шешіледі. Екі дешифратордың шығуларындағы активті сызықтарының қиылысуында орналасқан есте сақтау элементі таңдалады. Бұндай қиысулар болады Екі дешифратордың шығыстар санының қосындысы бұл n нақты мәндеріндегі 2n қарағанда әлдеқайда аз.  9.2 сурет – 3D типіндегі бірзарядты ұйымның есте сақтау құрылғысының құрылымы 9.2.3 2DM құрылымы. 2DM құрылымды ROM типті (9.3 суреттен қара) ЕСҚ бүтін жолды таңдайтын DCx дешифраторларынан мекен-жайы бар есте сақтау элементтерінің матрицасы үшін.  9.3 сурет – ROM арналған 2DM типті есте сақтау құрылғысының құрылымы Алайда 2D құрылымына қарағанда жол ұзындығы сақталушы сөздердің разрядтылығына тең емес, ал оны көптеген есе көбейтеді. Матрицаның жолдарының саны азаяды және сәйкесінше DC шығуларының саны азаяды. Жолдардың біреуін таңдау үшін Т адресті кодтардың барлық разрядтары қызмет етпейді, ал олардың бөлігі An-1... Ak. Басқа разрядты адрестік басқа разрядтары (Ak-1…A0) жолда болатын көп сөздердің ішінен қажетті сөзді таңдау үшін қолданылады. Бұл адресті кірістеріне Ak-1…A0 коды берілетін мультиплексорлар көмегімен жүзеге асырылады. Жол ұзындығы m2k тең, мұндағы, m – сақталушы сөздердің разрядтылығы. Ұзындығы 2k жолдың әрбір «кесігінен» мультиплексор бір бит таңдайды. Мультиплексорлар шығысында шығу сөзі қалыптасады. Үш күймен басқарылатын буферлердің ОЕ кірісіне түсетін CS сигналының рұқсат етілуіне байланысты шығу сөзі сыртқы шинаға беріледі. 10 Дәріс. ПЛМ және ПМЛ Ақпаратты сандық өңдеу жүйелеріне процессор, жады, перифериялық құрылғылар және интерфейстік схемалар кіреді. Жүйеде стандартты бөліктермен қатар, оны өңдеу үшін арнайы жабдықталған кейбір стандартты емес бөліктер де бар. Бұл блоктарды басқару олардың өзара әсерін қамтамасыз ету және тағы басқа схемаларына қатысты болады. Жүйелер үшін интеграция деңгейі жоғары арнайы АҚ тапсырыс беру қиындау, себебі бұл өте үлкен құралдар шығындары мен ҮИҚ/ҮИҚЖ жобалауда көп уақытты қажет етеді. Туындаған қарама-қайшылық бағдарламаланған және қайта бағдарламаланған құрылымды ҮИҚ/ҮИҚЖ құрастыру барысында шешімін тапты. БИС/СБИС құрастыру жолдарында және қайта бағдарламалау құрылымында шешімін тапты. Көрсетілген бағыттағы АҚ ең алғашқы өкілдері болып ПЛМ (PLA, Programmable Logic Array), бағдарламаланатын матрицалық логика ПМЛ (PAL, Programmable Array Logic) және вентильдік матрицалар ВМ (GA, Gate Array) деп аталатын базалық матрицалық кристалдар БМК келеді. PLA және PAL ағылшын терминологиясында PLD (Programmable Logic Devices) терминімен біріктіріледі. Бағдарламаланған және қайта бағдарламаланған құрылымды ҮИҚ/ҮИҚЖ дамыту бағыттарының қолайлы болуы соншалық, CPLD (Complex PLD), FPGA (Field Programmable GA) және SPGA (System Programmable GA) сияқты сандық жүйелерді өңдеудің жаңа тиімді құралдарын құрастыруға әкеліп соқты. Заманауи бағдарламаланған және қайта бағдарламаланған құрылымды ҮИҚ/ҮИҚЖ аясында біркристалды бүтін жүйені жасау мәселесі де шешімін тапты. 10.1 Бағдарламаланған логикалық матрицалар (ПЛМ) ПЛМ негізі ЖӘНЕ және НЕМЕСЕ бағдарламалық матрица элементтерінің тізбектілігі болып табылады. Құрылымға сондай-ақ кіріс жән шығыс буферлік (Бкір және Б\шығ) каскадтарының блоктары кіреді. ПЛМ-ның негізгі параметрлері m кірістер саны, терімдер саны (коньюкция) L және шығыстар саны n болып табылады (10.1 суретті қара).  10.1 сурет – ПЛМ базалық құрылымы Кіріс буферлері бірфазалы кіріс сигналдарын жұпфазалыққа түрлендіреді және И матрица элементтерін қоректендіру үшін қажетті қуатты сигналдар тудырады. Шығыс буферлері шығыстардың қажетті жүктемелік қабілеттілігін қамтамасыз етеді, ПЛМ сыртқы шиналарға шығысы ОЕ сигналы көмегімен рұқсат етіледі және тыйым салынады. ПЛМ қайта шығарылатын функциялардың екі деңгейлі логикасын (ДҚТ) іске асырады. Қайта шығарылған функциялар И матрицасынан құралған кез-келген терімдер санының жиыны болып табылады. Қандай терімдер өңделетін болады және осы терімдердің қандай жиыны шығыс функцияларын құрайтыны ПЛМ бағдарламалауымен анықталады. 10.1.1 ПЛМ сызбатехникасы. ПЛМ биполярлық технология негізінде, сол сияқты МОП-транзисторлары негізінде де шығарылады. Матрицаларда көлденең және тік байланыс жүйелері бар, бағдарламалауда олардың қиылысу түйіндерінде байланыс элементтері түзіледі немесе жойылады. 10.2 суретте жалғамаларды жалғауды бағдарламаланған биполярлық (буферлері жоқ) ПЛМ К556РТ1 сызбатехникасында көрсетілген.  10.2 сурет – ПЛМ сызбасы Функциялар жүйесін қайта шығару фрагменті келтірілген өлшемділігі 4, 7, 3. К556РТ1 микросхемасының параметрлері болып 16, 48, 8 табылады. И матрицасындағы байланыс элементтері қызметін 10.3 а суретте көрсетілген көлденең және тік шиналарды жалғастыратын, t1 терімін өңдеу тізбектерін бейнеленетін диодтар атқарады. Резистор және қоректену көзімен бірге терімдерді өңдеу тізбектерін кәдімгі И диодтың сызбалары құрайды. Бағдарламалау кезінде сызбада тек қажетті байланыс элементтері ғана қалдырылады, ал қажет еместері жалғамаларды жалғау арқылы жойылады. Аталған жағдайда коньюктор кірісіне Термдер сызықтарына қатысты эмитерлік қайталағыш сызбасы бойынша және шығысқа (көлденең сызықтар) қатысты НЕМЕСЕ схемасын құрайтын транзисторлар (10.3, б суретті қара) НЕМЕСЕ матрицасында байланыс элементтері қызметін атқарады. Қайта бағдарламаланған матрицаларда байланыс элементтерінің (бүтін жалғамалар) болуы сәйкес түйінде нүктемен белгіленеді.  10.3 сурет – ЖӘНЕ (а) және НЕМЕСЕ (б) матрицаларының сызбасы МОП – транзисторлар сызбасында базалық логикалық ұяшық ретінде инвертирлеуші (НЕМЕСЕ-ЕМЕС, ЖӘНЕ-ЕМЕС) қолданады. Де Морган ережесі биполярлы ПЛМ және МОП транзисторындағы ПЛМ функционалдық сипаттамаларының іс-жүзінде сәйкес келуі туралы айтады: егер соңғының кірістеріне биполярлық ПЛМ аргументеріне қатысты инвертирленген аргументтер берсек, онда оның шығысында алынған нәтиже биполярлық ПЛМ шығысынада тек инверсиясымен ғана ажыратылады. Осы жағдайда терім t1 мынаған тең: ал функция: Терімдер саны ПЛМ көрсетілген параметрлеріне L – тең болған деңгейге дейін терімдер саны бойынша минимал функцияларды іздеуді жүргізу керек. Ары қарай азайту қажет етілмейді. Егер көрсетілген ПЛМ өлшемділігі берілген түрдегі есепті шешуді қамтамасыз етсе, онда азайту мүлдем қажет етілмейді. ПЛМ схемаларын көрсетуді қысқарту үшін олардағы ЖӘНЕ, НЕМЕСЕ көпшығысты элементтерін шартты түрде біршығыстыларымен ауыстыру қолданылады. Осындай элементтердің жалғыз кірісі кіріс айнымалыларының бірнеше сызықтарымен қиылысады. Егер қиылысу нүктемен белгіленсе, онда аталған айнымалы бейнеленетін элемент кірісіне беріледі, егер нүкте жоқ болса, онда айнымалы элементке берілмейді. ПЛМ көмегімен ауыстырып-қосқыш функцияларының дизьюнктивті қалыпты түрлерін ғана шығарып қоймай, жақшалық түрлерін де шығаруға болады. Бұл жағдайда әуелі жақшадағы өрнектерді алады , содан соң оларды соңғы нәтиже алу үшін аргумент ретінде қарастырады. Сызбада кері байланыстар пайда болады – аралық нәтижелер шығыстан қайтадан кіріске беріледі. Мысалы, мына функцияны алу керек болсын: Ол үшін ПЛМ мына сызба бойынша қосылуын қолдану керек (10.4 суретті қара).  10.4 сурет – Оперативті жүйесі бар ПЛМ сызбасы | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||