схематехника. Схемотехника

Скачать 0.84 Mb. Скачать 0.84 Mb.

|

|

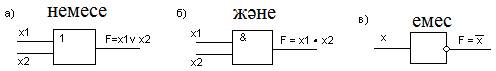

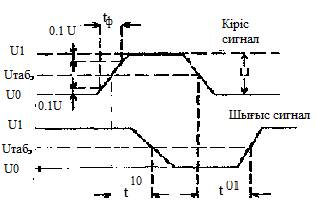

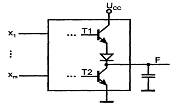

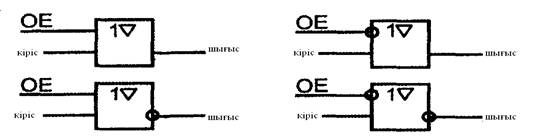

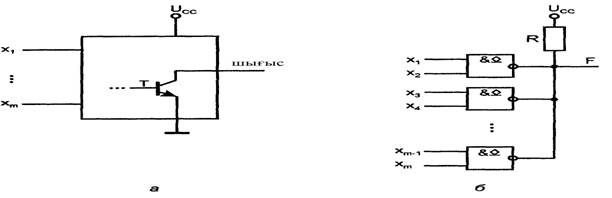

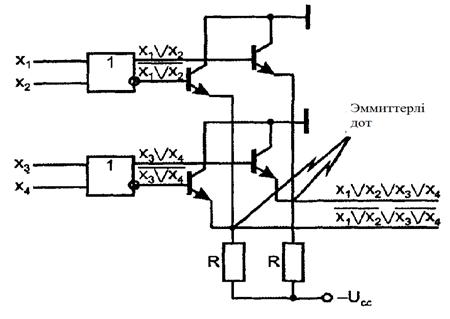

Коммерциялық емес акционерлік қоғамы АЛМАТЫ ЭНЕРГЕТИКА ЖӘНЕ БАЙЛАНЫС УНИВЕРСИТЕТІ «Электроника» кафедрасы СХЕМОТЕХНИКА Дәрістер жиынтығы 5В070400 – Есептеу техникасы және бағдарламалық қамтамасыз ету мамандығының студенттеріне арналған Алматы 2011 ҚҰРАСТЫРУШЫЛАР: А.Т. Ибраев, А.Б. Нусибалиева. Схемотехника. 5В070400 – Есептеу техникасы және бағдарламалық қамтамасыз ету мамандығының студенттеріне арналған «Схематехника» пәні бойынша дәрістер жиынтығы Дәрістер жиынтығында сандық электроника және микропроцессорлық техника негіздерін – заманауи әлемде ерекше орын алатын ғылым мен техниканың қарқынды дамып келе жатқан аймағын қарастырады. Материал жиынтығы студенттің қазіргі заманғы модельдеу және жобалау жүйелерін өздігінен және жүйелі түрде зерттеуге қажетті көлемде қамтамасыз етілген. Дәрістік материал екі бөлімнен тұрады: сандық сызбатехника және микропроцессорлық ҮИЖ. Бірінші бөлімде комбинациялық тізбекті типті сандық құрылғылар, есте сақтау құрылғылары және прграммалық логикалы матрицалар қарастырылған. Екінші бөлім i8085/8086микропроцессорларының құрылымына, командаларға, сонымен қатар микропроцессорлық жүйенің адаптерлары мен контроллерларына арналған. Дәріс жиынтығы сандық құрылғылар мен микропроцессорлық жүйелерді құру негіздерін бекіту мақсатында құрастырылған және 5В070400 – Есептеу техникасы және программалық қамтамасыз ету мамандығының студенттеріне арналған. Без. 84, кестелер 24, әдеб.көрсеткіші – 6 атау. Пікір беруші: техн.ғыл.д-ры., проф. Ш.А. Бахтаев «Алматы энергетика және байланыс университеті» коммерциялық емес акционерлік қоғамының 2011 ж баспа жоспарына сәйкес басылады. © «Алматы энергетика және байланыс университеті» КЕАҚ, 2011 ж. Кіріспе Заманауи қоғамның қажеттіліктерінің тез дамуы, экономиканың әртүрлі саласында кең көлемде қолданылатын Hi-Tec (High Technogy) деп аталатын жаңа технологияны талап етуде. Информатика саласының ірі маманы, академик Е.П.Велихов бір мақаласында «Кімде-кім компьютер құрай білсе, ол әлемді бағындырады» деп өзінің ойын білдірген. Сандық техникалардың барлық әртүрлі құралдары: дербес компьютерлер, өлшеудің микропроцессорлық жүйелері мен технологиялық процессорлардың автоматизациясы, цифрлық байланыс, теледидар, тұрмыстық техника және т.б. құрамына әртүрлі қиын микросхемалардан тұратын біртұтас элементті базадан - қарапайым операциялардан бастап миллион логикалық элементтерден тұратын қиын бағдарламалық кристалдарды орындайтын логикалық элементтерден құрылады. Микропроцессорлар мен бағдарламалық құрылымды үлкен интегралдық схемалардың (ҮИС) (БИС), пайда болуынан автоматика құралдарын жасауға және жобалау әдістеріне сапалы өзгерістер болды. Микропроцессор – бұл бір немесе бірнеше үлкен интегралды схемалар (ҮИС) (БИС) түрінде жүзеге асырылған функционалды процессор. Микропроцессор өзінің жүйесіне кіретін командаларды орындауға қабілетті. Командалардың тізбектелуін өзгерте отырып, бір микропроцессорда әртүрлі есептерді шешуге болады. Микропроцессорлы топтама – белгілі бір командалар топтамасы көмегімен жұмысты басқару мүмкіндігіне ие болатын ҮИС жиынтығы. Микропроцессорлы жүйе өзінің құрылымы бойынша дербес компьютерге ұқсас, бірақта, ішкі әлеммен беттесу құралдарының жиынтығы және жадысының көлемі шектеулі. Микропроцессорлық жүйені құрудың негізінде бағдарламалық-аппараттық принцип жатыр. Бір стандартты микропроцессорлық жүйенің бағдарламасын ауыстыра отырып, оны көптеген құрылғылар мен жүйелерде қолдануға болады: техникалық процестегі автоматты басқаруда, техникалық диагностикалар жүйелерінде және күзету жүйелерін қосу арқылы объектілердің жағдайын бақылауда. Бағдарламаланатын құрылымды СҮИС-тің негізгі ерекшелігі микросхема құрылымын өзгерте отырып, бағдарламалы түрде әртүрлі блоктарды қоса алуында. Микропроцессорлар мен СҮИС-ті оқып үйренбес бұрын, микропроцессор құрамындағы маңызды цифрлық элементтермен және құрылғылармен танысуымыз керек. 1 Дәріс. Цифрлық құрылғының логикалық элементтері Цифрлық ақпараттарды түрлендіру 0 және 1 логикалық айнымалылары негізінде логикалық ЖӘНЕ, НЕМЕСЕ, ЕМЕС элементтері арқылы жүзеге асады. Логикалық элементтердің шартты белгілері - орындалатын операция таңбасы қойылған тіктөртбұрыш, (терістеу операциясының белгісі дөңгелек түрінде болады).  1.1 сурет – Логикалық элементтердің шартты белгілері Схемаларда 0 және 1 айнымалылары әртүрлі екі кернеу арқылы кескінделеді: Uo және U1 . Кернеудің екі деңгейінің қайсысы Uo үшін, қайсысы U1 үшін қабылдау керектігін келісу керек. Оң және теріс логикалар деген ұғым бар. Оң логикада U1 > Uo, ал теріс логикада U1 < Uо. Ары қарай, егер қателеспесек, оң логиканы қолданамыз. Бір түрлі логикалық айнымалыларды түрлендіру әртүрлі формаларда: ЖӘНЕ, НЕМЕСЕ, ЕМЕС операцияларының көмегімен (буль базисі), ЖӘНЕ-ЕМЕС операциялары (Шеффер базисі), НЕМЕСЕ-ЕМЕС операциялары (Пирс базисі), сондай-ақ басқа да көптеген әдістермен беруге болады. Көбіне Пирс және Шеффер базистері кездеседі. 1.1 Логикалық элементтердің статикалық параметрлері Статикалық параметрлер дегеніміз логикалық элементтердің (ЛЭ) кірісі мен шығысында кескінделетін айнымалылар (0 және 1) шекарасында кескінделетін кернеу мәндері: 1) кірісі бойынша Uкір1min және Uкір0mах.; 2) шығысы бойынша Uшығ1min және Uшығ0max және ток мәндері: 3) кірісі бойынша Iкір1max және Iкір0mах; 4) шығысы бойынша Iшығ1mах және Iшығ0mах. Элементтер дұрыс жұмыс жасау үшін логикалық 1 кескіндейтін кернеу мейлінше жоғары, ал логикалық 0 кескіндейтін кернеу төмен болуы талап етіледі. Бұл талаптар Uкір1min және Uкір0mах. параметрлеріне қойылады. Осы элементтің кіріс кернеуі алдыңғы элементтің шығыс кернеуі (сигналдар көзі). Жүктемелік шарттарды орындағанда сақталатын элемент шығысындағы элементтер деңгейі Uшығ1min және Uшығ0max параметрлері арқылы беріледі. Шығыс кернеуінің жоғарғы деңгейінде элемент қорек көзінен ток ағып, жүктеме тізбегі токты сіңіреді. Элемент қорек көзінің шығыс кернеуінің төменгі деңгейінде ток осы элементке құйылып, ал қабылдағыш элементтерінің кіріс тізбегінен токтар ағады. Сигналдың қорек көзі элементтерінің мүмкіндіктерін сипаттайтын Iшығ1mах және Iшығ0mах токтарын, қабылдағыш элементтеріне қолданылатын Iкір1max және Iкір0mах токтарын біле отырып, схеманың барлық элементтері үшін жүктемелік шектелуді сақтауды бақылауға болады. Логикалық элементтердің тезәсерлігі олардың бір күйден екінші күйге ауысу жылдамдығымен анықталады. 1.2 суретте ЕМЕС логикалық элементінің жұмысының уақыттық диаграммасы көрсетілген. Логикалық сигналдың өзгеру уақыты олардың Uтаб, табалдырық деңгейіне жету уақыты болып саналады, ол үшін сигналдың логикалық төмендеуінің ортасын алады 0,5(Uо + U1).  1.2 сурет – ЕМЕС логикалық элементі жұмысының уақыттық диаграммасы ЦҚ тезәсерлігіне, сондай-ақ қайта зарядтауға уақыт жұмсауды талап ететін сыйымдылықта әсер етеді. Анықтамалық мәліметтерде схема түйіндерінде жүктеме сыйымдылығын есептеуге мүмкіндік беретін логикалық элементтердің кіріс және шығыс сыйымдылықтары келтірілген. 1.2 ЦЭ шығыстарының типтері Цифрлық элементтердің (логикалық, есте сақтау, буферлі) шығыстарының келесі типтері бар: - логикалық; - ашық коллекторлы (стоком); - үшінші жағдайлы; - ашық эммиттерлі (истоком). 1.2.1 Логикалық шығыс. Логикалық шығыс кернеудің екі деңгейін қалыптастырады (Uо және U1). Логикалық шығыстың шығыс кедергісі жоғарғы тезәсерлік алу үшін және сыйымдылықты жүктемені қайта зарядтау үшін үлкен токтарды бөлшектеуге қабілетті. Шығыстың бұл түрі ішкі схемаларда қолданылады (дешифраторларда, мультиплексорларда, сумматорларда). ТТЛ және КМОП элементтерінің логикалық шығыстарының схемалары екі тактілі каскадтарға ұқсас – оларда шығыс кернеудің екі фронты активті транзисторлар қатысуымен қалыптасады, олар шығысты ауыстырудың кез-келген бағытында аз шығыс кедергісін қамтамасыз ету үшін жұмыс жасайды. (1.3 суретті қара).  1.3 сурет - Цифрлы элементтің шығыс тізбегінің схемасы Бұндай шығыстың ерекшелігі, оларды параллель жалғауға болмайтынында. Біріншіден, шығыстарды байланыстыратын нүктеде логикалық 1 қалыптасады, ал логикалық 0 қалыптасатын шығыста қалыпты нәтиже болмайды. Екіншіден, шығыс кедергінің шамасы аз болғандықтан, теңестіруші ток үлкен шамаға ие болуы мүмкін, ол шығыс тізбектің электрлік элементтерін істен шығаруға әкеп соғады. 1.2.2 Үш шығыс күйі бар элементтер. Үш шығыс күйі бар элементтері (ТС типті) 0 және 1 логикалық күйден басқа "ажыратылған" деген күйге ие, бұл кезде шығыс тізбек тогы өте аз болады. Бұл күйде элемент арнайы басқарылатын сигналға ауыстырылады, ол шығыс каскадындағы екі транзистордың (Т1 және Т2) жабық болуын қамтамасыз етеді (1.3 суретті қара). ТС типті элементімен сигналды басқару әдетте ОЕ (Output Enable) деп белгіленеді. Рұқсат (ОЕ = 1) болғанда элементтер өзінің логикалық операцияларын орындайды, ал болмаса (ОЕ = 0), "ажыратылған" күйіне ауысады. ЦҚ–да басқарылмалы сигналдарды таратуда ТС типті буферлі элементтер кең қолданылады. Буферлер терістейтін және терістемейтін болуы мүмкін, ал ОЕ сигналдары — төрт типті буферлік каскадтарға келтіретін Н-активті немесе L-активті болады (14 суретті қара). Элементтерде ТС типті шығыстар үшбұрышты белгілермен белгіленеді. ТС типті шығыстарды уақыттың кез-келген моментінде олардың тек біреуі ғана активті болған кезде ғана параллель жалғауға болады. Бұл жағдайда ажыратылған шығыстар байланысқан нүктеде сигналдардың активті қалыптасуына кедергі жасамайды. Бұл мүмкіндік ТС типті элементтерді магистральды-модульді микропроцессорларда және бір байланыс желісінде ақпарат көздері кезектесіп қолданылатын жүйелерде қолдануға болады.  1.4 сурет - Үш күйлі буферлік каскадтардың типтері 1.2.3 Ашық коллекторлы шығыс. Ашық коллекторлы элементтерде коллекторы микросхема ішіндегі тізбектің ешқайсысымен жалғанбаған жеке транзистормен аяқталатын шығыс тізбегі бар (1.5,а суретті қара). Транзистор элементтің схемасының алдыңғы бөлігінен басқарылады, ол қаныққан немесе жабық күйде болуы мүмкін. Қаныққан күй логикалық 0 секілді, ал жабық логикалық 1 секілді жол салады. Транзистордың қанығуы шығыста Uо (қанығудың ең аз кернеуі коллектор-эмиттер" Uкэқ) кернеуін қамтамасыз етеді. Кернеудің кез-келген деңгейінде транзистордың бекітілуі элемент шығысында болмайды, осы кезде шығыста белгісіз "өзгермелі" мүмкіндікке ие, ол элемент схемасының ешқандай тізбегіне жалғанбаған. Сол себепті, жоғарғы деңгейлі кернеуді қалыптастыру үшін элемент шығысында ашық коллекторда (ОК типті) транзисторды бекіткен кезде, қорек көзіне қосылған ішкі кедергілерді (немесе басқа жүктемелерді) қосу талап етіледі. ОК типті бірнеше шығыстарды барлық шығыстарға ортақ Ucc - R ( 1.5, б суретті қара) тізбекке қосып, параллель жалғауға болады. Бұл кезде жалпы тізбекте элементтердің кезектесу жұмыс режимін алуға болады, ТС типті элементтер үшін бір элемент активті болса, қалғандарының шығыстары жабық болады. Егер де шығыстары қосылған элементтердің активті жұмыс істеуіне рұқсат етілсе, онда қосымша логикалық операцияларды алуға болады, оны монтажды логика операциясы деп атауға болады.  1.5 сурет - ЦЭ ашық коллекторлы шығыс тізбегінің (а) және ЖӘНЕ операциясын жүзеге асыру (б) схемасы Монтажды логиканы жүзеге асырғанда ортақ шығыста жоғарғы кернеу тек барлық транзисторларды бекіткенде ғана пайда болады, тек олардың біреуінің ғана қанығуы шығыс кернеуін Uo = Uкэқ деңгейіне дейін төмендете алады. Шығыста логикалық бірлік алу үшін барлық шығыстардың жекелік күйлері талап етіледі: ЖӘНЕ операциясы орындалады. Әрбір элемент өздерінің кіріс айнымалыларымен Шеффер операциясын орындағандықтан, ортақ нәтиже келесідей болады ОК элементтердің белгіленуінде таңбадан кейін астында сызығы бар ромб қойылады. 1.2.4 Ашық эммиттері бар шығыс Ашық эмиттерлі шығыс ЭБЛ (эмиттерлі-байланысқан логика) типті элементтер үшін сипатты. Магистральда жұмыс істеу үшін бұндай элементтер қолданылмайды. Ашық эмиттерлі шығыстарды бір-бірімен біріктіру мүмкіндігі эмиттерлі резисторларды үлкен бір резисторға біріктірген кезде "эмиттерлі дот" деп аталатын схемаға келтіреді (1.6 суретті қара), ол қосымша монтажды логикалық схемалар алу үшін қолданылады.  1.6 сурет - "Эмиттерлі дот" схемасы ЭБЛ элементтерінің біреуінде НЕМЕСЕ функциясы, ал басқасында НЕМЕСЕ-ЕМЕС функциясы іске асатын фазаға қарсы элементтері бар. Бірнеше элементтердің тура шығыстарын байланыстырып кеңейтілген НЕМЕСЕ алуға болады (байланыстыратын элементтердің кіріс айнымалылары біртұтас дизъюнкция қалыптастырады). Терістелген шығыстарды біріктіріп, кіріс айнымалылар терістелуіне қатысты ЖӘНЕ-НЕМЕСЕ операциясын алуға болады, бұл кезде Тура шығысты терістеумен байланыстырып, функцияны мына түрде алуға болады: 2 Дәріс. Комбинациялы типті ЦҚ 2.1 Жобалау сатылары Функционалды тораптар комбинациялы және тізбектелген болып екіге бөлінеді. Ары қарай комбинациялық торапты КТ (комбинациялы тізбек) арқылы, ал тізбектелгенді ЖА (жадылы автомат) арқылы белгілейміз. КТ мен ЖА негізгі айырмашылықтары мынадай: - КТ-ның шығыс шамалары тек ағымдағы кіріс шамаларға (аргументтерге) тәуелді, бастама мәндері жоқ. КТ-да өтпелі кезең аяқталған соң, олардың шығысында өтпелі кезең сипаттары әсер етпейтін шығыс шамалары қондырылады. Бірақ та, цифрлық құрылғыларда КТ жадылы автоматпен бірге функцияланады: өтпелі кезең кезде КТ шығысында тәуекел деп аталатын уақытша сигналдар пайда болады. Уақыт өткен сайын олар жойылып, КТ шығысында тізбек жұмысын сипаттайтын, логикалық формуламен қарастырылатын мәндерге ие болады. Бірақта, КТ шығысындағы тәуекелдердің жойылып кетуіне қарамастан, ЖА жұмысын радикалды өзгертетін тәуекелдер ЖА жадысының элементтерімен қабылдануы мүмкін. ЦҚ жұмысында тәуекелдер пайда болғандықтан үзіліс болмау үшін, өтпелі кезең уақытында жадының КТ элементтерімен сигнал қабылдауға тиым салынады. КТ шығысынан ақпараттарды қабылдау, КТ-да өтпелі кезең аяқталғаннан кейін жады элементтеріне түсірілетін, тек қана синхрондаудың арнайы сигналдарымен рұқсат етіледі. Сондықтан, жады элементтерінде жалған сигналдар әсері болмайды. Сәйкес құрылымдар синхронды деп аталады. Комбинациялы типті туынды логиканы жобалау сатылы түрде жүзеге асады. Ең алдымен, КТ функциялау сипаты беріледі. Бұл әртүрлі әдістермен жасалынуы мүмкін, көбіне барлық аргументтерді жинақтап, іздеген функция мәндерін беретін ақиқат кестесін қолданды. Кестеден іздеген функция ЖДҚТ –ке (ЖДҚТ (СДНФ) – жетілдірілген дизъюнктивті қалыпты түр немесе конъюктивті мүшелер дизъюнкциясы бірдей мөлшерде) өту оңай. Ол үшін, біртұтас мәндерді қабылдайтын функция, сол аргументтердің жиынтығының логикалық қосындысын құрастырады. Мысалы, 2.1-кестеде берілген үш аргумент үшін функцияны жаңғырту үшін ЖДҚТ аламыз 2.1кесте - ЦҚ-ның ақиқат кестесі

Басқа әрекеттер, заманауи схематехникаға қатысты функцияларды жүзеге асыру құралдарына тәуелді: 1) Кестелі типті логикалық блоктар (LUTs, Look-Up Tables). 2)ЖӘНЕ мен НЕМЕСЕ элементтерінің тізбектелген матрицасы түріндегі логикалық блоктар (PLA, Programmable Logic Array; PAL, Programmable Array Logic). 3) Мультиплексор (ӘЛМ) негізіндегі әмбебап логикалық блоктар. 4) Кейбір базистардағы логикалық элементтерден құралған логикалық блоктар (SLC, Small Logic Cells). 1. Егер КТ кестелі типті логикалық блоктар негізінде жүзеге асырылса, онда ЖДҚТ функцияның ақырғы өрнегі болады және бұл түрге ары қарай ешқандай түрлендіру талап етілмейді. Кестелі блок функцияның барлық мәндерін сақтауға қажет көп ұялы жадыны көрсетеді, немесе 2m, мұндағы m – функция аргументтерінің саны. Аргументтерді теру функция (0 немесе 1) мәндері сақталатын ұяшықтар мекен-жайы болып табылады. ЖДҚТ–та функцияның біртұтас мәндерін сақтауға қажетті барлық мекен - жайлар бар. Егерде, іздеген функция қандай-да бір қысқартылған түрде өрнектелсе, онда оны ЖДҚТ–ге ауыстыру қажет. Ол үшін хj айнымалысы жоқ конъюктивті мүшелер дизъюнкцияның тең бірліктеріне көбейтіледі Мысалы, 2. Егер бұл жоба ЖӘНЕ мен НЕМЕСЕ элементтерінің тізбектеліп қосылған матрица түрінде логикалық блоктар негізінде жүзеге асса, онда бастапқы ЖДҚТ-ны ықшамдауға болады. ЖӘНЕ мен НЕМЕСЕ матрицалы логикалық блоктар жүйелерді айырып-қосқыш функция ретінде көрсетеді: кірістер, шығыстар және терім сандары. Ықшамдаудың мақсаты функцияның бұл жүйесінде конъюнктивті терімдер санын қысқарту немесе төте дизъюнктивті түрлерді қысқарту болып табылады. Бұл дизъюнктивті қалыпты түрдің (ДҚТ) ең төменгі түрін іздеуге әкеліп соғады. 3. Мультиплексор негізіндегі логикалық блоктар 3-тақырыпта қарастырылған. 4. SLC типті немесе вентильді деңгейде логикалық блокта КТ-ны жинақтау дәстүрлі болып табылады. ("вентиль" терминімен қарапайым операцияларды орындайтын базалы логикалық ұяшықтарды атайды, мысалы, екі-үш кірісі бар ЖӘНЕ-ЕМЕС элементтері). Бұл нұсқада КТ жобалау келесі сатылардан тұрады: - логикалық функцияларды ықшамдау; - берілген логикалық базиске өту . Ықшамдау – логикалық функцияны берілген шарттан мағынасын оңайлату үшін түрлендіреді. Алғашында схемадағы жүзеге асыратын өрнекте әріптер саны түрінде қиындықтар шартына әкеліп соғатын логикалық элементтер санын ықшамдауға тырысты. Бұл шарттар схеманың барлық логикалық элементтері кірістерінің қосындысы Квайн бағасы бойынша есептеледі. Бұл шарттар бойынша ықшамдау үшін математикалық өрнекті түрлендіру негізінде бірнеше әдістер жасалған, егерде аргументтер саны 6-дан аз болса, Карно картасын (Вейча диаграммасы) қолдану ыңғайлы. Жобалаудың келесі әдісі – әдетте Буль базисінен (ЖӘНЕ, НЕМЕСЕ, ЕМЕС) алатын бастапқы өрнектен берілген логикалық базиске өту. Бұндай өту ережесі белгілі: олар де-Морген теоремасын қолдануға негізделген. Шеффер базисіне (ЖӘНЕ-ЕМЕС) өту үшін мына қатынас қолданылады. ал Пирс базисіне (НЕМЕСЕ-ЕМЕС) өту үшін, алдымен іздейтін функцияны терістеу жолымен бастапқы буль түрін алған ыңғайлы, содан кейін НЕМЕСЕ-ЕМЕС базисіне келесі қатынаспен өтуге болады |