схематехника. Схемотехника

Скачать 0.84 Mb. Скачать 0.84 Mb.

|

|

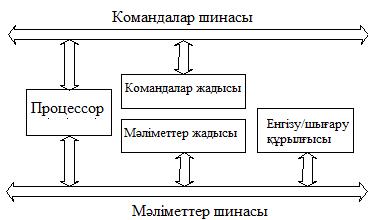

10.2 Бағдарламаланатын матрицалық логика (ПМЛ) ПЛМ-да (10.5 суретті қара) ЖӘНЕ элементтерінің шығыстары (бірінші матрица шығыстары) НЕМЕСЕ элементтерінің (НЕМЕСЕ матрицасының шығыстары) арасында қатаң таратылған.  10.5 сурет – ПМЛ сызбасы Көрсетілген ПМЛ-да m кірістері, n шығыстары және И элементінің 4n элементтері бар, себебі әрбір НЕМЕСЕ элементіне төрт конъюктордан беріледі. ПЛМ-мен салыстырғанда ПМЛ сызбалары аз функционалдық иілгіштікке ие, себебі оларда НЕМЕСЕ матрицасы бекітілген, бірақ олардың жасалуы және қолданылуы қарапайымырақ. ПМЛ үшін әрбір шығыс үшін ЖӘНЕ элементтер санын азайтқан маңызды, бірақ егер ПЛМ үшін функцияны беру де жалпы терімдер саны көп болатын жағдайға ұмтылса, ал ПМЛ үшін бұл қажет емес, себебі ЖӘНЕ функциялары өз шығыстарына бекітілген және басқа шығыстармен қолданыла алмайды (яғни басқа функциялар үшін). 10.3 Базалық матрицалық кристалдар Жартылай тапсырысты БИС/СБИС дамыту олардың бірнеше түрлерінің пайда болуына әкеліп соқты. БМК қатысты – бұлар каналды, каналсыз және блокты архитектуралар. БМК термині орыс тіліндегі әдебиеттерге тән. Ағылшын терминологиясында GA (Gate Array) термині алынған, яғни аударғанда – вентилді матрица дегенге сәйкес келеді. Бірінші ұрпақ БМК негізі – кристалды ретпен орналасқан базалық ұяшықтардың (БҰ) жиынтығы, олардың арасындағы еркін зоналар қосылуларды (каналдарды) жасау үшін арналған бос зоналар бар. Бұл архитектура каналдық деп аталады. Базалық ұяшықтар БМК ішкі облысын алып жатады. Онда олар жолдар мен бағандар бойынша орналасқан және олардың құрамында коммутирленбеген элементтер (транзисторлар, резисторлар және т.б) тобы бар. Кристалдың периферийлік облысында кіріс/шығыс ұяшықтары, сызбалық құраушылар жиыны орналасқан, олар БМК сыртқы тізбектерден байланысын іске асыруға арналған. Осылайша ПМК қажетті қосылыстарды іске асыра отырып, талап етілетін схемаға айналатын алдын-ала дайындық болып табылады. Қолданушы ПМК негізінде кристалға қосылысатын компоненттердің сол немесе басқа суретін бере отырып, белгілі бір класты қондырғылардың көбін жүзеге асыра алады. Алғашқы БМК (Amdahl Corp. фирмасы, АҚШ) ЭСЛ сызбатехникасында орындалған, оны толық дайындау процесіне фотошаблонды 13 операциядан тұрады. БМК негізіндегі (осындай сызбаларды МАБИС немесе БМИС) сызбаларды дайындау үшін аралық қосылыстардың суретін беруде 3 жеке (айнымалы) шаблондар қажет болады. Осыған сәйкес МАБИС мерзімдері мен жобалау құны толық тапсырыс берілген БИС/СБИС-қа қарағанда 3-5 есе кем. Қазіргі уақытта БМК интеграциялау деңгейі кристалда миллион шұраға жетті. БМК жобалау кезінде жақсы жолмен базалық ұяшықтар санын, оларды трассирленген кристалл ресурстарын және сыртқы шығыстарды қосу үшін контактілі аудандар санын теңестіруге тырысады. Негізгі ұғымдар мен анықтамалар. Базалық ұяшық (БҰ) – кристалдың берілген ауданында үнемі қайталанатын сызбалық элементтердің жиыны. Бұл жиын коммутирленбеген элементтерден, сондай-ақ жартылай коммутирленген элементтерден тұрады. БМК ішкі облысының базалық ұяшықтары матрицалық базалық ұяшықтар (МБҰ), ал периферилік белдеу ұяшықтары периферийлік базалық ұяшықтар (ПБҰ) деп аталады. БМК ұйымдастырудың екі тәсілі қолданыс тапқан: - МБҰ элементтерінен бір логикалық элемент құрастырылады, ал одан да қиынырақ функцияларды іске асыру үшін бірнеше ұяшық қолданылады - МБҰ элементерінен кез-келген функционалдық түйін құрылуы мүмкін, ал ұяшық элементтерінің құрамын күрделі түйін өз сызбасымен анықтайды. Функционалды ұяшық (ФҰ) – функционалды біткен сызба бір немесе бірнеше сызба БҰ элементтерін қосу жолымен іске асырылады. Функционалдық ұяшықтар кітапханасы – МАБИС-ті жоспарлауда қолданылатын ФҰ жиынтығы. Бұл кітапхана БМК құрастыруда жасалады және МАБИС жобалаушысын кристалды ОСН осы немесе басқа типтес сызбаларды жасау жұмыстарынан босатады, яғни оларды іске асыру үшін дайын шешімдер ұсынады. Кітапхана құрамына функционалдық элементтер, түйіндер және олардың бөліктерінің үлкен саны (жүздеген) кіреді. Жобалаушы кітапхананы пайдалана отырып, жұмыс қабілеттілігі тексеруден өткен, параметрлері белгілі сызбаларды іске қосады. Кітапханамен жұмыс істей отырып, ол функционалды-логикалық деңгейде жоспарлау жүргізеді, себебі сызбатехникалық деңгей мәселелері кітапхананы құру кезінде шешілген болады. Кітапхана элементтерінің (логикалық элементтер, триггерлер, одан да қиын түйіндер және олардың фрагменттері) қиындығы әртүрлі болып келеді. Кітапхана элементі құрамына бір немесе бірнеше БҰ кіруі мүмкін. Кітапхана элементі ауданы БҰ ауданына еселік болып келеді. МАБИС жобалауда дайындалған құрылғының функционалдық сызбасы кітапхана элементтерімен жабылған болуы керек деп айту қабылданған. Эквивалентті вентиль (ЭВ) – вентильдың логикалық функциясын іске асыру мүмкіндігіне сәйкес келетін БМК элементтер тобы (екікірісті ЖӘНЕ-ЕМЕС элементі не болмаса НЕМЕСЕ-ЕМЕС). Эквиваленттік вентиль ұғымы БМК логикалық қиындығын бағалауға арналған. Тасымалдау каналдары – аралық қосуларды орналастыру мүмкіндігінің БМК жолдары. БМК тасымалдау қабілеттілігі – ортогональді бағыттардағы элементаралық байланыстар үшін бөлінген аудан. Аралық қосулар қабаттар саны да ескеріледі. 11 Дәріс. МПЖ архитектурасы 11.1 МПЖ негізгі міндеттері МПЖ келесі негізгі міндеттерді шешеді: - ақпарат жинау; - өңдеу; - өлшеу нәтижелерін беру және (қажет болған жағдайда) осы мәліметтерді байланыс каналы бойынша жіберу. МПЖ ақпараттық (Hard Ware) және бағдарламалық в (Soft Ware) құралдарының жиынтығын құрайды. Ақпараттық құралдар жоғары өнімділік немесе тез әсерлікті, ал бағдарламалық құралдар –МПҚ шешетін міндеттерінің аясын үлкейтеді. Микропроцессор (МП) - кез-келген микропроцессорлық жүйенің орталық бөлігі – оған АЛҚ және командалық циклді жүзеге асыратын басқару құрылғысы кіреді. МП мен МПҚ құрамында ғана жұмыс жасай алады, оның құрамына жады, енгізу/жіберу құрылғылары, қосымша сызбалар (тактілік генератор, үзу контроллері және ПДП, шиналық құрастырушылар, регистр-қысқыштар және т.б.) кіреді. Процессорда барлық командалар жүйесі орналасқан. Процессор командалар жүйесінің құрылымы және көлемі оның тезәсерлігін, иілгіштігін, қолдану ыңғайлылығын анықтайды. Процессордағы барлық командалар саны бірнеше ондықтан бірнеше жүздікке дейін болуы мүмкін. Командалар жүйесі шешетін міндеттердің тар аумағына (арнайы жабдықталған процессорлар) немесе міндеттердің кең аумағына (әмбебап процессорлар) есептелген болуы мүмкін. Команда кодтары әртүрлі разрядтар санын (1 ден 8 байтқа дейін) иеленуі мүмкін. Әрбір команданың өзінің орындалу уақыты болады, сондықтан барлық бағдарламаны орындау уақыты мен бағдарламадағы командалар санынан ғана емес, сол сияқты қандай қомандалардың қолданылуына байланысты болып келеді. 11.2 Байланыстардың шиналық құрылымы Микропроцессорлық жүйелерде максимал әмбебаптылық және ақпараттармен ауысу хаттамаларын қысқарту үшін жүйеге кіретін жеке құрылғылар арасындағы байланыстардың шиналық құрылымы қолданылады. Байланыстардың шиналық құрылымында құрылғылар арасындағы барлық сигналдар тек бір ғана байланыс сызықтары бойынша, бірақ әртүрлі уақытта (бұл мультиплексирленген берілу деп аталады) беріледі. Сондай-ақ барлық байланыс сызықтары бойынша екі бағытта жүргізіледі (екібағытты берілу деп аталады). Нәтижесінде байланыс желілерінің саны едәуір қысқарады, ал ауысу ережесі (хаттамалар) қысқартылады. Сигналдар немесе кодтар берілетін байланыс сызықтары тобы шина (ағылш. bus) деп аталады. Артықшылығы: шинаға қосылған барлық құрылғылар тек бір ғана ереже бойынша (шина бойынша ақпаратты ауыстыру хаттамасы) ақпаратты қабылдап және жіберуі керек. Осы құрылғыларда шинамен ауысуға жауапты барлық түйіндер біртүрлі, унифицирленген болуы керек. Кемшілігі: барлық құрылғылар әрбір желіге параллель қосылады. Сондықтан, ол барлық байланыс сызығын істен шығарса, кез-келген құрылғының істен шығуы басқа желілердің істен шығуына әкелуі мүмкін. Шиналық құрылымды байланыстар жүйесінде сандық микросхемалардың шығыс каскад түрлерінің үшеуін де қолданады: - стандартты шығыс немесе екі күйдегі шығыс ( 2С, 2S реті ТТЛ, TTL сирек белгіленеді); -ашық коллектормен шығыс (белгіленуі ОК, OC); - үш күймен шығыс немесе (сол сияқты) ажырату мүмкіндігімен шығыс (белгіленуі - 3С, 3S). 2С шығысында екі кілт кезекпен жабылады, бұл логикалық бірлік деңгейіне сәйкес келеді (жоғары кілт жабық) және логикалық нөл (төменгі кілт жабық). АК шығысында жабық кілт логикалық нөл деңгейін, ал ағытылғаны логикалық бірлікті қалыптастырады. 3С шығысында кілттер кезекпен жабылуы (2С жағдайы сияқты) мүмкін, үшінші жоғары импеданстық күй тудырып, біруақытта ажыратылуы мүмкін. Үшінші күйге (Z-күй) көшу EZ арнайы кірісінде сигналмен басқарылады (11.2 суретті қара).  11.2 сурет - Санды микросхемалар шығыстарының үш типі 3С және АК типті шығыс каскадтары микросхемалардың бірнеше шығыстарын мультиплексирленген немесе екі бағытты алу үшін біріктіреді. (11.4 суретті қара).  11.3 сурет - Мультиплексирленген сызық  11.4 сурет - Екібағытты сызық Бұл кезде 3С шығыстарын желіде әрқашан тек бір активті шығыс жұмыс істеу үшін қамтамасыз ету қажет, ал қалған шығыстардың барлығы осы уақытта үшінші күйде болатындай етіп қамтамасыз ету керек, басқаша болғанда қақтығыстар болуы мүмкін. АК жалпы алынған шығыстары барлығы ешқандай қақтығыссыз біруақытта жұмыс істеуі мүмкін. МПЖ типтік құрылымы 11.6 суретте келтірілген. Оның құрамына 3 негізгі құрылғы типі енеді. - процессор; - мәліметтер мен бағдарламаларды сақтауға арналған оперативті жады (ОЗУ, RAM — Random Access Memory) мен тұрақты жадыдан (ПЗУ, ROM —Read Only Memory) тұратын, жады, оперативті жады. Микропроцессорлық жүйенің сыртқы құрылғылармен байланысы үшін, кіріс сигналдарын қабылдау (енгізу, оқу, Read) үшін және шығыс сигналдарын тарату ( шығару, жазу, Write) үшін қолданылатын, енгізу/жіберу құрылғысы (УВВ, I/O - Input/Output Devices). Микропроцессорлық жүйенің барлық құрылғылары жалпы жүйелік шинамен (жүйелік магистральмен) біріктіріледі. Жүйелік магистраль өзіне 4 негізгі төменгі деңгейдегі шинаны кіргізеді: - агрес шинасы (Address Bus); - мәліметтер шинасы (Data Bus); - басқару шинасы (Control Bus); - қоректену шинасы (Power Bus). Шина адресі (ША) процессордың дәл осы уақытта ақпаратпен алмасу уақытындағы құрылғы адресін (ретін) анықтау үшін қажет. Әрбір құрылғыға (процессорден басқа), микропроцессорлық жүйедегі жадының әрбір ұяшығына меншікті адрес беріледі. Қандай да бір адрес коды қойылатын болса, осы адрес жазылған құрылғы оған ақпаратпен ауысу керек екенін түсінеді. Шина адресі бірбағыттық немесе екібағыттық болуы мүмкін. Мәліметтер шинасы (МШ) – микропроцессорлық жүйенің барлық құрылғылары арасындағы ақпараттық кодтарды беру үшін қолданылатын ең негізгі шина. Әдетте ақпаратты жіберуде процессор қатысады, ол мәліметтер кодын қандай да бір құрылғыдан немесе жады ұяшығынан береді, немесе қандай да бір құрылғыдан немесе жады ұяшығынан мәліметтер кодын қабылдайды. Құрылғылар арасында ақпаратты жіберу процессордың қатысуынсыз да болуы мүмкін. Мәліметтер шинасы әрқашан екібағытты. Басқару шинасының (БУ) адрес шинасы мен мәліметтер шинасынан айырмашылығы оның жеке басқарылатын сигналдардан тұратыны болып табылады. Осы сигналдардың әрқайсысы ақпарат ауысу кезінде өзінің функциясын атқарады. Кейбір сигналдар берілген немесе қабылданған сигналдарды стробирлеу үшін (яғни ақпараттық код шинаға қойылатын уақыт мезеттерін анықтайды) қызмет атқарады. Қоректендіру шинасы ақпараттық сигналдарды қайта жіберу үшін емес, жүйені қоректендіруге арналған. Ол қоректендіру желісінен және ортақ сымнан тұрады. Микропроцессорлық жүйеде бір қоректендіру көзі ( көбінесе – 5 В, +12 В и –12 В) болуы мүмкін. Әрбір қоректендіру кернеуіне өзінің байланыс желісі сәйкес келеді. Кез-келген жады ұяшығына бару үшін процессор оның адресін шина адресіне қойып және оның ақпараттық кодын мәліметтер шинасы бойынша жібереді немесе одан мәліметер шинасы бойынша ақпараттық кодты қабылдап алады. Жадыда (оперативті және тұрақты) басқарушы кодтар (бағдарлама процессорымен орындалатын командалар) болады, оларды да процессор мәліметтер шинасы көмегімен оқиды. Тұрақты жады негізінен микропроцессорлық жүйенің бастапқы қосу бағдарламасын (BIOS) сақтау үшін қолданылады, ол әрбір қоректендіру қосылған сайын орындалып отырады. 11.3 МПЖ жұмыс режимі Іс жүзінде кез-келген дамыған МПЖ (оның ішінде компьютер) магистраль бойынша үш негізгі режимді ұстайды: - ақпаратпен бағдарламалық алмасу; - үзілістерді қолдану арқылы ауысу (Interrupts); - жадыға тура ену жолын пайдалану арқылы ауысу (ПДП, DMA — Direct Memory Access). Ақпаратпен бағдарламалық ауысу кез-келген МПЖ негізгісі болып табылады. Ол әрқашан қарастырылады, онсыз басқа ауысу режимдері мүмкін емес. Бұл режимде процессор жүйелік магистральдің иесі болып табылады. Осы жағдайдағы ақпаратпен ауысудың барлық операциялары (циклдары) МПС. Ол тек процессормен іске асырылады, олардың барлығы орындалатын бағдарламада жазылған ретпен қатаң орындалады. Үзулер туралы ауысулар қандай да бір сыртқы оқиғаға МПЖ реакциясы қажет болғанда сыртқы сигнал келуіне жұмсалады. Компьютер жағдайында сыртқы оқиға ретінде, клавиатура тетігіне басу немесе локалды жүйе бойынша мәліметтер пакетінің келуі болуы мүмкін. Компьютер оған көңіл аударып, яғни символдың экранға шығуы немесе жүйе бойынша алынған патентті оқуы немесе өңдеуі керек. Жалпы жағдайда сыртқы жағдайға әсерді ұйымдастырудың үш жолы бар: - оқиғаның тұрақты бағдарламалық бақылау фактісінің туындауы арқылы жүйелі магистралдар. Алмасудың барлық операциялары (циклдары) (жалаудан сұрау жүргізу әдісі немесе polling); - үзілістерді қолдану арқылы, ағымдағы орындалып келген бағдарламаны шұғыл қажет бағдарламаға процессорды мәжбүрлеп ауыстыру; - жадыға тура ену жолын пайдалану арқылы ауысуы. 11.4 МПЖ архитектурасы Осыған дейін біз тек микропроцессорлық жүйелердің тек бір типін, жалпы шиналы архитектурасын, мәліметтер мен командалар үшін ортақ бір шиналықты (бір шиналық, немесе пристондық, фон-неймандық архитектурасын) қарастырдық. Сәйкесінше бұл жағдайда жүйе құрамында мәліметтер үшін де, командалар үшін де ортақ тағы да бір жалпы жады болады (11.6 суретті қара). Бірақ бөлек шиналы мәліметтер архитектурасы мен командалар (екішиналық немесе гарвард архитектурасы) да болады. Бұл архитектура жүйеде мәліметтер үшін жеке жадының және командалар үшін жеке жадының болуын ұсынады (11.7 суретті қара). Осы екі типтің әрқайсысымен процессор ауысуы өз шинасы бойынша өтеді.  11.6 сурет - МПЖ фон-нейманды архитектурасы Жалпы шиналы архитектура көбірек таралған, ол мысалы дербес компьютерлерде және күрделі микрокомпьютерлерде қолданылады. Бөлек шиналы архитектура негізінен біркристалды микроконтроллерде қолданылады  11.7 сурет - МПЖ гарвардты архитектурасы Жалпы шинасы бар архитектура (притондық, фон-неймандық) қарапайымырақ, ол процессордан біруақытта екі шинаға қызмет көрсетуді, екі шина бойынша ауысуды бақылауды талап етпейді. Мәліметтер мен командалардың ортақ жадысының болуы оның көлемін мәліметтер коды мен командалар коды арасында ыңғайлы етіп бөлуге көмектеседі. 12 Дәріс. i8085 микропроцессоры 12.1 Жалпы мәліметтер Intel фирмасы ең бірінші МП процессорын, содан соң олардың жанұяларының қатарын құрастырды және қазіргі уақытта әртүрлі бағалаулар бойынша шығарылатын микропроцессорлардың жалпы көлемінің 85-92% өндіреді. Екі негізгі категорияларға RISC және CISC бөлінетін көптеген процессорлар архитектуралары бар. RISC - Reduced (Restricted) Instruction Set Computer – қысқартылған командалар жүйесі бар процессорлар. Бұл процессорлардың көбінесе әмбебап қолданыстағы біртекті регистрлер жиыны болады, сонымен қатар олардың саны көп болуы мүмкін. Командалар жүйесі салыстырмалы қарапайымдылығымен ерекшеленеді, қолданылу реті кодтары тіркелген ұзындығы бар нақты құрылымға ие. Нәтижесінде осындай архитектураны жүзеге асыру аздаған шығындар мен декодирлеуге және минималды шегінде осы инструкцияларды ең аз синхронизациялау тактілерінің саны бойынша орындауға мүмкіндік береді. CISC - Complete Instruction Set Computer - х86 жанұялары да жататын толық инструкциялар жиыны бар процессорлер (компьютерлер). Олардың регистрлерінің құрамы мен қызметі біртекті емес, командалардың кең жиыны инструкциялардың декодирленуін қиындатады, осыған байланысты аппараттық ресурстар шығындалады. Инструкцияларды орындауға арналаған тактілер саны артады. х86 процессорлары дүние жүзіндегі ең күрделі командаларға ие. х86 процессорлар жанұясындағы С486 бастап аралас архитектура қолданылады. CISC-процессоры RISC-ядросына ие. Есептеу процесін ұйымдастырудың келесі тәсілдерін бөлуге болады. - командалардың бір ағыны – мәліметтердің бір ағыны (Simple Instruction - Simple Data, SISD) – дәстүрлі фон-нейман архитектурасына сипатты (кейде Simple орнына Single жазылады); - командалардың бір ағыны – мәліметтердің көптік ағыны (Simple Instruction - Multiple Data, SIMD) – MMX технологиясы; - көп командалар ағыны – бір мәліметтер ағыны (Multiple Instruction - Simple Data, MISD); - командалардың көп ағыны – мәліметтердің көп ағыны (Multiple Instruction - Multiple Data, MIMD). Процессор микросхемасы міндетті түрде үш шиналар шығысына ие болады: адрес шинасы, мәліметтер шинасы және басқару шиналары. Кейде кейбір сигналдар және шиналар процессор микросхемалары шығысының азайту үшін мультиплексирленеді. Процессордың негізгі сипаттамалары – оның мәліметтер шинасының разрядтар саны, оның адрес шинасындағы разрядтар саны және басқару шинасындағы басқарылатын сигналдар саны. Адрес шинасының разрядтылығы жүйенің шекті қиындығын анықтайды. Басқару желісінің саны ауысу режимінің әртүрлілігін және жүйенің басқа құрылғылармен процессор ауысуының тиімділігін анықтайды. Негізгі үш шинаның сигналдары шығыстарынан басқа, процессор әрқашан сыртқы тактілік сигналды немесе кварцтік генераторды (CLK) қосу шығысына ие болады, яғни процессор тактілейтін құрылғы деген сөз. Процессордың тактілік жиілігі оның сыртқы емес, тек ішкі тез әсер етуін анықтайды. Әрбір процессорда болатын сигнал – бұл алғашқы ауытқу RESET сигналы. Қоректендіру қосылғанда, авариялық жағдайда немесе процессордың тоқтап қалуында сигналдың берілуі процессордың тоқтап қалуы осы сигналды беру процессор инициализациясына әкеледі, оны бастапқы қосылу бағдарламасын орындауға кірісуге мәжбүр етеді. Заманауи процессордың қоректену шинасы әдетте бір кернеуге (+5В немесе +3,3В) және ортақ сымға («жер») ие болады. Кейбір процессорларда төменгі энергия қоректендіру режимі қарастырылған. Процессорды магистралға қосу үшін буферлік микросхемалар қолданылатын болса, сигналдардың демультиплексирленуі және магистрал сигналдарының электрлік буферленуі қолданылады. Процессордың шина бойынша және жүйелік магистраль бойынша ауысу хаттамалары кейде өзара сәйкес келмейді, онда буферлік микросхемалар хаттамаларды бір-бірімен сәйкестендіреді. Кейде микропроцессорлық жүйеде бірнеше магистралдар (жүйелік және локальді) қолданылады, осы кезде магистралдың әрқайсысы үшінөзінің буферлік түйіні қолданылады. Мұндай құрылым мысалы, дербес компьютерлікке тән болып келеді. |