курс. курсач_борон_даня. Содержание х1Х0 13 Х3Х2 13 00 13 01 13

Скачать 1.9 Mb. Скачать 1.9 Mb.

|

|

СОДЕРЖАНИЕ Х1Х0 13 Х3Х2 13 00 13 01 13 11 13 10 13 00 13 1 13 1 13 1 13 1 13 01 14 1 14 1 14 1 14 11 14 1 14 1 14 1 14 1 14 10 14 1 14 1 14 1 14 МДНФ функции Y3: 14 Х1Х0 14 Х3Х2 14 00 14 01 14 11 14 10 14 00 14 01 14 0 14 11 14 10 14 0 14 МКНФ функции Y3: 14 14 МДНФ функции Y2: 15 Х1Х0 15 Х3Х2 15 00 15 01 15 11 15 10 15 00 15 0 15 01 15 0 15 0 15 11 15 0 15 0 15 10 15 0 15 МКНФ функции Y2: 15 Х1Х0 15 Х3Х2 15 00 15 01 15 11 15 10 15 00 15 01 16 1 16 1 16 11 16 1 16 1 16 1 16 1 16 10 16 1 16 1 16 МДНФ функции Y1: 16 Х1Х0 16 Х3Х2 16 00 16 01 16 11 16 10 16 00 16 0 16 0 16 0 16 0 16 01 16 0 16 0 16 11 16 10 16 0 16 0 16 МКНФ функции Y1: 16 Х1Х0 16 Х3Х2 16 00 16 01 16 11 16 10 16 00 16 1 16 1 16 01 16 1 16 11 17 10 17 1 17 1 17 1 17 МДНФ функции Y0: 17 Х1Х0 17 Х3Х2 17 00 17 01 17 11 17 10 17 00 17 0 17 0 17 01 17 0 17 0 17 0 17 11 17 0 17 0 17 0 17 0 17 10 17 0 17 МКНФ функции Y0: 17 ВВЕДЕНИЕ Программируемая логическая интегральная схема (ПЛИС) — электронный компонент (интегральная микросхема), используемый для создания конфигурируемых цифровых электронных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования). Для программирования используются программатор и IDE (отладочная среда), позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или программы на специальных языках описания аппаратуры: Verilog, VHDL, AHDL и др. ПЛИС широко применяются в разных устройствах: потребительской электронике, оборудовании телекома, платах-ускорителях для применения в дата-центрах, различной робототехнике, а также при прототипировании микросхем ASIC. В курсовой работе необходимо спроектировать модели комбинационной логической схемы, конечного автомата, а также работу семисегментного индикатора, многоканального генератора ШИМ-сигналов, разработать цифровой узел анализатора последовательности и смоделировать функциональный узел управления матричным дисплеем. Каждый компонент должен успешно пройти верификацию. 1 Проектирование моделей комбинационной логической схемы 1.1 Постановка задачи Спроектировать синтезируемые модели комбинационной схемы 4х4, описанной таблицей истинности согласно варианту задания, тремя различными способами: На вентильном уровне, методом карт Карно в виде МДНФ, в схемотехническом редакторе Schematic editor САПР Xilinx ISE Design Suite. На вентильном уровне, методом карт Карно в виде МКНФ, на языке описания аппаратуры Verilog. На поведенческом уровне, на языке описания аппаратуры Verilog. Реализовать на языке Verilog тестовое окружение и провести верификацию спроектированных моделей при помощи симулятора iSim из состава САПР Xilinx ISE Design Suite. Провести апробацию моделей при помощи отладочной платы Digilent Nexys 4 на ПЛИС Xilinx Artix 7 XC7A100T-1CSG324. Комбинации на входах комбинационных схем должны задаваться при помощи движковых переключателей отладочной платы, комбинации на выходах комбинационных схем должны отображаться светодиодами отладочной платы. Персональный вариант представлен в Таблице 1.1. Таблица 1.1 — Комбинация персонального варианта

1.2 Таблица истинности Заданная функция представлена в виде таблицы истинности в двоичной и шестнадцатеричной системах счисления (Таблица 1.2). Таблица 1.2 — Таблица истинности

1.3 Составление карт Карно с формулами МДНФ и МКНФ Удобство и наглядность такого представления логической функции обусловлено тем, что логические термы, к которым могут быть применены операции попарного неполного склеивания и элементарного поглощения, группируются в карте Карно в виде визуально очевидных прямоугольных массивов, содержащих в своих ячейках одинаковые значения (нули и единицы). С помощью карт Карно были составлены формулы минимальных дизъюнктивных и конъюнктивных нормальных форм (МКНФ и МДНФ) заданных функций (Таблицы 1.3 - 1.10). Таблица 1.3 — Карта Карно для МДНФ функции Y3

МДНФ функции Y3:   Таблица 1.4 — Карта Карно для МКНФ функции Y3

МКНФ функции Y3:  Таблица 1.5 — Карта Карно для МДНФ функции Y2

МДНФ функции Y2:  Таблица 1.6 — Карта Карно для МКНФ функции Y2

МКНФ функции Y2:  ( ( Таблица 1.7 — Карта Карно для МДНФ функции Y1

МДНФ функции Y1:  Таблица 1.8 — Карта Карно для МКНФ функции Y1

МКНФ функции Y1:  ( ( Таблица 1.9 — Карта Карно для МДНФ функции Y0

МДНФ функции Y0:  Таблица 1.10 — Карта Карно для МКНФ функции Y0

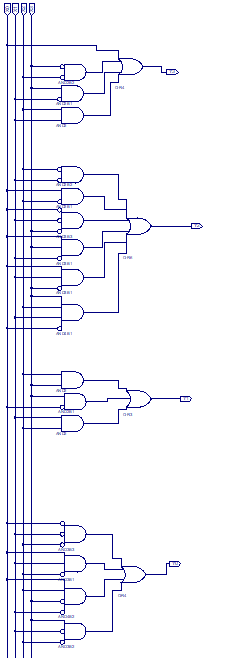

МКНФ функции Y0:  1.4 Описание модулей Для построения схемы на вентильном уровне в схемотехническом редакторе были расставлены и соединены вентили И, ИЛИ в соответствии с составленными функциями МДНФ (Рисунок 1.1).  | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Х1Х0

Х1Х0 1

1 1

1

1

1 Х1Х0

Х1Х0 0

0 0

0 Х1Х0

Х1Х0 00

00 01

01 11

11 1

1

1

1 1

1

0

0

0

0

1

1 1

1 1

1 Х1Х0

Х1Х0 11

11 0

0

0

0 01

01 11

11 1

1

1

1 Х1Х0

Х1Х0 0

0

0

0 0

0 0

0