|

|

курс. курсач_борон_даня. Содержание х1Х0 13 Х3Х2 13 00 13 01 13

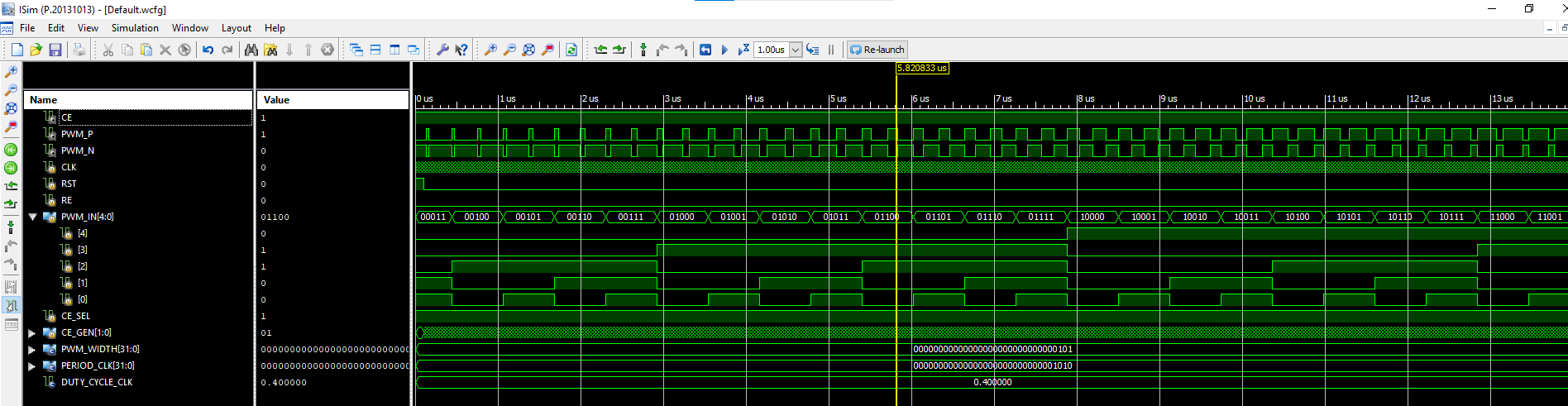

5.4 Тестовое окружение и результат верификации

После написания всех этих модулей, оставалось только реализовать тестовое окружение, которое позволило бы провести верификацию и подтвердило бы правильность реализации всех модулей и логического устройства в целом. Код тестового модуля представлен в Листинге 5.4.

Листинг 5.4 — Тестовый модуль (TEST_PWM_FSM.v)

module TEST_PWM_FSM;

parameter PWM_WIDTH = 5;

// System Inputs:

reg CLK;

reg RST;

// Inputs:

reg RE;

wire CE;

reg [PWM_WIDTH-1:0] PWM_IN;

// Outputs:

wire PWM_P;

wire PWM_N;

// CE Mode Select:

reg CE_SEL;

//----------------------------------------—

// Clock Generator - 100 MHz

parameter PERIOD_CLK = 10; // 10ns

parameter DUTY_CYCLE_CLK = 0.4;

initial

forever

begin

CLK = 1'b0;

#(PERIOD_CLK-(PERIOD_CLK*DUTY_CYCLE_CLK)) CLK = 1'b1;

#(PERIOD_CLK*DUTY_CYCLE_CLK);

end

//----------------------------------------—

// Init. Reset startup pulse (100ns POR)

initial

begin

RST = 1;

#100;

@(posedge CLK);

#(PERIOD_CLK*0.2);

RST = 0;

end

//----------------------------------------—

// Instantiate the Unit Under Test (UUT)

PWM_FSM #(.UDW(PWM_WIDTH)) uut (

.CLK(CLK),

.RST(RST),

.RE(RE),

.CE(CE),

.PWM_IN(PWM_IN),

.PWM_P(PWM_P),

.PWM_N(PWM_N)

);

//----------------------------------------—

// 3T Clock Enable Generator:

reg [1:0] CE_GEN;

always @ (posedge CLK, posedge RST)

if(RST)

CE_GEN <= 2'b00;

else

Продолжение Листинга 5.4

if(CE_GEN == 2'b10) CE_GEN <= 2'b00;

else CE_GEN <= CE_GEN + 1;

or (CE, CE_GEN[1], CE_SEL);

//----------------------------------------—

initial begin

// Initialize Inputs

RE = 0;

CE_SEL = 1;

PWM_IN = 3;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 4

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 5

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 6

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 7

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 8

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 9

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 10

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 11

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 12

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 13

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 14

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 15

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 16

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 17

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 18

@(posedge PWM_P);

Продолжение Листинга 5.4

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 19

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 20

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 21

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 22

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 23

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 24

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 25

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 26

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 27

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 28

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 29

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 30

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 31

#(PERIOD_CLK*100);

PWM_IN = 0;

#(PERIOD_CLK*100);

PWM_IN = PWM_IN + 1; // 1

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 2

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 3

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 4

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = {PWM_WIDTH{1'bX}};

Продолжение Листинга 5.4

PWM_IN = {PWM_WIDTH{1'bX}};

#(PERIOD_CLK*91.2);

PWM_IN = 3; // 3

#(PERIOD_CLK);

PWM_IN = {PWM_WIDTH{1'bX}};

CE_SEL = 0;

@(posedge PWM_P);

#(PERIOD_CLK*60*3);

#(PERIOD_CLK*2.2);

PWM_IN = 3; // 3

#(PERIOD_CLK);

PWM_IN = {PWM_WIDTH{1'bX}};

@(posedge PWM_P);

#(PERIOD_CLK*60*3);

#(PERIOD_CLK*2.2);

PWM_IN = 1; // 1

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 2

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 3

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 4

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 5

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 6

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 7

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 8

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 9

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 10

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 11

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 12

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 13

Продолжение Листинга 5.4

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 14

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 15

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 16

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 17

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 18

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 19

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 20

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 21

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 22

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 23

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 24

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 25

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 26

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 27

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 28

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 29

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 30

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 31

#(PERIOD_CLK*300);

PWM_IN = 0;

#(PERIOD_CLK*300);

PWM_IN = PWM_IN + 1; // 1

@(posedge PWM_P);

@(posedge PWM_P);

Продолжение Листинга 5.4

PWM_IN = PWM_IN + 1; // 2

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 3

@(posedge PWM_P);

@(posedge PWM_P);

PWM_IN = PWM_IN + 1; // 4

@(posedge PWM_P);

@(posedge PWM_P);

#(PERIOD_CLK*5.2);

RE = 1;

#(PERIOD_CLK);

RE = 0;

#(PERIOD_CLK*16);

RE = 1;

#(PERIOD_CLK);

RE = 0;

#(PERIOD_CLK*55);

RE = 1;

#(PERIOD_CLK);

RE = 0;

#(PERIOD_CLK*200);

RE = 1;

#(PERIOD_CLK*300);

$stop;

end

endmodule

Для верификации была сгенерирована временная диаграмма, представленная на Рисунке 5.10. При правильной работе, значения в разделе “line[7:0]” должны совпадать с персональным вариантом, представленным в Таблице 1.1. Помимо этого, число тактов активности сигналов “LED” также должно совпадать с персональным вариантом. Из вида временной диаграммы был сделан вывод о том, что все модули и логическое устройство в целом правильно спроектированы и реализованы.

Рисунок 5.2 – Временная диаграмма работы модуля

5.5 Вывод

В ходе работы был разработан универсальный модуль ШИМ-генератора, который управляет LED-светодиодами. В результате тестирования временная диаграмма показала корректную работу модуля. Также было изучено, как работает ШИМ-генератор и было освоено описание параметрических моделей.

ЗАКЛЮЧЕНИЕ

В результате выполнения курсовой работы были освоены основные принципы разработки на ПЛИС в инструментальной среде разработки программ ISE 14.7, а также проведено успешное тестирование составляющих модулей.

При решении задач были применены прикладные системы программирования, а также необходимые методы для их реализации.

В первом задании курсовой работы были спроектированы синтезируемые модели комбинационной схемы 4х4, описанной таблицей истинности согласно варианту задания, тремя различными способами:

1. На вентильном уровне, методом карт Карно в виде МДНФ, в схемотехническом редакторе Schematic editor САПР Xilinx ISE Design Suite.

2. На вентильном уровне, методом карт Карно в виде МКНФ, на языке описания аппаратуры Verilog.

3. На поведенческом уровне, на языке описания аппаратуры Verilog.

Условием второго задания курсовой работы было описать конечный автомат, представляющий собой генератор фиксированной последовательности логических сигналов, в виде синтезируемой модели на языке Verilog HDL.

В третьем задании курсовой работы требовалось разработать цифровой узел на основе отладочной платы Digilent Nexys 4, представляющий собой анализатор фиксированной последовательности логических сигналов. Узел обеспечивает индикацию ожидаемых и вводимых элементов последовательности, посредством входящих в состав отладочной платы семисегментных индикаторов, согласно данному заданию. Узел реализован в виде синтезируемой модели на языке Verilog HDL

Темой четвертого задания курсовой работы была реализация в объёме ПЛИС Spartan-3E XC3S500E4PQ208C модель логического устройства, сочетающая в себе функциональные узлы делителя частоты 1кГц, фильтр дребезга контактов кнопки и конечного автомата генератора последовательности, реализованной во втором задании. При этом все модули проекта описаны с помощью языка Verilog.

В заключительном задании курсовой работы требовалась реализация в объёме ПЛИС Spartan-3E XC3S500E4PQ208C модель логического устройства, сочетающая в себе функциональные узлы делителя частоты 1кГц, фильтр дребезга контактов кнопок и схемы динамической индикации, реализованных в предыдущих заданиях, с новыми узлами генераторов широтно-импульсных сигналов. При этом все модули проекта были описаны с помощью языка Verilog.

Таким образом, были изучены и реализованы: работа конечного автомата, универсального модуля ШИМ-генератора, матричного и семисегментного индикатора. Также для всех этих моделей было реализовано тестовое окружение на языке Verilog и успешно проведена верификация при помощи симулятора iSim из состава САПР Xilinx ISE Design Suite. Симуляция показала успешную работу спроектированных моделей.

.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

Харрис Д.М., Харрис С.Л. Цифровая схемотехника и архитектура компьютера. – М.: ДМК Пресс, 2018. – 792 с.

Цифровой синтез: практический курс / под ред. А.Ю. Романова, Ю.В. Панчула. – М.: ДМК Пресс, 2020. – 556 с.

Соловьев В.В. Основы языка проектирования цифровой аппаратуры Verilog. – М.: Горячая линия – Телеком, 2015. – 206 с.

Соловьев В.В. Логическое проектирование встраиваемых систем на FPGA. – СПб.: ООО «Медиа Группа Файнстрит», 2021. – 222 с.

Угрюмов Е.П. Цифровая схемотехника: Учеб. пособие для вузов. – 2-е изд., перераб. и доп. – СПб.: БХВ-Петербург, 2007. – 800 с.

Зайцев Е.И., Прикладная теория цифровых автоматов : учебное пособие / Е. И. Зайцев, В. В. Макаров. — М.: МИРЭА, 2018. — 112 с.. — Библиогр.: с. 111 (7 назв.), НТБ МИРЭА З-17.

ISE Tutorial [Электронный ресурс]/ Режим доступа: https://my.ece.utah.edu/

kalla/ECE3700/ISE_Tutorial_Nexys3_14.7_Pay mon_with_W10_installation_notes_utkarsh.pdf. — 33 с.

|

|

|

Скачать 1.9 Mb.

Скачать 1.9 Mb.