|

|

курс. курсач_борон_даня. Содержание х1Х0 13 Х3Х2 13 00 13 01 13

3.4 Тестовое окружение и результат верификации

Последним шагом оставалось реализовать модуль тестового окружения, который позволил бы провести верификацию проделанной работы. Данный модуль представлен в Листинге 3.6.

Листинг 3.6 — Модуль тестового окружения (TEST.v)

module TEST;

reg CLK;

reg CPU_RST;

reg BTN_C;

reg CE;

reg [3:0] SW;

wire [7:0] CAT;

wire [7:0] AN;

wire [3:0] HEX_CAT;

wire [3:0] HEX_AN;

top2 uut(

.CLK(CLK),

.CPU_RST(CPU_RST),

.BTN_C(BTN_C),

.SW(SW),

.line_CE(CE),

.CAT(CAT),

.AN(AN),

.HEX_CAT(HEX_CAT),

.HEX_AN(HEX_AN)

);

initial begin

CLK = 0;

CPU_RST = 1;

BTN_C = 1;

SW = 4'h6;

#10;

BTN_C = 0;

#710;

Продолжение Листинга 3.6

CPU_RST = 0;

BTN_C = 0;

#80;

CPU_RST = 1;

#10;

BTN_C = 1;

SW = 4'h1;

#10;

BTN_C = 0;

#700;

BTN_C = 1;

SW = 4'h4;

#10;

BTN_C = 0;

#710;

BTN_C = 1;

SW = 4'h7;

#10;

BTN_C = 0;

#710;

BTN_C = 1;

SW = 4'h1;

#10;

BTN_C = 0;

#710;

BTN_C = 1;

SW = 4'h6;

#10;

BTN_C = 0;

#710;

BTN_C = 1;

SW = 4'h2;

#10;

BTN_C = 0;

#710;

BTN_C = 1;

SW = 4'h3;

#10;

BTN_C = 0;

#710;

BTN_C = 1;

SW = 4'hB;

#10;

BTN_C = 0;

#710;

end

always begin

#5;

CLK <=

CLK;

end

always begin

CE <= 0;

#80;

CE <= 1;

#10;

end

endmodule

Для верификации результатов нужно было сгенерировать временную диаграмму и сравнить ожидаемые значения с действительностью. Значения в строке “SEG[31:0]” должны совпадать со значениями персонального варианта, представленного в Таблице 1.1.

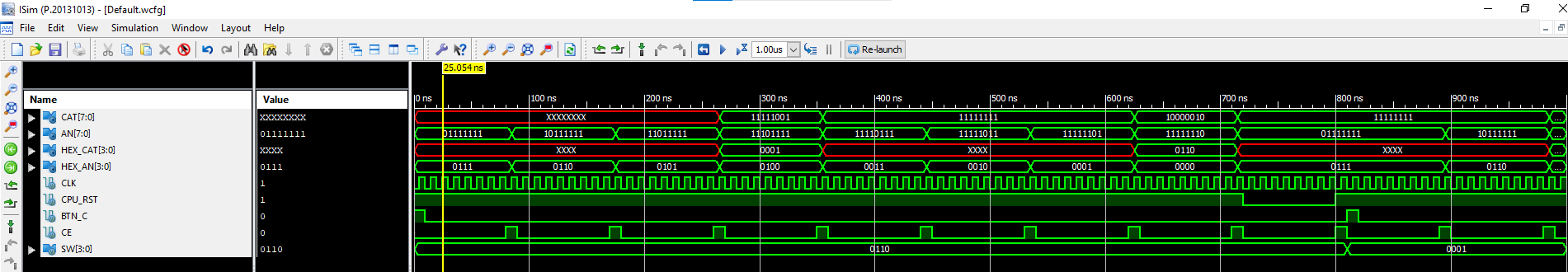

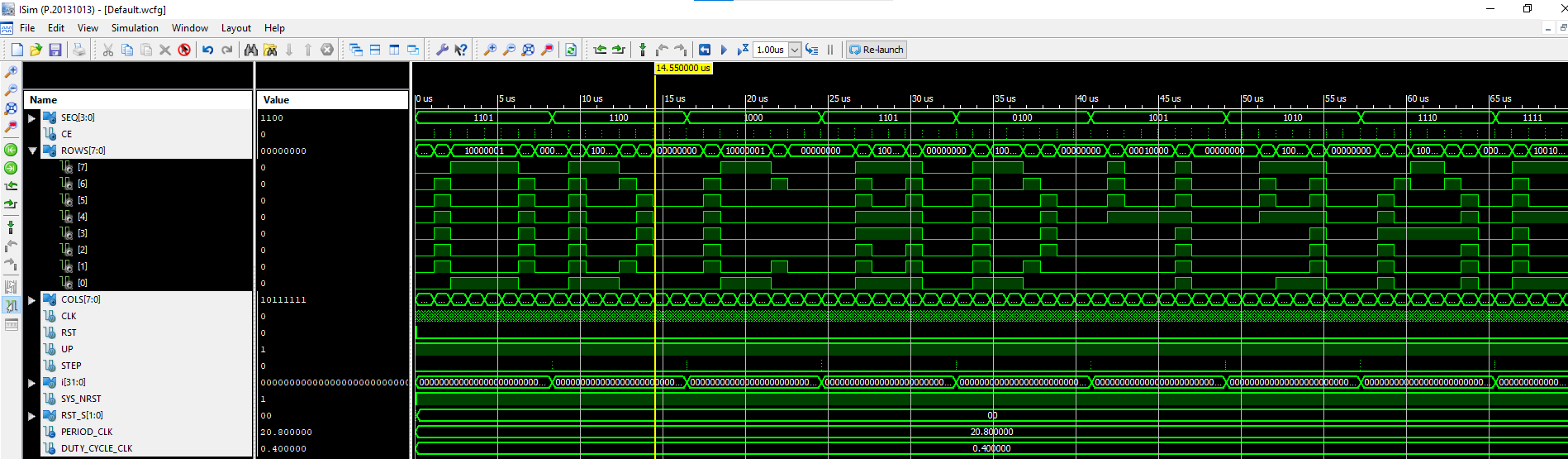

На временной диаграмме (Рис. 3.5) виден результат верификации в виде симуляции. Выходные значения совпадают и соответствуют таблице переходов. Следовательно, автомат спроектирован верно.

Рисунок 3.5 - Результат верификации

3.5 Вывод

В ходе работы был спроектирован конечный автомат, представляющий собой анализатор фиксированной последовательности логических сигналов, в виде синтезируемой модели на языке Verilog HDL. Также было реализовано на языке Verilog тестовое окружение и успешно проведена верификация спроектированной модели при помощи симулятора iSim из состава САПР Xilinx ISE Design Suite.

4 Моделирование функционального узла управления матричным дисплеем

4.1 Постановка задачи

В работе требуется реализовать в объёме ПЛИС Spartan-3E XC3S500E4PQ208C модель логического устройства, сочетающую в себе функциональные узлы делителя частоты 1кГц, фильтра дребезга контактов кнопки и конечного автомата генератора последовательности, реализованных во второй работе. При этом все модули проекта должны быть описаны с помощью языка Verilog.

Помимо синтезируемых модулей, реализуемых в базисе элементов ПЛИС, в проекте следует разработать тестовый модуль, также написанный на языке Verilog, предназначенный для верификации.

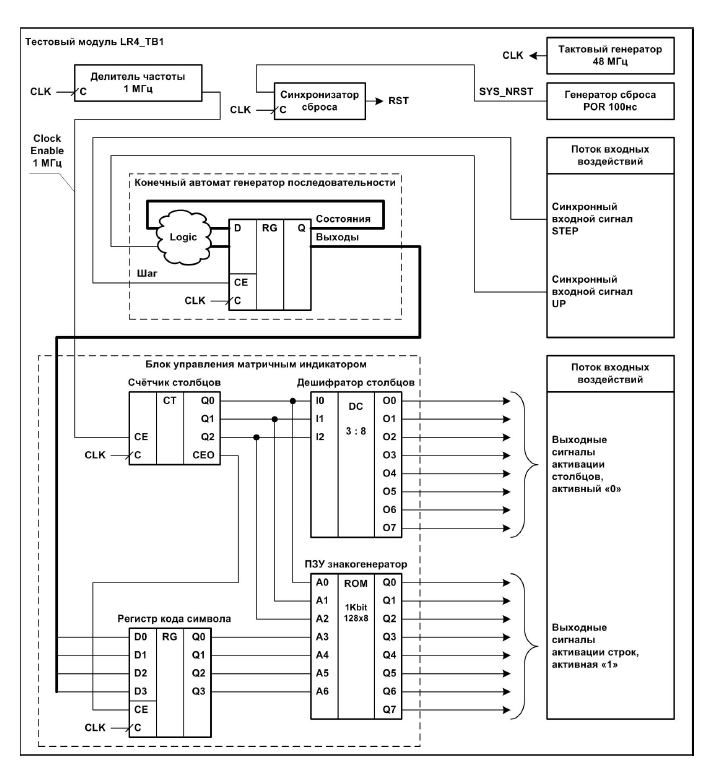

В объёме тестового модуля по иерархии в качестве составных блоков подключаются тестируемые блоки. В нашем случае в роли тестируемых блоков выступают модули управления матричным индикатором и автомат генератора заданной последовательности символов (из второй лабораторной работы).

Для эмуляции работы синхронных цифровых устройств в составе тестового модуля описываются генератор синхросигнала CLK и генератор сигнала сброса в исходное состояние RST. Эти блоки в общем случае не предназначены для реализации в базисе ПЛИС и могут быть описаны не синтезируемыми конструкциями языка Verilog.

Основные тестовые воздействия, подаваемые на тестируемый блок, в различные моменты времени, описываются в потоке тестовых воздействий (стимулов), и включают синхронные управляющие сигналы UP и STEP.

4.2 Описание структурных схем

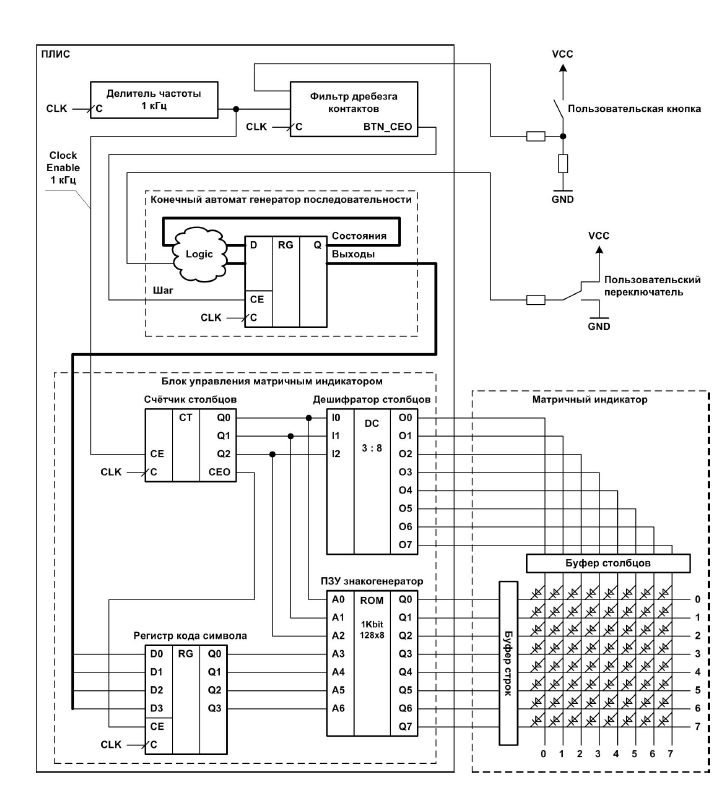

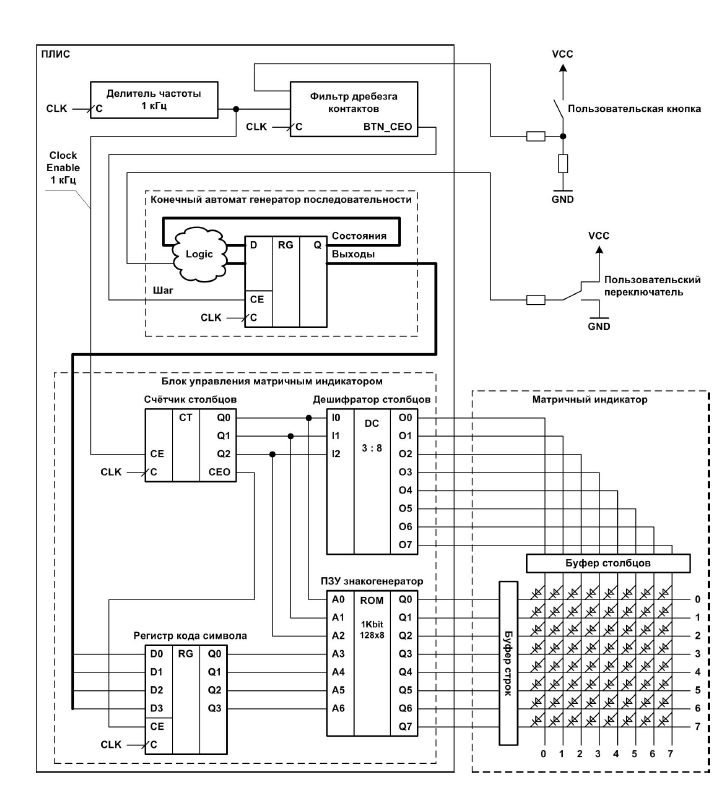

Реализуемое в ПЛИС устройство имеет структурную схему, представленную на Рисунке 4.1. В нем представлена структурная схема модуля, в которой следующие модули:

Конечный автомат, который генерирует последовательность символов, согласно варианту, представленному в Таблице 4.1.

Блок управления матричным индикатором – выводит последовательность символов на матричный индикатор, которую генерирует конечный автомат.

Фильтр дребезга контактов кнопки

Делитель частоты

Рисунок 4.1 – Структурная схема верхнего модуля иерархии проекта

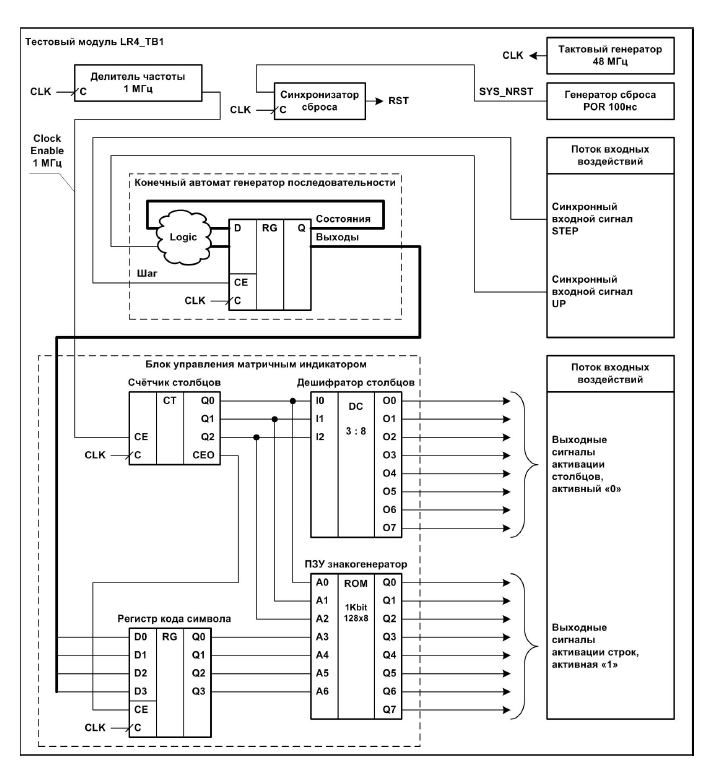

Как видно из Рисунка 4.2, тестовое окружение моделирует работу части устройства на частоте 1 МГц, в 1000 раз выше реальной частоты работы матричного индикатора. Функциональные узлы делителя частоты и фильтра в тестировании не задействованы и считаются отлаженными ранее.

Рисунок 4.2 – Организация тестового модуля

Входные и выходные значения аналогичны персональному варианту и представлены в Таблице 1.1.

Далее описан принцип работы матричного индикатора.

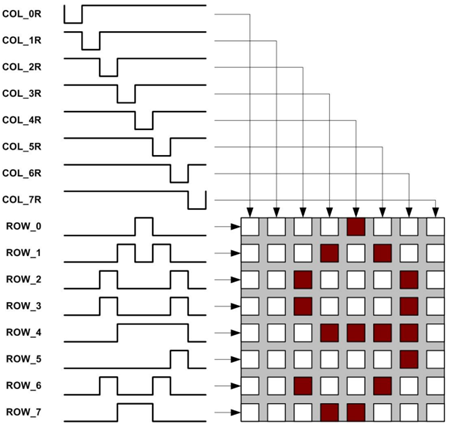

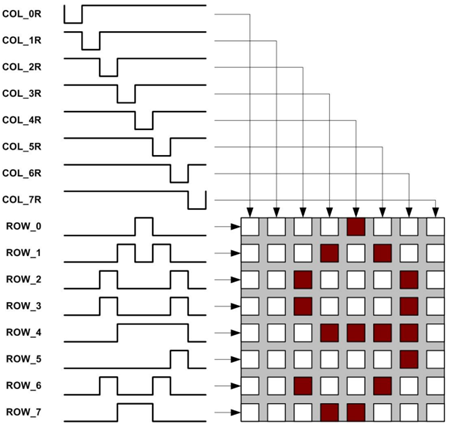

Вывод в данном примере осуществляется не по строкам, а по столбцам. Это значит, что в определённый момент времени активным является столбец, и любые из восьми светодиодов активного столбца могут подсвечиваться одновременно. Это даёт возможность увидеть одноцветное изображение, выводимое на матричный дисплей, непосредственно на временной диаграмме. Принцип вывода информации на матричный индикатор на примере символа «9» показан на Рисунке 4.3.

Рисунок 4.3 — Вывод символа на матричный индикатор

В работе следовало предусмотреть возможность вывода на индикатор символов шестнадцатиричных цифр от 0 до F.

Формирование символа из 4-разрядного двоичного кода осуществляет знакогенератор. Это постоянное запоминающее устройство (ПЗУ), хранящее шаблоны всех символов. Размер шаблона соответствует размерности матричного индикатора – 8х8 точек, 64 бита. Число шаблонов определяется числом символов и равно 16. Итого объём ПЗУ знакогенератора составляет 1 кбит или 128 байт.

Младшие три разряда адреса ПЗУ выбирают текущий столбец в рамках одного шаблона. Старшие четыре разряда адреса ПЗУ выбирают текущий шаблон.

4.3 Содержание модулей

В общем счёте, для реализации данного проекта требовались шесть модулей, а именно: делитель частоты, фильтр дребезга контактов, генератор последовательности, модуль управления матричным индикатором, модуль верхнего уровня и тестовое окружение.

Первые три модуля уже были разработаны ранее. Их описание приведено в разделе 2, а код представлен в Листингах 2.3, 2.2 и 2.1 соответственно.

В Листинге 4.1 представлен код модуля верхнего уровня иерархии проекта, описанный на языке Verilog. Он объединяет все используемые модули.

Листинг 4.1 — Модуль верхнего уровня иерархии проекта (LR4_TOP.v)

module LR4_TOP(

input CLK,

input BTN_RST,

input SW,

input BTN_C,

output [7:0] ROWS,

output [7:0] COLS

);

reg RST_I;

always @(posedge CLK, negedge BTN_RST)

begin

if(

BTN_RST)

RST_I <= 1'b1;

else

RST_I <= 1'b0;

end

wire CE;

wire BTN_C_CE;

wire [3:0]SEQ;

LR2_CLK_DIV CLK_DIV (

.CLK(CLK),

.RST(RST_I),

.CEO_DIV(CE));

LR2_BTN_FLTR FLTR (

.CLK(CLK),

.RST(RST_I),

.CE(CE),

.BTN_IN(BTN_C),

.BTN_OUT(),

.BTN_CEO(BTN_C_CE));

LR2_V VARIANT (

.CLK(CLK),

.RST(RST_I),

.CE(BTN_C_CE),

.UP(SW),

.SEQ(SEQ));

Продолжение Листинга 4.1

MATRIXXX MATRIXXX(

.CLK(CLK),

.RST(RST_I),

.CE(CE),

.SEQ(SEQ),

.ROWS(ROWS),

.COLS(COLS));

endmodule

В Листинге 4.2 представлен код модуля конечного автомата, в котором, исходя из Таблицы 1.1 задана последовательность индивидуального варианта.

Листинг 4.2 — Модуль конечного автомата (LR2_V.v)

module LR2_V(

input CLK,

input RST,

input CE,

input UP,

output reg [3:0] SEQ

);

reg [3:0] CNT;

always@(CNT)

case(CNT)

4'h0: SEQ <= 4'hD;

4'h1: SEQ <= 4'hC;

4'h2: SEQ <= 4'h8;

4'h3: SEQ <= 4'hD;

4'h4: SEQ <= 4'h4;

4'h5: SEQ <= 4'h9;

4'h6: SEQ <= 4'hA;

4'h7: SEQ <= 4'hE;

4'h8: SEQ <= 4'hF;

4'h9: SEQ <= 4'hD;

4'hA: SEQ <= 4'h2;

4'hB: SEQ <= 4'hD;

4'hC: SEQ <= 4'hA;

4'hD: SEQ <= 4'hE;

4'hE: SEQ <= 4'hE;

4'hF: SEQ <= 4'hA;

default: SEQ <= 4'h0;

endcase

always@(posedge CLK, posedge RST)

if (RST)

CNT <= 4'h0;

else if (CE)

if (UP)

CNT<=(CNT + 1);

else

CNT <= (CNT - 1);

else SEQ <= SEQ;

endmodule

В Листинге 4.3 представлен код модуля управления матричным индикатором, для которого требовалось разработать обработчики сигналов строк и столбцов. В целом, логика их работы схожа с логикой обработчиков сигналов катодов и анодов. Для их работы также требуется счётчик

Листинг 4.3 — Модуль управления матричным индикатором (MATRIXXX.v)

module MATRIXXX(

input CLK,

input RST,

input CE,

input [3:0] SEQ,

output reg [7:0] ROWS,

output reg [7:0] COLS

);

reg [2:0]CT_CO; // Счетчик столбцов

always @(posedge CLK, posedge RST)

begin

if(RST) begin

CT_CO <= 0;

end

else

if(CE) begin

CT_CO <= CT_CO + 1'b1;

end

end

wire CEO; // Разрешение смены символа

assign CEO = &CT_CO;

// Дешифратор столбцов

always @*

case(CT_CO)

3'd0: COLS <= 8'b11111110;

3'd1: COLS <= 8'b11111101;

3'd2: COLS <= 8'b11111011;

3'd3: COLS <= 8'b11110111;

3'd4: COLS <= 8'b11101111;

3'd5: COLS <= 8'b11011111;

3'd6: COLS <= 8'b10111111;

default: COLS <= 8'b01111111;

endcase

reg [3:0] SEQ_CODE; // Регистр кода символа

always @(posedge CLK, posedge RST)

//SEQ_CODE <= SEQ;

if (RST)

SEQ_CODE <= 4'h0;

else if (CT_CO == 4'h7)

SEQ_CODE <= SEQ;

// ПЗУ знакогенератор

always @* begin

case({SEQ_CODE, CT_CO})

//__Symbol__'0'

7'h00: ROWS <= 8'b00000000;

7'h01: ROWS <= 8'b01111110;

7'h02: ROWS <= 8'b10000001;

Продолжение Листинга 4.3

7'h03: ROWS <= 8'b10000001;

7'h04: ROWS <= 8'b10000001;

7'h05: ROWS <= 8'b10000001;

7'h06: ROWS <= 8'b01111110;

7'h07: ROWS <= 8'b00000000;

//__Symbol__'1'

7'h08: ROWS <= 8'b00000000;

7'h09: ROWS <= 8'b00000000;

7'h0a: ROWS <= 8'b00010000;

7'h0b: ROWS <= 8'b00100000;

7'h0c: ROWS <= 8'b01000001;

7'h0d: ROWS <= 8'b11111111;

7'h0e: ROWS <= 8'b00000001;

7'h0f: ROWS <= 8'b00000000;

//__Symbol__'2'

7'h10: ROWS <= 8'b00000000;

7'h11: ROWS <= 8'b00000000;

7'h12: ROWS <= 8'b10011111;

7'h13: ROWS <= 8'b10010001;

7'h14: ROWS <= 8'b10010001;

7'h15: ROWS <= 8'b11110001;

7'h16: ROWS <= 8'b00000000;

7'h17: ROWS <= 8'b00000000;

//__Symbol__'3'

7'h18: ROWS <= 8'b00000000;

7'h19: ROWS <= 8'b00000000;

7'h1a: ROWS <= 8'b10010001;

7'h1b: ROWS <= 8'b10010001;

7'h1c: ROWS <= 8'b10010001;

7'h1d: ROWS <= 8'b11111111;

7'h1e: ROWS <= 8'b00000000;

7'h1f: ROWS <= 8'b00000000;

//__Symbol__'4'

7'h20: ROWS <= 8'b00000000;

7'h21: ROWS <= 8'b11110000;

7'h22: ROWS <= 8'b00010000;

7'h23: ROWS <= 8'b00010000;

7'h24: ROWS <= 8'b00010000;

7'h25: ROWS <= 8'b11111111;

7'h26: ROWS <= 8'b00000000;

7'h27: ROWS <= 8'b00000000;

//__Symbol__'5'

7'h28: ROWS <= 8'b00000000;

7'h29: ROWS <= 8'b00000000;

7'h2a: ROWS <= 8'b11110001;

7'h2b: ROWS <= 8'b10010001;

7'h2c: ROWS <= 8'b10010001;

7'h2d: ROWS <= 8'b10011111;

7'h2e: ROWS <= 8'b00000000;

7'h2f: ROWS <= 8'b00000000;

//__Symbol__'6'

7'h30: ROWS <= 8'b00000000;

7'h31: ROWS <= 8'b00000000;

7'h32: ROWS <= 8'b11111111;

7'h33: ROWS <= 8'b10010001;

7'h34: ROWS <= 8'b10010001;

Продолжение Листинга 4.3

7'h35: ROWS <= 8'b10011111;

7'h36: ROWS <= 8'b00000000;

7'h37: ROWS <= 8'b00000000;

//__Symbol__'7'

7'h38: ROWS <= 8'b00000000;

7'h39: ROWS <= 8'b10000000;

7'h3a: ROWS <= 8'b10000000;

7'h3b: ROWS <= 8'b10000000;

7'h3c: ROWS <= 8'b10000000;

7'h3d: ROWS <= 8'b11111111;

7'h3e: ROWS <= 8'b00000000;

7'h3f: ROWS <= 8'b00000000;

//__Symbol__'8'

7'h40: ROWS <= 8'b00000000;

7'h41: ROWS <= 8'b00000000;

7'h42: ROWS <= 8'b11111111;

7'h43: ROWS <= 8'b10011001;

7'h44: ROWS <= 8'b10011001;

7'h45: ROWS <= 8'b11111111;

7'h46: ROWS <= 8'b00000000;

7'h47: ROWS <= 8'b00000000;

//__Symbol__'9'

7'h48: ROWS <= 8'b00000000;

7'h49: ROWS <= 8'b00000000;

7'h4a: ROWS <= 8'b11110000;

7'h4b: ROWS <= 8'b10010001;

7'h4c: ROWS <= 8'b10010001;

7'h4d: ROWS <= 8'b11111111;

7'h4e: ROWS <= 8'b00000000;

7'h4f: ROWS <= 8'b00000000;

//__Symbol__'A'

7'h50: ROWS <= 8'b00000000;

7'h51: ROWS <= 8'b00111111;

7'h52: ROWS <= 8'b01001000;

7'h53: ROWS <= 8'b10001000;

7'h54: ROWS <= 8'b10001000;

7'h55: ROWS <= 8'b01001000;

7'h56: ROWS <= 8'b00111111;

7'h57: ROWS <= 8'b00000000;

//__Symbol__'B'

7'h58: ROWS <= 8'b00000000;

7'h59: ROWS <= 8'b11111111;

7'h5a: ROWS <= 8'b10010001;

7'h5b: ROWS <= 8'b10010001;

7'h5c: ROWS <= 8'b01101110;

7'h5d: ROWS <= 8'b00000000;

7'h5e: ROWS <= 8'b00000000;

7'h5f: ROWS <= 8'b00000000;

//__Symbol__'c'

7'h60: ROWS <= 8'b00000000;

7'h61: ROWS <= 8'b01111110;

7'h62: ROWS <= 8'b10000001;

7'h63: ROWS <= 8'b10000001;

7'h64: ROWS <= 8'b10000001;

7'h65: ROWS <= 8'b01000010;

7'h66: ROWS <= 8'b00000000;

Продолжение Листинга 4.3

7'h67: ROWS <= 8'b00000000;

//__Symbol__'D'

7'h68: ROWS <= 8'b00000000;

7'h69: ROWS <= 8'b11111111;

7'h6a: ROWS <= 8'b10000001;

7'h6b: ROWS <= 8'b10000001;

7'h6c: ROWS <= 8'b01000010;

7'h6d: ROWS <= 8'b00111100;

7'h6e: ROWS <= 8'b00000000;

7'h6f: ROWS <= 8'b00000000;

//__Symbol__'e'

7'h70: ROWS <= 8'b00000000;

7'h71: ROWS <= 8'b11111111;

7'h72: ROWS <= 8'b10010001;

7'h73: ROWS <= 8'b10010001;

7'h74: ROWS <= 8'b10010001;

7'h75: ROWS <= 8'b10010001;

7'h76: ROWS <= 8'b00000000;

7'h77: ROWS <= 8'b00000000;

//__Symbol__'F'

7'h78: ROWS <= 8'b00000000;

7'h79: ROWS <= 8'b11111111;

7'h7a: ROWS <= 8'b10010000;

7'h7b: ROWS <= 8'b10010000;

7'h7c: ROWS <= 8'b10010000;

7'h7d: ROWS <= 8'b10010000;

7'h7e: ROWS <= 8'b00000000;

default: ROWS <= 8'b00000000;

endcase

end

endmodule

4.4 Тестовое окружение и результат верификации

Код тестового модуля, описанный на языке Verilog, позволяет сгенерировать временную диаграмму и провести верификацию проекта. Сам модуль тестового окружения представлен в Листинге 4.4.

Листинг 4.4 — Тестовый модуль (MATest.v)

module MATest;

// Inputs

reg CLK;

reg RST;

reg UP;

reg STEP;

// Outputs

wire [3:0] SEQ;

wire CE;

Продолжение Листинга 4.4

wire [7:0] ROWS;

wire [7:0] COLS;

integer i;

// Instantiate the Unit Under Test (UUT)

LR2_V uut (

.CLK(CLK),

.RST(RST),

.CE(STEP),

.UP(UP),

.SEQ(SEQ)

);

LR2_CLK_DIV #(

.CNT_WDT(6),

.DIVDIV(48))

DIV_1KHZ(

.CLK(CLK),

.RST(RST),

.CEO_DIV(CE));

MATRIXXX MATRIXXX(

.CLK(CLK),

.RST(RST),

.CE(CE),

.SEQ(SEQ),

.ROWS(ROWS),

.COLS(COLS));

// Clock Generator - 48 MHz

parameter PERIOD_CLK = 20.8;

parameter DUTY_CYCLE_CLK = 0.4;

initial

forever

begin

CLK = 1'b0;

#(PERIOD_CLK-(PERIOD_CLK*DUTY_CYCLE_CLK)) CLK = 1'b1;

#(PERIOD_CLK*DUTY_CYCLE_CLK);

end

//Генератор сигнала сброса

reg SYS_NRST;

initial

begin

SYS_NRST = 1'b0;

#100;

SYS_NRST = 1'b1;

end

//cинхронизатор сброса ТРИГГЕРОВ

reg [1:0] RST_S;

always @(posedge CLK, negedge SYS_NRST)

if(!SYS_NRST) RST_S <= 2'b11;

else RST_S <= {RST_S[0], 1'b0};

always @* RST <= RST_S[1];

initial begin

STEP = 1'b0;

Продолжение Листинга 4.4

UP = 1'b1;

for(i = 0; i < 15; i = i + 1'b1) begin

@(negedge COLS[7]);

@(posedge CE);

@(posedge CLK)

#(PERIOD_CLK*0.2);

STEP = 1'b1;

#(PERIOD_CLK);

STEP = 1'b0;

end

UP = 1'b0;

#100;

for(i = 0; i < 15; i = i + 1'b1) begin

@(negedge COLS[7]);

@(posedge CE);

@(posedge CLK)

#(PERIOD_CLK*0.2);

STEP = 1'b1;

#(PERIOD_CLK);

STEP = 1'b0;

end

end

endmodule

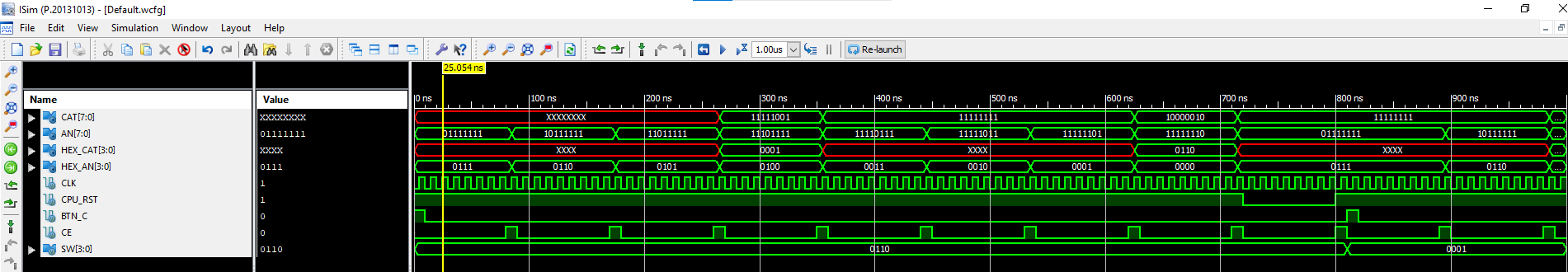

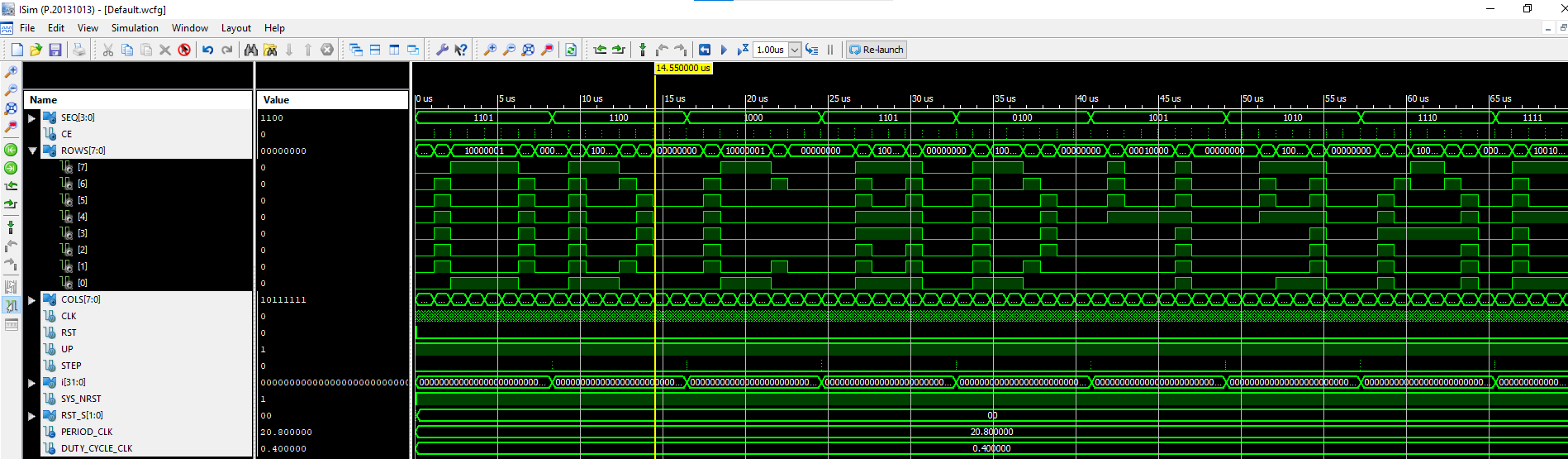

Провести верификацию данной работы было достаточно просто, так как нужно было только сгенерировать временную диаграмму и сравнить изображения символов с персональным вариантом, предста вленным в Таблице 1.1. Временная диаграмма изображена на Рисунке 4.4. Исходя из вида временной диаграммы сделан вывод о том, что все модули написаны правильно и проект корректно реализован.

|

|

|

Скачать 1.9 Mb.

Скачать 1.9 Mb.