курс. курсач_борон_даня. Содержание х1Х0 13 Х3Х2 13 00 13 01 13

Скачать 1.9 Mb. Скачать 1.9 Mb.

|

X[0]);

X[2] | X[0]) & (

X[2] |

X[3] |

X[0]);

X[0]) & ( X[3] |

X[2] |

X[1] | X[0]) & (

X[2] | X[1] | X[0]);

X[3] | X[2] | |

assign Y[2] =(X[3] |

assign Y[1] =(X[3] | X[2]) & (X[3] | X[1]) & (X[2] |

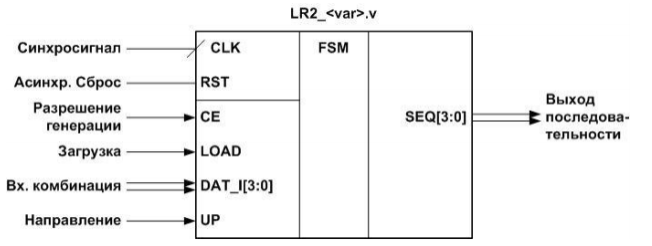

| RST | CLK | LOAD | CE | UP | Действие |

| 1 | X | X | X | X | Асинхронный сброс SEQ <= Func(4'h0) |

Продолжение Таблицы 2.1

| 0 | | 1 | X | X | Загрузка SEQ <= Func(DAT_I) |

| 0 | | 0 | 1 | 0 | Обратная генерация SEQ <= Func(i-1) |

| 0 | | 0 | 1 | 1 | Прямая генерация SEQ <= Func(i+1) |

| 0 | | 0 | 0 | X | Хранение SEQ <= SEQ |

Последовательность генерируемых сигналов определяется функцией Func(i), где i – 4-разрядный двоичный индекс, представляющий собой номер элемента последовательности. Инкремент индекса соответствует прямой генерации последовательности. Декремент индекса соответствует обратной генерации последовательности.

Последовательность определяется, исходя из Таблицы 1.1, следующим образом: индекс-i задан входными комбинациями от F до 0 в верхней строке таблицы, а выходные комбинации Func(i), формируемые на выходах SEQ[3:0], заданы второй строкой таблицы. Таблица состояний и выходных значений автомата совпадает с таблицей истинности, представленной в Таблице 1.2.

Переходы автомата при прямой и обратной генерациях представлены в Таблицах 2.2 и 2.3 соответственно.

Таблица 2.2 – Переходы автомата при прямой генерации

| HEX | X30 | X20 | X10 | X00 | HEX | X31 | X21 | X11 | X01 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 2 | 0 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 3 | 0 | 0 | 1 | 1 |

| 3 | 0 | 0 | 1 | 1 | 4 | 0 | 1 | 0 | 0 |

| 4 | 0 | 1 | 0 | 0 | 5 | 0 | 1 | 0 | 1 |

| 5 | 0 | 1 | 0 | 1 | 6 | 0 | 1 | 1 | 0 |

| 6 | 0 | 1 | 1 | 0 | 7 | 0 | 1 | 1 | 1 |

Продолжение Таблицы 2.2

| 7 | 0 | 1 | 1 | 1 | 8 | 1 | 0 | 0 | 0 |

| 8 | 1 | 0 | 0 | 0 | 9 | 1 | 0 | 0 | 1 |

| 9 | 1 | 0 | 0 | 1 | A | 1 | 0 | 1 | 0 |

| A | 1 | 0 | 1 | 0 | B | 1 | 0 | 1 | 1 |

| B | 1 | 0 | 1 | 1 | C | 1 | 1 | 0 | 0 |

| C | 1 | 1 | 0 | 0 | D | 1 | 1 | 0 | 1 |

| D | 1 | 1 | 0 | 1 | E | 1 | 1 | 1 | 0 |

| E | 1 | 1 | 1 | 0 | F | 1 | 1 | 1 | 1 |

| F | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

Таблица 2.1 — Переходы автомата при обратной генерации

| HEX | X3 | X2 | X1 | X0 | HEX | Y3 | Y2 | Y1 | Y0 |

| 0 | 0 | 0 | 0 | 0 | D | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | C | 1 | 1 | 0 | 0 |

| 2 | 0 | 0 | 1 | 0 | 8 | 1 | 0 | 0 | 0 |

| 3 | 0 | 0 | 1 | 1 | D | 1 | 1 | 0 | 1 |

| 4 | 0 | 1 | 0 | 0 | 4 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 9 | 1 | 0 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 | A | 1 | 0 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 | E | 1 | 1 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | F | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | D | 1 | 1 | 0 | 1 |

| A | 1 | 0 | 1 | 0 | 2 | 0 | 0 | 1 | 0 |

| B | 1 | 0 | 1 | 1 | D | 1 | 1 | 0 | 1 |

| C | 1 | 1 | 0 | 0 | A | 1 | 0 | 1 | 0 |

| D | 1 | 1 | 0 | 1 | E | 1 | 1 | 1 | 0 |

| E | 1 | 1 | 1 | 0 | E | 1 | 1 | 1 | 0 |

| F | 1 | 1 | 1 | 1 | A | 1 | 0 | 1 | 0 |

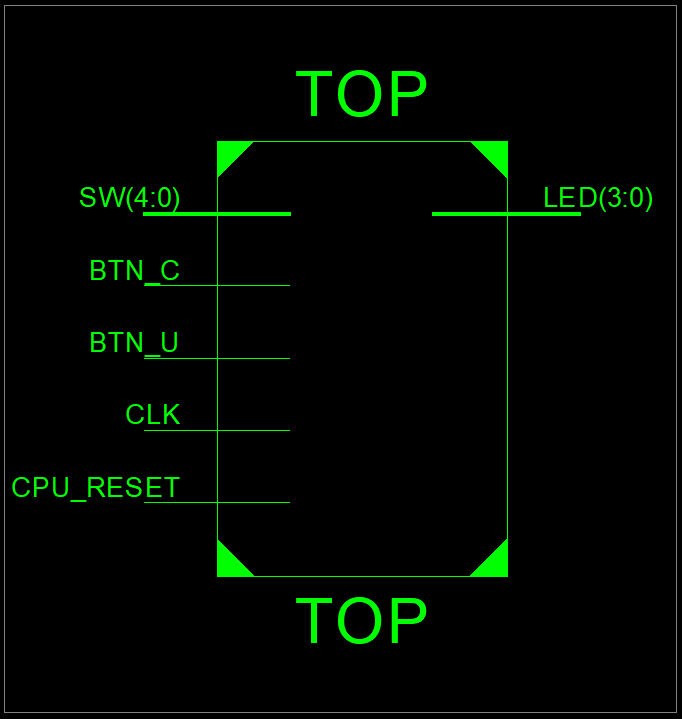

Также, нужно было сгенерировать RTL-модель, описывающую автомат. В ходе выполнения работы были сгенерированы 2 модели. Первая — общая, показывающая только входы и выходы модуля верхнего уровня. Вторая же более развёрнута, так как показывает соединения между отдельными модулями проекта. Сгенерированные модели представлены на Рисунках 2.2 и 2.3 соответственно.