Суперскаляризация. Тема 2.4. Суперскаляризация. Матричные и векторные процессоры. Суперскалярных. Pentium первый суперскалярный процессор Intel. Здесь две линии, что позволяет ему при одинаковых частотах быть вдвое производительней i80486, выполняя сразу две инструкции за такт

Скачать 207.17 Kb. Скачать 207.17 Kb.

|

|

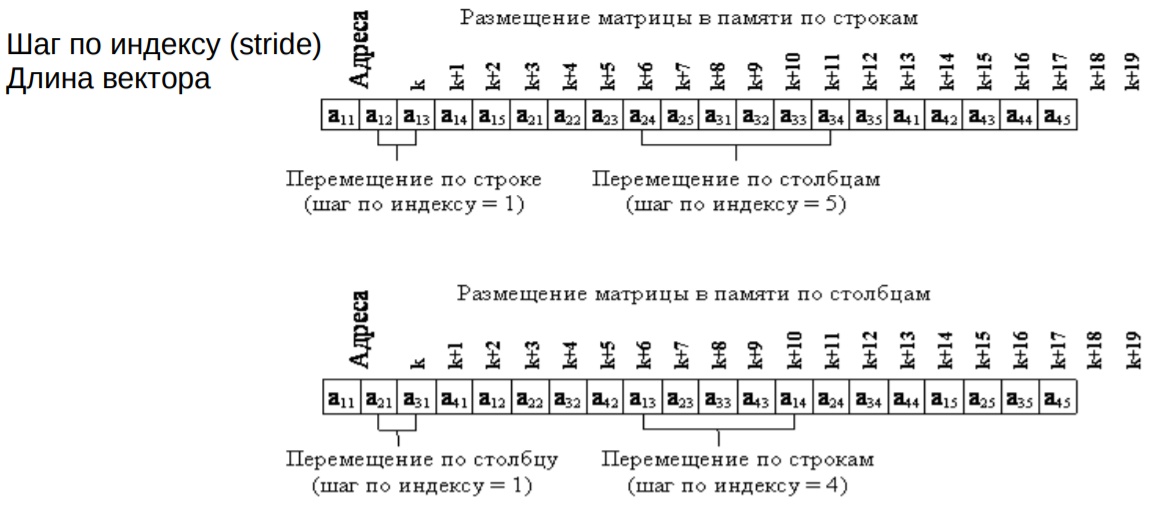

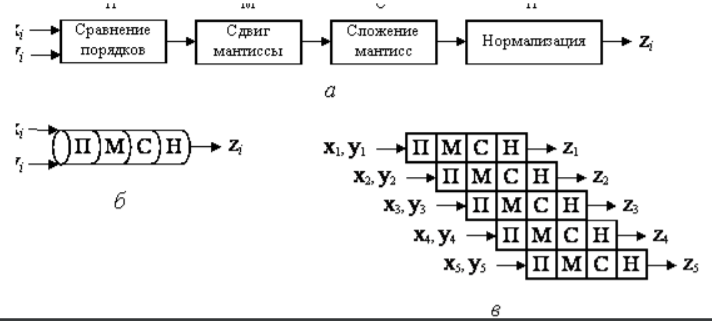

Суперскаляризация Процессоры с несколькими линиями конвейера получили название суперскалярных. Pentium — первый суперскалярный процессор Intel. Здесь две линии, что позволяет ему при одинаковых частотах быть вдвое производительней i80486, выполняя сразу две инструкции за такт. Во многих вычислительных системах, наряду с конвейером команд, используются конвейеры данных. Сочетание этих двух конвейеров дает возможность достичь очень высокой производительности на определенных классах задач, особенно если используется несколько различных конвейерных процессоров, способных работать одновременно и независимо друг от друга. Операции над вещественными числами (с плавающей запятой) Сопроцессоры. Для расширения вычислительных возможностей центрального процессора — выполнения арифметических операций, вычисления основных математических функции (тригонометрических, показательных, логарифмических) и т. д. — в состав ЭВМ добавляется математический сопроцессор. Применение сопроцессора повышает производительность вычислений в сотни раз. В разных поколениях процессоров он назывался по-разному — FPU (Floating Point Unit — блок чисел/операций с плавающей точкой — БПЗ) или NPX (Numeric Processor extension — числовое расширение процессора). Для процессоров 386 и ниже сопроцессор был отдельной микросхемой, подключаемой к локальной нише основного процессора. В любом случае сопроцессор исполняет только свои специфические команды, а всю работу по декодированию инструкций и доставке данных осуществляет ЦП. Блоки операций с плавающей запятой. С программной точки зрения сопроцессор и процессор выглядят как единое целое. В современных (486+) процессорах БПЗ располагается на одном кристалле с центральным процессором. Вектор (в программировании) — одномерный массив. При размещении матрицы в памяти все ее элементы заносятся в ячейки с последовательными адресами, причем данные могут быть записаны строка за строкой или столбец за столбцом.  Векторный компьютер Векторные компьютеры манипулируют массивами сходных данных подобно тому, как скалярные машины обрабатывают отдельные элементы таких массивов. Это делается за счет использования специально сконструированных векторных центральных процессоров. Когда данные обрабатываются посредством векторных модулей, результаты могут быть выданы на один, два или три такта частотогенератора (такт частотогенератора является основным временным параметром системы). При работе в векторном режиме векторные процессоры обрабатывают данные практически параллельно, что делает их в несколько раз более быстрыми, чем при работе в скалярном режиме. Категории процессоров, способных реализовать векторную обработку - процессор с конвейерным арифметико-логическим устройством; - процессор с параллельным арифметико-логическим устройством; - параллельные процессоры. Процессор с конвейерным АЛУ В варианте с конвейерным АЛУ обработка элементов векторов производится конвейерным АЛУ для чисел с плавающей запятой (ПЗ). Операции с числами в форме с ПЗ достаточно сложны, но поддаются разбиению на отдельные шаги. Например, сложение двух чисел сводится к четырем этапам: сравнению порядков, сдвигу мантиссы меньшего из чисел, сложению мантисс и нормализации результата. Каждый этап может быть реализован с помощью отдельной ступени конвейерного АЛУ. Очередной элемент вектора подается на вход конвейера, как только освобождается первая ступень.  Процессор с параллельным АЛУ Если параллельно используются конвейерные АЛУ, то возможен еще один уровень конвейеризации. Вычислительные системы, где реализована эта идея, называются векторно-конвейерными. Коммерческие векторно-конвейерные ВС, в состав которых для обеспечения универсальности включен также скалярный процессор, известны как супер ЭВМ. Векторный процессор Этот тип процессора является более специализированным, чем скалярный процессор, что делает его менее популярным выбором для среднего компьютера. Средний компьютер выполняет широкий спектр задач, и самый быстрый способ выполнения множества различных типов задач - это скалярный процессор. Это потому, что процессор может переключаться между задачами намного быстрее. Векторный процессор используется в узкоспециализированной электронике, такой как суперкомпьютеры. Эти процессоры намного мощнее, когда используются для крупномасштабных задач. Небольшие задачи, такие как открытие текстового документа или воспроизведение видео, могут выполняться скалярным процессором быстрее, чем векторный процессор. Матричные ВС Назначение матричных вычислительных систем во многом схоже с назначением векторных ВС – обработка больших массивов данных. В основе матричных систем лежит матричный процессор (array processor), состоящий из регулярного массива процессорных элементов (ПЭ). Системы подобного типа имеют общее управляющее устройство, генерирующее поток команд, и большое число ПЭ, работающих параллельно и обрабатывающих каждый свой поток данных. С целью обеспечения достаточной эффективности системы при решении широкого круга задач необходимо организовать связи между процессорными элементами так, чтобы наиболее полно загрузить процессоры работой. Именно характер связей между ПЭ и определяет разные свойства системы. Между матричными и векторными системами есть существенная разница: матричный процессор интегрирует множество идентичных функциональных блоков (ФБ), логически объединенных в матрицу и работающих в SIMD стиле (SIMD — принцип компьютерных вычислений, позволяющий обеспечить параллелизм на уровне данных. Один из классов вычислительных систем в классификации Флинна. SIMD-компьютеры состоят из одного командного процессора, называемого контроллером, и нескольких модулей обработки данных, называемых процессорными элементами.). Не столь существенно, как конструктивно реализована матрица процессорных элементов – на едином кристалле или на нескольких. Важен сам принцип – ФБ логически скомпонованы в матрицу и работают синхронно, т.е. присутствует только один поток команд для всех. Векторный процессор имеет встроенные команды для обработки векторов данных, что позволяет эффективно загрузить конвейер из функциональных блоков. В свою очередь, векторные процессоры проще использовать, потому что команды для обработки векторов – это более удобная для человека модель программирования, чем SIMD. Матричный процессор Параллельная обработка множественных элементов данных осуществляется массивом процессоров (МПр). Единый поток команд, управляющий обработкой данных в массиве процессоров, генерируется контроллером массива процессоров (КМП). КМП выполняет последовательный программный код, реализует операции условного и безусловного переходов, транслирует в МПр команды, данные и сигналы управления. Компоненты матричной ВС ● Массив процессоров (МПр) осуществляет параллельную обработку множественных элементов данных. ● Контроллер массива процессоров (КМП) генерирует единый поток команд, управляющий обработкой данных в массиве процессоров, выполняет последовательный программный код, реализует операции условного и безусловного переходов, транслирует в МПр команды, данные и сигналы управления. Команды обрабатываются процессорами в режиме жесткой синхронизации. ● Сигналы управления используются для синхронизации команд и пересылок, а также для управления процессом вычислений, в частности определяют, какие процессоры массива должны выполнять операцию, а какие - нет. ● Шина широковещательной рассылки служит для передачи команд, данных и сигналов управления из КМП в массив процессоров. ● Шина результата служит для трансляции результатов вычислений из МПр в КМП (это требуется, поскольку выполнение операций условного перехода зависит от результатов вычислений). ●Интерфейсная ВМ (front-end computer) служит для обеспечения пользователя удобным интерфейсом при создании и отладке программ. В роли такой ВМ выступает универсальная вычислительная машина, на которую дополнительно возлагается задача загрузки программ и данных в КМП. Кроме того, загрузка программ и данных в КМП может производиться и напрямую с устройств ввода/вывода, например с магнитных дисков. После загрузки КМП приступает к выполнению программы, транслируя в МПр по широковещательной шине соответствующие SIMD-команды. Интерфейсная ВМ Интерфейсная ВМ (ИВМ) соединяет матричную SIMD-систему с внешним миром, используя для этого какой-либо из сетевых интерфейсов, например Ethernet, как это имеет место в системе MasPar MP-1. Интерфейсная ВМ работает под управлением операционной системы, чаще всего ОС UNIX. На ИВМ пользователи подготавливают, компилируют и отлаживают свои программы. В процессе выполнения программы сначала загружаются из интерфейсной ВМ в контроллер управления массивом процессоров, который выполняет программу и распределяет команды и данные по процессорным элементам массива. В некоторых ВС, например в Massively Parallel Computer MPP, при создании, компиляции и отладке программ КМП и интерфейсная ВМ используются совместно. На роль ИВМ подходят различные вычислительные машины. Так, в системе СМ-2 в этом качестве выступает рабочая станция SUN-4, в системе MasPar — DECstation 3000, а в системе МРР - DEC VAX-11/78. Контроллер массива процессоров Функции контроллера массива процессоров: ● выполняет последовательный программный код, ● реализует команды ветвления программы, ● транслирует команды и сигналы управления в процессорные элементы. Режимы работы микропроцессора Впервые о различных режимах работы процессоров IA-32 стали говорить с появлением процессора 80286. Это был первый представитель данного семейства процессоров, в котором были реализованы многозадачность и защищенная архитектура. Чтобы обеспечить совместимость с предыдущими представителями этого семейства (8086/88, 80186/188) в процессоре 80286 было реализовано два режима функционирования: режим эмуляции 8086 (режим реального адреса) и защищенный режим, в котором используются все возможности процессора. В последующих поколениях процессоров этого семейства защищенный режим становится основным режимом работы. В новых поколениях процессоров Intel появился еще один режим работы - режим системного управления. Впервые он был реализован в процессорах 80386SL и i486SL. Начиная с расширенных моделей Intel486, этот режим стал обязательным элементом архитектуры IA-32. С его помощью прозрачно даже для операционной системы на уровне BIOS реализуются функции энергосбережения. Защищенный режим (Protected Mode) Основным режимом работы микропроцессора является защищенный режим. Ключевыми особенностями защищенного режима являются: виртуальное адресное пространство, защита и многозадачность. В защищенном режиме программа оперирует адресами, которые могут относиться к физически отсутствующим ячейкам памяти, поэтому такое адресное пространство называется виртуальным. Размер виртуального адресного пространства программы может превышать емкость физической памяти и достигать 64Тбайт. Для адресации виртуального адресного пространства используется сегментированная модель, в которой адрес состоит из двух элементов: селектора сегмента и смещения внутри сегмента. С каждым сегментом связана особая структура, хранящая информацию о нем, - дескриптор. Кроме "виртуализации" памяти на уровне сегментов существует возможность "виртуализации" памяти при помощи страниц - страничная трансляция. Страничная трансляция предоставляет удобные средства для реализации в операционной системе функций подкачки, а кроме того в процессорах P6+ обеспечивает 36-битную физическую адресацию памяти (64Гбайт). Встроенные средства переключения задач обеспечивают многозадачность в защищенном режиме. Среда задачи состоит из содержимого регистров МП и всего кода с данными в пространстве памяти. Микропроцессор способен быстро переключаться из одной среды выполнения в другую, имитируя параллельную работу нескольких задач. Для некоторых задач может эмулироваться управление памятью как у процессора 8086. Такое состояние задачи называется режимом виртуального 8086 (Virtual 8086 Mode). О пребывании задачи в таком состоянии сигнализирует бит VM в регистре флагов. При этом задачи виртуального МП 8086 изолированы и защищены, как от друг друга, так и от обычных задач защищенного режима. Защита задач обеспечивается следующими средствами: контроль пределов сегментов, контроль типов сегментов, контроль привилегий, привилегированные инструкции и защита на уровне страниц. Контроль пределов и типов сегментов обеспечивает целостность сегментов кода и данных. Программа не имеет права обращаться к виртуальной памяти, выходящей за предел того или иного сегмента. Программа не имеет права обращаться к сегменту данных как к коду и наоборот. Архитектура защиты микропроцессора обеспечивает 4 иерархических уровня привилегий, что позволяет ограничить задаче доступ к отдельным сегментам в зависимости от ее текущих привилегий. Кроме того, текущий уровень привилегий задачи влияет на возможность выполнения тех или иных специфических команд (привилегированных инструкций). Функции страничной трансляции, впервые появившиеся в МП Intel386, обеспечивают дополнительные механизмы защиты на уровне страниц. Реальный режим (Real Mode) В реальном режиме микропроцессор работает как очень быстрый 8086 с возможностью использования 32-битных расширений. Механизм адресации, размеры памяти и обработка прерываний (с их последовательными ограничениями) МП Intel386 в реальном режиме полностью совпадают с аналогичными функциями МП 8086. В отличие от 8086 микропроцессоры 286+ в определенных ситуациях генерируют исключения, например, при превышении предела сегмента, который для всех сегментов в реальном режиме - 0FFFFh. Имеется две фиксированные области в памяти, которые резервируются в режиме реальной адресации: область инициализации системы область таблицы прерываний Ячейки от 00000h до 003FFH резервируются для векторов прерываний. Каждое из 256 возможных прерываний имеет зарезервированный 4-байтовый адрес перехода. Ячейки от FFFFFFF0H до FFFFFFFFH резервируются для инициализации системы. Режим системного управления (System Management Mode) Режим системного управления предназначен для выполнения некоторых действий с возможностью их полной изоляции от прикладного программного обеспечения и даже операционной системы. Переход в этот режим возможен только аппаратно. Когда процессор находится в режиме SMM, он выставляет сигнал SMIACT#. Этот сигнал может служить для включения выделенной области физической памяти (System Management RAM), так что память SMRAM можно сделать доступной только для этого режима. При входе в режим SMM процессор сохраняет свой контекст в SMRAM (контекст сопроцессора не сохраняется) по адресу SMM Base и передает управление процедуре, называемой обработчиком System Management Interrupt, по адресу SMM Base+8000h (по умолчанию SMM Base содержит значение 30000h). Состояние процессора в этот момент точно определено: EFLAGS обнулен (кроме зарезервированных битов), сегментные регистры содержат селектор 0000, базы сегментов установлены в 00000000, пределы - 0FFFFFFFFh. Следует отметить, что в режиме SMM не предусмотрена работа с прерываниями и особыми случаями: прерывания по IRQ и SMI# замаскированы, пошаговые ловушки и точки останова отключены, обработка прерывания по NMI откладывается до выхода из режима SMM. Если необходимо обеспечить работу с прерываниями или особыми случаями, то надо инициализировать IDT и разрешить прерывания, выставив флаг IF в регистре EFLAGS. Прерывания по NMI будут разблокированы автоматически после первой же команды IRET. При возврате из SMM (по инструкции RSM) процессор восстанавливает свой контекст из SMRAM. Обработчик может программно внести изменения в образ контекста процессора, тогда процессор перейдет не в то состояние, в котором произошло SMI. Если SMI было получено во время выполнения инструкции HLT, то дальнейшие действия при выходе из SMM определяются значением поля "Auto HALT Restart": процессор может снова вернуться к инструкции останова или перейти к выполнению следующей команды. Если SMI произошло при выполнении инструкции ввода-вывода, то в зависимости от значения поля "I/O Instruction Restart" возможен рестарт инструкции ввода вывода. Эти особенности режима системного управления позволяют использовать его для реализации системы управления энергосбережением компьютера или функций безопасности и контроля доступа. Переключение между режимами После инициализации процессор находится в реальном режиме. Процессор может быть переведен в защищенный режим установкой бита 0 (Protect Enable) в регистре CR0:

Второй вариант "достался в наследство" от 16-разрядной архитектуры 80286, для совместимости с которой ее регистр MSW (Machine Status Word) отображается на младшее слово регистра CR0. Вернуться в режим реального адреса процессор может по сигналу RESET или (в отличие от 80286) сбросив бит PE: MOV EAX,00000000h MOV CR0,EAX Для совместимости с 80286 инструкция LMSW бит PE не сбрасывает. Режим системного управления изолирован от других режимов. Процессор переходит в этот режим только аппаратно: по низкому уровню на контакте SMI# или по команде с шины APIC (Pentium+). Никакой программный способ не предусмотрен для перехода в этот режим. Процессор возвращается из режима системного управления в тот режим, при работе в котором был получен сигнал SMI#. Возврат происходит по команде RSM. Эта команда работает только в режиме системного управления и в других режимах не распознается, генерирую исключение #6 (недействительный код операции). |