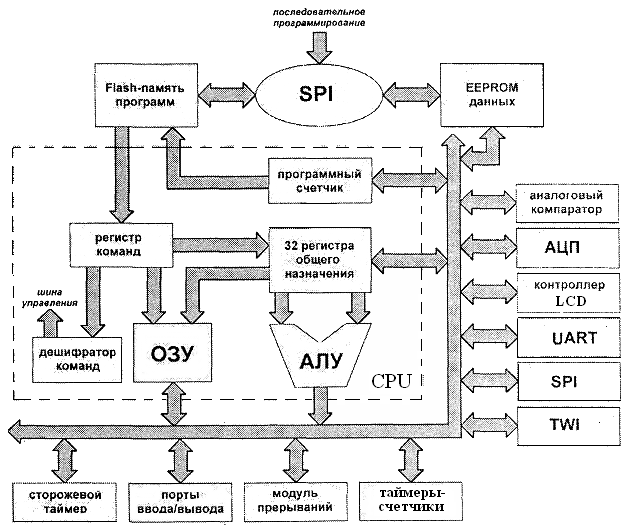

Ардуйно. ЛК1 - Архитектура и порты AVR. Тема Архитектура микроконтроллеров серии avr

Скачать 379 Kb. Скачать 379 Kb.

|

|

| DDXn | PortXn | Ввод/ вывод | Подтягивающее сопротивление | Описание |

| 0 | 0 | Ввод | Нет | Высокоомный вход |

| 0 | 1 | Ввод | Да | Подтягивающее сопротивление |

| 1 | 0 | Вывод | Нет | Двухтактный выход: лог. 0 |

| 1 | 1 | Вывод | Нет | Двухтактный выход: лог. 1 |

Регистр направления передачи данных и регистр порта доступны для чтения и записи. AVR в состоянии принимать входные токи силой до 20 мА и благодаря этому, например, напрямую управлять светодиодами, подключенными к питающему напряжению.

1.2.1 Порт А

Наряду с общими функциями ввода/вывода, в качестве особой функции через этот порт осуществляется управление работой мультиплексированной шины адресов и данных, если к микроконтроллеру семейства AVR подключено внешнее запоминающее устройство RAM. На этот случай порт А оснащен внутренними подтягивающими сопротивлениями.

Когда порт А с помощью разряда SRE регистра MCUCR переключен на выполнение альтернативной функции, его регистр направления передачи данных DDRA соответствующим образом переписывается.

1.2.1.1 Регистр данных порта А.

Регистр данных PORTA расположен в области ввода/вывода по адресу $1В (по адресу $ЗВ в памяти RAM) и доступен для чтения и записи. После поступления сигнала сброса он инициализируется значением $00.

1.2.1.2 Регистр направления передачи данных DDRA.

Регистр направления передачи данных DDRA расположен в области ввода/вывода по адресу $1А (по адресу $ЗА в памяти RAM) и доступен для чтения и записи.

1.2.2 Порт В

Наряду с выполнением общих функций ввода/вывода, он также выполняет и некоторые особые функции.

1.2.2.1 Регистр данных порта В.

Регистр данных порта В расположен в области ввода/вывода по адресу $18 (по адресу $38 в памяти RAM) и доступен для чтения и записи. После поступления сигнала сброса он инициализируется значением $00.

Таблица 1.2 – Назначение разрядов регистра порта В

| P0RTB7 | P0RTB6 | P0RTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 |

| SCK | MISO | MOSI | | | | AIN1 | AIN0 |

| SCK | MISO | MOSI | - | OC1 | - | AIN1 | AIN0 |

| SCK | MISO | MOSI | /SS | AIN1 | AIN0 | T1 | T0 |

| SCK | MISO | MOSI | /SS | AIN1 | AIN0 | T1 | T0 |

Описание разрядов регистра порта В:

SCK - тактовый выход в случае, если ведущим устройством является последовательный интерфейс SPI, и тактовый вход в случае, если этот интерфейс является ведомым;

MISO - вход последовательного интерфейса SPI в качестве ведущего устройства, и выход в случае, если этот интерфейс применяется в качестве ведомого;

MOSI - выход последовательного интерфейса SPI в качестве ведущего устройства, и вход в случае, если этот интерфейс применяется в качестве ведомого;

/SS - вход выбора, если SPI является ведомым;

AIN1 - инвертирующий вход аналогового компаратора;

AIN0 — неинвертирующий вход аналогового компаратора;

ОС1 - выход функции сравнения таймера/счетчика Т/С1;

T1 - тактовый вход для T/C1;

Т0 - тактовый вход для Т/С0.

1.2.2.2 Регистр направления передачи данных DDRB.

Регистр направления передачи данных DDRB расположен в области ввода/вывода по адресу $17 (по адресу $37 в памяти RAM) и доступен для чтения и записи.

1.2.3 Порт С

Наряду с общими функциями ввода/вывода, в качестве особой функции выполняется вывод через порт С старшего байта адреса, когда подсоединена внешняя память RAM. На этот случай порт С оснащен внутренними подтягивающими сопротивлениями.

Когда порт С с помощью разряда SRE регистра MCUCR переключен на выполнение альтернативной функции, его регистр направления передачи данных DDRC соответствующим образом переписывается.

1.2.3.1 Регистр данных порта С.

Регистр данных PORTC расположен в области ввода/вывода по адресу $15 (по адресу $35 в памяти RAM) и доступен для чтения и записи.

1.2.3.2 Регистр направления передачи данных DDRC.

Регистр направления передачи данных DDRC расположен в области ввода/вывода по адресу $14 (адрес $34 в RAM) и доступен для чтения и записи.

1.2.4 Порт D

Наряду с выполнением общих функций ввода/вывода, порт D также выполняет некоторые особые функции.

1.2.4.1 Регистр данных порта D.

Регистр данных порта D расположен в области ввода/вывода по адресу $12 (по адресу $32 в RAM) и доступен для чтения и записи.

Таблица 1.3 – Назначение разрядов порта D

| P0RTD7 | PORTD6 | P0RTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 |

| - | - | - | T0 | - | INT0 | | - |

| - | ICP | T1 | T0 | INT1 | INT0 | TxD | RxD |

| /RD | /WR | 0C1A | - | INT1 | INT0 | TxD | RxD |

| /RD | /WR | OC1A | - | INT1 | INT0 | TxD | RxD |

Разряды порта D:

/RD - управляющий сигнал чтение внешней памяти RAM;

/WR - управляющий сигнал запись во внешнюю память RAM;

ICP - вход для функции захвата таймера/счетчика Т/С1;

ОС1А - выход для функции сравнения или функции ШИМ таймера/счетчикаТ/С1;

Т1 - тактовый вход для Т/С1;

Т0 - тактовый вход для Т/С0;

INT1 - вход для внешнего прерывания 1;

INT0 - вход для внешнего прерывания 0;

TxD - информационный выход приемопередатчика UART;

RxD - информационный вход приемопередатчика UART.

1.2.4.2 Регистр направления передачи данных DDRD.

Регистр направления передачи данных порта DDRD расположен в области ввода/вывода по адресу $11 (по адресу $31 в RAM) и доступен для чтения и записи.

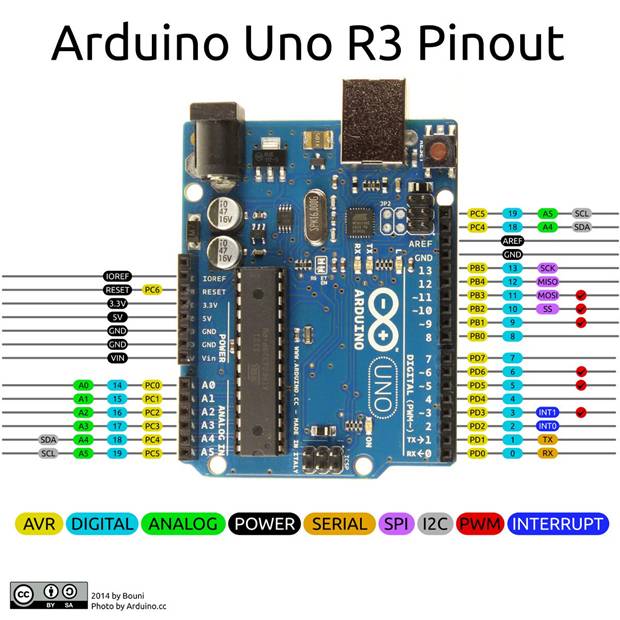

1.3 Расположение выводов (пинов) на плате Arduino Uno R3

Пины разбиты на 3 группы: Digital – блок цифровых пинов; Analog – блок аналоговых пинов; Power – блок пинов, которые связаны с питанием и работой микросхемы.

Рисунок 1.3 – Распиновка платы ардуино UNO

При этом в разделе Digital пины, которые могут выдавать ШИМ (PWM)-сигнал, помечены тильдой «». Для служебных целей и проверки работоспособности контроллера на плате установлен светодиод, который подключен к 13-му выводу, а из среды разработки Arduino IDE к нему можно обращаться через встроенную директиву LED_BUILTIN.

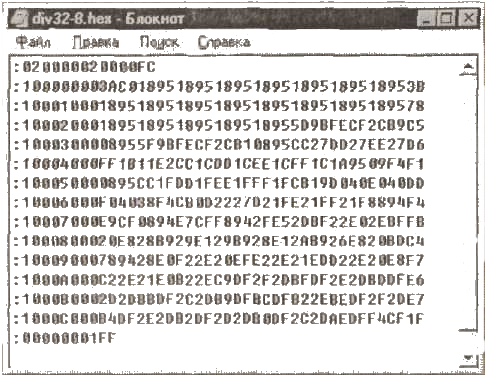

1.4 Hex-файлы

Двоичное представление команды - командное слово, или код операции (КОП) - компилятор записывает в виде числа в выходной файл с расширением hex, который затем используется программатором для записи в контроллер. Рассматриваемый формат разработан фирмой Intel (есть и другие "гексы") и отличается тем, что содержит числа в шестнадцатеричной коде. На рисунке 1.4 представлен файл короткой программы, открытый в обычном Блокноте. Чтение затрудняется тем, что строки не поделены на отдельные байты. Разбираться будет проще, если скопировать этот файл под другим именем и расставить в нем пробелы после каждой пары символов.

Рисунок 1.4 - Файл формата HEX

Основную часть файла занимают информационные строки, содержащие непосредственно КОП. Они состоят из ряда служебных полей и собственно данных. Каждая строка начинается двоеточием и заканчивается парой символов "возврат каретки" - "перевод строки", на экране не отображаемых. После двоеточия идет число байтов в строке - кроме первой и последней, везде стоит число 10 (десятичное 16), т.е. в каждой строке будет ровно 16 информационных байтов (исключая служебные). Затем следуют два байта адреса памяти - куда писать (в первой строке 0000, во второй это будет, естественно, 0010, т. е. предыдущий адрес + 16, и т. д.). Наконец, после адреса расположен еще один служебный байт, обозначающий тип данных, который в информационных строках равен 00 (а в первой и последней - 02 и 01, о чем далее). Только после этого начинаются собственно байты данных, которые означают соответствующие КОП, записанные пословно (КОП для AVR занимают в основном два байта, и память в этих МК также организована пословно), причем так, что младший байт идет первым.

Таким образом, запись в первой информационной строке 3AС0 в привычном нам "арабском" порядке, когда самый старший разряд располагается слева, должна выглядеть, как С03А.

В первой строке служебный байт типа данных равен 02, и это означает, что данные в ней представляют сегмент памяти, с которого должна начинаться запись (в данном случае 0000). Заканчивается hex-файл всегда строкой:00000001FF - значение типа данных 01 означает конец записи, данных больше не ожидается. А что означает FF?

Самым последним байтом в каждой строке идет контрольная сумма (дополнение до 2, LRC - Longitudinal Redundancy Check) байтов строки, включая служебные. Алгоритм вычисления LRC - нужно вычесть из числа 256 значения всех байтов строки (не обращая внимание на перенос) и взять младший байт результата. Так, в первой строке число информационных байтов всего два, оба равны нулю, плюс число информационных байтов равно 2, плюс служебный байт типа данных, равный также 2, итого контрольная сумма всегда равна 256- 2-0-0-2 = 252 = $FC. В последней строке одни нули, кроме типа данных, равного 1, - соответственно контрольная сумма равна 256 - I = 255 = $FF.

1.4.1 Расшифровка данных

Первое слово в 1-й информационной строке равно C03A. Значению старшей тетрады в КОП, равной С (1100), соответствует команда rjmp - любая программа начинается с безусловного перехода на метку RESET. Теперь очевидно, что остальные биты в этом значении (03А) представляют абсолютный адрес в программе, где в тексте стоит метка RESET.

Адреса отсчитываются по словам, а не по байтам, т.е. число $ЗА (58) нужно умножить на 2 (получится 116 = $74) и искать в этой области. Разыщем строку с адресом $0070, отсчитаем три пары байтов от начала данных и найдем там фрагмент "F894", который в нормальной записи будет выглядеть как 94F8, а это код команды cli, запрещающей прерывания (которая в начале программы лишняя, т.к. они все равно запрещены, но, видимо, поставлена на всякий случай).

Следующая команда будет начинаться с байта Е5, и первая тетрада в ней обозначает код команды ldi (1110), а пятерка есть фрагмент адреса конца памяти (ramend), который в силу довольно сложного формата записи команды получается на самом деле равным 025F (см. значение младшего байта, равное $2F), Это соответствует значению ramend, определенному в inc-файлах для МК с 512 байтами встроенного ОЗУ (025F = 607, т.е. всего адресов 608, из которых 96 (51) занимают регистры, итого получается 512 ($0200) незанятых байтовых ячеек, составляющих ОЗУ). Если обратить внимание на первую-вторую строки с данными, то увидим повторяющийся фрагмент "1895", который является командой reti.

Программа, которая превращает код обратно в текст, называется дизассемблер (она входит в AVR Studio).

Если текст программы по каким-то причинам отсутствует, а загрузочный hex-файл имеется, то исходный код можно немного подправить под свои нужды.