Цифровые устройства. Что такое цифровые микросхемы. Виды цифровых микросхем

Скачать 2.25 Mb. Скачать 2.25 Mb.

|

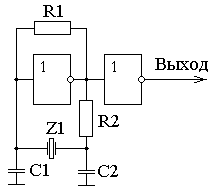

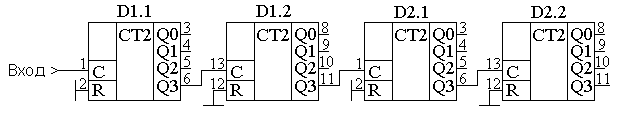

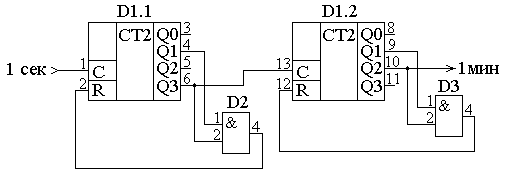

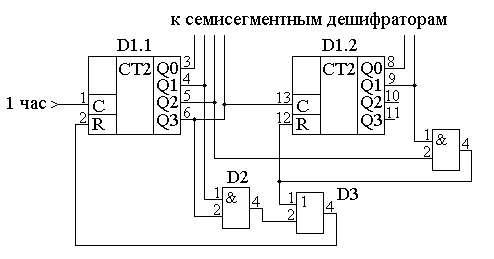

Глава 2Разработка принципиальной схемыПри разработке принципиальной схемы чрезвычайно важен выбор серии микросхем, на которой будет реализована эта схема. Для часов самым важным параметром является ток, потребляемый ими, так как в большинстве случаев или все часы, или часть схемы часов питается от элементов питания. Поэтому при разработке схемы будем выбирать микросхемы, реализованные по КМОП технологии. Разработку схемы часов начнём с кварцевого генератора. Как уже обсуждалось при разработке структурной схемы, в составе генератора будет применён часовой кварцевый резонатор. Для уменьшения стоимости всего устройства в целом применим простейшую схему генератора — ёмкостную трёхточку, а так как генератор предназначен для синхронизации цифрового устройства, то генератор выполним на логическом инверторе. Принципиальная схема такого кварцевого генератора приведена на рисунке 12.1.5.  Рисунок 12.1.5 Схема кварцевого генератора, выполненная на логическом инверторе Напомню, что резистор R1 предназначен для автоматического запуска генератора при включении питания. Этот же элемент определяет коэффициент усиления инвертора, и чем больше будет этот коэффициент усиления, тем более прямоугольные колебания будут формироваться на его выходе, а это, в свою очередь, приведёт к снижению тока, потребляемого кварцевым генератором. Выберем номинал резистора R1 равным 10Мом. Резистор R2 предназначен для предотвращения самовозбуждения генератора на частоте, определяемой ёмкостью кварцедержателя. Выберем номинал этого резистора 510 кОм. Номинал ёмкости конденсаторов C1 и C2 определяется величиной паразитных ёмкостей схемы. Выберем конденсаторы с ёмкостью 20пФ. Равное значение ёмкостей этих конденсаторов позволяет обеспечить максимальный коэффициент передачи колебательной системы, построенной на кварцевом резонаторе Z1 и конденсаторах C1 и C2. Второй инвертор в схеме генератора предназначен для уменьшения длительности фронтов формируемого прямоугольного колебания. Это необходимо для уменьшения влияния последующей схемы на стабильность колебаний задающего генератора, а также для более надёжной работы цифровых счётчиков делителя частоты. В качестве микросхемы, содержащей инверторы, выберем микросхему SN74LVC2G04DRL. В этой микросхеме, построенной по КМОП технологии, содержится два инвертора. О том, что в микросхеме содержится два элемента, говорит обозначение 2G. То что это инверторы — обозначается цифрой 04, а то, что в микросхеме использован корпус с шагом выводов 0,5 мм — буквы DRL. Размеры корпуса этой микросхемы не превышают 1.6*1.6мм (у корпуса всего шесть выводов). Микросхема способна работать в диапазоне напряжений от 1,5 до 5,5 В. Следующей реализуем схему делителя частоты до значения 1 Гц. Напомню, что период колебаний с частотой 1 Гц равен 1 секунде. Как это мы уже определили при разработке структурной схемы, его коэффициент деления должен быть равен 32768. То есть для реализации делителя потребуется 15 счётных триггеров. Конечно, можно взять микросхему К176ИЕ12, специально разработанную для этой цели, но мы не ищем простых путей, поэтому используем универсальную микросхему SN74HC393PW. В ней есть два независимых четырёхразрядных двоичных счётчика. Это означает, что для реализации нашего делителя будет достаточно всего двух микросхем. Размеры корпуса выбранной микросхемы не превышают 5´6.4мм. У корпуса этой микросхемы имеется 14 выводов. Если к габаритам часов нет особых требований, то можно использовать отечественную микросхему К1564ИЕ19. Ее корпус больше корпуса выбранной микросхемы более чем в два раза. Однако при этом даже номера выводов микросхем будут совпадать. Полученная принципиальная схема генератора секундных импульсов приведена на рисунке 12.1.6.  Рисунок 12.1.6. Схема делителя на 32768 генератора секундных импульсов Теперь вспомним, что в генераторе временных интервалов необходим еще один делитель частоты. Период импульсов на его выходе будет равен 1 минуте. Делитель на шестьдесят можно реализовать на точно такой же микросхеме что мы использовали и ранее для построения делителя на 32768. Делитель на шестьдесят не кратен степени числа два, поэтому для его реализации потребуется обратная связь. Для упрощения схемы обратим внимание, что число 60 разбивается на числа 10 и 6. И то, и другое число содержат только две единицы. Выводы 4-х разрядных счетчиков выходят на разные стороны корпуса микросхемы. Поэтому будет удобно использовать два независимых логических элемента “2И”. Это позволит значительно упростить разводку печатной платы и сократить длину соединительных проводов, тем самым, уменьшив площадь печатной платы и возможные помехи от работающей схемы. В качестве логических элементов “2И” используем две микросхемы SN74LVC1G08DRLR. То, что в микросхеме содержится только один логический элемент, мы определяем по символам 1G, а то, что это логический элемент“2И” - по цифрам 08. Размеры корпуса выбранной микросхемы не превышают 1.6´1.6мм. Отечественные варианты подобной микросхемы, например К1554ЛИ1, содержат в одном корпусе сразу по четыре логических элемента, расстояние между выводами составляет минимум 1,25мм. В результате схема, собранная на таких микросхемах, будет идентична по электрическим параметрам, но проиграет по размерам. Полученная схема делителя частоты на 60 и вырабатывающая импульсы с периодом 1 мин и состоящая из последовательно включенных делителей на 10 и на 6, приведена на рисунке 12.1.7. Схема реализована всего на трёх микросхемах. Использование обратной связи с выводов Q1 и Q3 превращает двоичный счётчик D1.1 в десятичный, а применение обратной связи с выводов Q1 и Q2 микросхемы D1.2 реализует счётчик по модулю 6.  Рисунок 12.1.7. Схема делителя на 60 генератора минутных импульсов Итак, мы закончили разработку генератора минутных импульсов. Всего нам потребовалось шесть микросхем, при этом три из них относятся к микросхемам малой логики и занимают минимум места на печатной плате цифрового устройства. Теперь можно приступить к разработке принципиальной схемы счетчика временных интервалов. Как мы уже выяснили при разработке структурной схемы часов, в состав этого счётчика входит точно такой же делитель на 60, как и в генераторе минутных импульсов, поэтому можно воспользоваться той же самой схемой. Отличие заключается только в том, что на этот раз нам потребуются все выходы счётчиков. Сигналы с этих выводов мы будем подавить на вход семисегментных дешифраторов блока индикации. Последний счётчик, который нам потребуется для реализации блока счётчика временных интервалов - это счётчик на 24. Этот счётчик было бы удобно реализовать на микросхеме десятичного счётчика, однако сдвоенных микросхем асинхронных десятичных счётчиков не производится, поэтому реализуем счётчик часов на той же микросхеме, что и остальные блоки часов — SN74HC393PW. Сложность в реализации этой схемы заключается в том, что коэффициент счёта не кратен десяти, поэтому сигнал обратной связи необходимо заводить на оба счётчика одновременно. Можно было бы реализовать этот счётчик в двоичном виде, но тогда возникнут сложности с отображением содержимого этого счётчика. Для того, чтобы реализовать на первом 4-х разрядном счётчике десятичный счётчик и одновременно получить возможность сброса всего счётчика часов в начале суток используем дополнительный логический элемент “2ИЛИ”. Сигнал сброса на выходе этой микросхемы появится либо в случае достижения первым счётчиком числа 10, либо при достижении всем счётчиком значения 24. В качестве логического элемента “2ИЛИ” используем микросхему малой логики, подобную уже использованной микросхеме “2И”. Это микросхема SN74LVC1G32DRLR. Цифра 32 в названии микросхемы и обозначает логический элемент “2ИЛИ”. Размеры корпуса этой микросхемы не превышают 1.6´1.6мм. В результате, несмотря на несколько более сложную принципиальную схему площадь, занимаемая счётчиком часов, значительно уменьшается. Полная принципиальная схема счётчика часовых импульсов, реализованная на микросхеме SN74HC393PW приведена на рисунке 4. Использование обратной связи с выводов Q1 и Q3 первой микросхемы превращает ее в десятичный счётчик. Для реализации счетчика по модулю 24 мы используем обратную связь с вывода Q1 старшего разряда счётчика (двойка) и вывода Q2 младшего разряда счётчика часов (четвёрка).  Рисунок 12.1.8. Схема счётчика часовых импульсов Таким образом, мы реализовали основную часть схемы часов, но как это уже обсуждалось при разработке структурной схемы этого недостаточно. Требуется уметь отображать полученную цифровую информацию. Перейдём к разработке блока индикации часов. Глава 3 |