Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

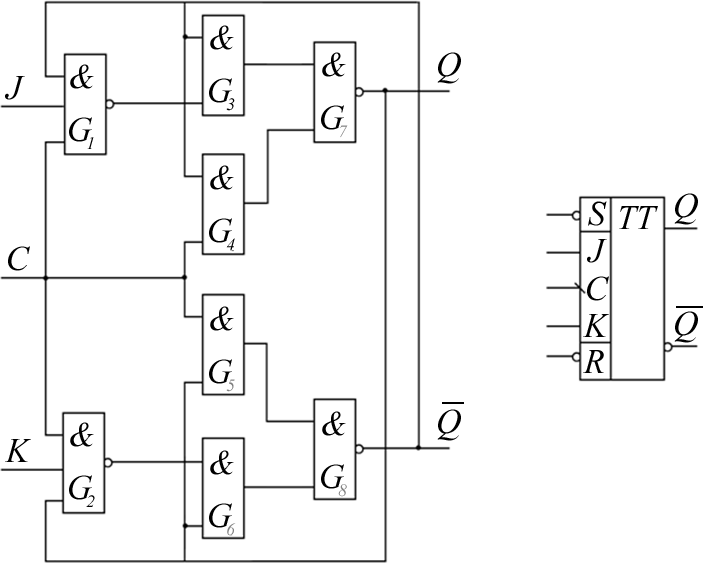

JK-триггер с динамическим управлениемJK-триггер с динамическим управлением может быть построен с ис- пользованием логической схемы рис. 6.17, а также и другой логической схе- мы, которая является основой для построения триггеров TB6, TB9, TB10, TB11. На рис. 6.20 представлена логическая схема и условное обозначение JK-триггера, подобного TB9.  а б Рис. 6.20. Логическая схема и условное обозначение JK-триггера с инверсным динамическим управлением Основным достоинством схемы (рис. 6.20,а)является то,что время удержания tуд для нее равняется 0, что повышает ее быстродействие. Рассмотрим особенности схемной реализации и работу этой схемы. Для нормального функционирования задержка распространения сигнала че- рез элементы G1 и G2 превышает суммарную задержку остальных элемен- тов И, ИЛИ-НЕ. Изменения состояния триггера происходят по отрицатель- ному перепаду синхросигнала, т. е. тактовый вход С триггера является ин- версным динамическим. Проанализируем работу схемы для J=K=1. Пусть триггер находится в состоянии (С=1), тогда на выходе элемента Qn=0, а на синхровходе действует лог. 1 G1 действует лог. 0, на выходе 3 ог.0G, на выходе 4 лог. 1G, которая гарантирует на выходе триггера Q=0. На инверс- ном выходе триггера установится 1, пQоскольку на выходах элементов G2 , G5 , G6 –уровень лог. 0. Теперь при переходе Сот лог.1 к лог. 0 (переход 1 0 ) на выходах элементов G3 и G4 устанавливается лог. 0, а на выходе G7 – лог. 1, т. е. вы- ход триггера G1n 1. Лог. 1 с выхода G7 поступает на вход G6 , на второй вход которого поступает лог. 1 с выхода G2 , поэтому на выходе G6 появля- ется лог.1, а на выходе лог. 0G, т.е. 0. QЛог. 0 с выхода элемента G8 8 поступает на вход элемента G3 прежде, чем на втором входе появится лог. 1 с выхода элемента G1, т. к. время распространения сигнала через элемент G1 больше, чем суммарное время распространения сигнала через элементы G3 – G8 . При возвращении синхросигнала в состояние лог. 1 (С=1) на выходах элементов G3 и G4 сохраняется лог. 0, т. к. на один из входов G3 и G4 по- ступает лог.0 с инверсного выхода триггера, что сохраняет на выходе Q=1. На выходе элемента G5 появляется лог. 1, обеспечивая сохранение на ин- версном выходе 0. QПри поступлении следующего отрицательного пере- пада синхросигнала плечи триггера работают аналогично. Таким образом, при J=K=1 триггер изменяет свое состояние на противоположное каждым от- рицательным перепадом синхроимпульса. ПОРЯДОК ВЫПОЛНЕНИЯ ЛАБОРАТОРНОЙ РАБОТЫ Оборудование и компоненты: универсальная лабораторная установка IDL-800; интегральные схемы: 1533ЛА3 (74ALS00) – четыре логических элемента 2И-НЕ, 1533ЛЕ1 (74ALS02) – четыре логических элемента 2ИЛИ- НЕ; 1533ЛА3 (74ALS10) – три логических элемента 3И-НЕ;1533 ТМ2 (74ALS74) – два синхронных динамических D-триггера;1533 TM7(74ALS75) – четыре D-триггера со статическим управлением; 1533 TB6 (74ALS107) – два синхронных динамических JK-триггера; 1533TP2 (74ALS279) – четыре син- хронных RS-триггера. |