Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

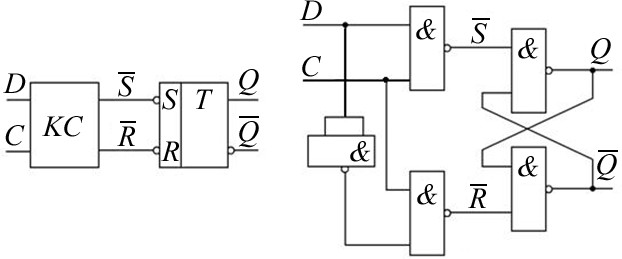

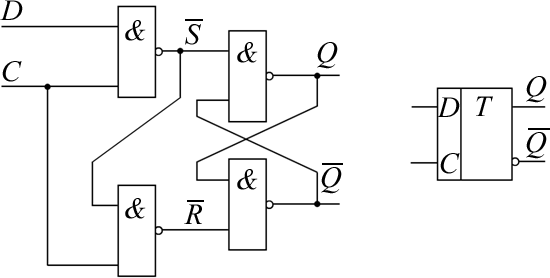

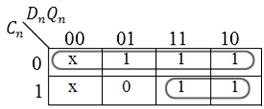

D-триггерD-триггер имеет информационный вход D (data, delay) и вход синхро- низации C. Триггер принимает информационные сигналы по разрешению синхросигнала и повторяет их на выходе с некоторой задержкой. Синтез синхронного D-триггера(D-latch)осуществим на основе базового асинхрон- ного RS-триггера. Блок-схема такого триггера показана на рис. 6.8, а.  а б а бРис. 6.8. Синхронный D-триггер со статическим управлением (окончание на с. 77)  в г Рис. 6.8. Окончание (начало см. на с. 76) Из блок-схемы (см. рис. 6.8, а) очевидно, что для получения логической схемы синхронного D-триггера со статическим управлением необходимо оп- ределить комбинационную схему (КС), генерирующую функции Sи Rта- кими, чтобы базовый RS-триггер функционировал как D-триггер. Для полу- чения КС составим таблицу истинности для функций Snи Rn, на основе таблицы истинности синхронного D-триггера со статическим управлением и таблицы переходов асинхронного RS-триггера(табл. 6.6) и с помощью карт Карно минимизируем выражения для Snи Rn.

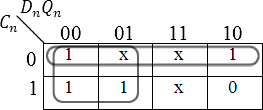

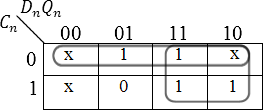

Таблица 6.6 SnCnDn DnCn;   RnCnDnDnCn. Используя выражения для Sи R, построим логическую схему син- хронного D-триггера со статическим управлением (рис. 6.8, б). Логическая схема синхронного D-триггера со статическим управлени- ем может быть упрощена, если при построении КС использовать не мини- мальное выражение для Rn, а как показано на рис. 6.9.  Rn RnCnCnDn  CnDnCn Рис. 6.9.Карта Карно для Rn При использовании для построения триггера выражений Sn DnCnи Rn  Cn DnCn получается логическая схема синхронного D-триггера со ста- тическим управлением, приведенная на рис. 6.8, в. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||