Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

6.1.1. Асинхронный RS- триггер (SR-latch)Это устройство с двумя устойчивыми состояниями, имеющее два входа S(Set– установка) и R(Reset– сброс) и два выхода Qи Q. Асинхронный триг- гер функционирует в соответствии с таблицей истинности (табл. 6.1). Таблица 6.1

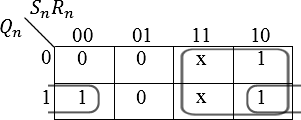

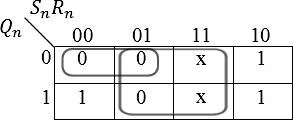

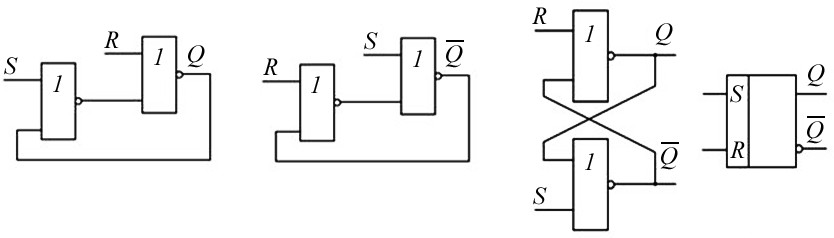

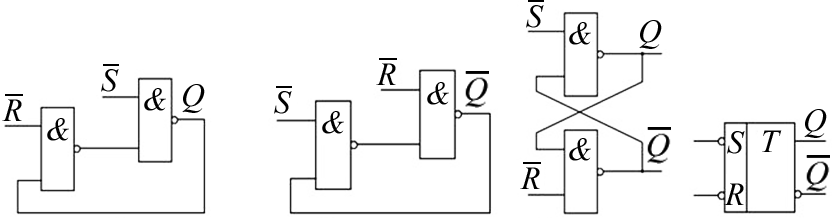

Если входы Snи Rnоба в состоянии лог. 0, то триггер не изменяет свое состояние, т. е. триггер хранит 1 бит информации. Если Sn=1 и Rn=0, то независимо от того, в каком состоянии триггер находился, следующее состояние триггера Q 1=n1. Если Sn=0 и Rn=1, то независимо от того, в каком состоянии находил- ся триггер, следующее его состояние Комбинация входных сигналов Rn= 0. Rn = Sn= 1 является неопределенной, поскольку триггер после воздействия на входах активных уровней может равновероятно перейти как в нулевое, так и в единичное состояние. Поэтому одновременная подача активных уровней на входы S и R не допускается. Работа RS-триггера также может быть представлена функцией на карте Карно и логическим уравнением. Входные и выходные переменные триггера в момент срабатывания tnи после срабатывания t1мnожно представить функциональной зависимостью Q 1=nf(Sn, Rn, Qn),(6.1) где Rn, Sn– состояние информационных входов; Qn– значение выходного сигнала триггера в момент времени tn ; Q1–nзначение выходного сигнала триггера в момент времени t 1.n Функция алгебры логики (см. табл. 6.1) может быть представлена кар- той Карно (рис. 6.1). Значения ФАЛ, показанные значком x, указывают на то, что данная ФАЛ является недоопределенной. При минимизации ФАЛ можно ее доопределить так, как нам это удобно, чтобы получить минимальную форму (см. рис. 6.1).   Qn1 SnQn Rn Qn1 RnQnSn Рис. 6.1.Карты Карно для минимизации выходных функций RS-триггера Выражения Qn1 SnQnRn; (6.2) Qn1 RnQnSn (6.3) используются для построения RS-триггера.  Применяя инверсию и закон де Моргана, выражения (6.2) и (6.3) могут быть преобразованы следующим образом: Применяя инверсию и закон де Моргана, выражения (6.2) и (6.3) могут быть преобразованы следующим образом: Qn1 Qn1 SnQn  RnQn RnQnRn; (6.4) Rn. (6.5) Выражения (6.4) и (6.5) используются для реализации RS-триггера на элементах ИЛИ-НЕ. Применяя двойную инверсию и закон де Моргана, выражения (6.2) и (6.3) могут быть преобразованы следующим образом: Qn1  SnQnRn; (6.6) Qn1  RnQnSn . (6.7) Выражения (6.6) и (6.7) используются для реализации RS-триггера на элементах И-НЕ. Реализация RS-триггера на элементах ИЛИ-НЕ показана на рис. 6.2, а,б.   Qn1 Qn1RnQn Rn Qn1  SnQnRn а б в г Рис. 6.2. RS-триггеры на элементах ИЛИ-НЕ Обычно RS-триггер изображается с расположением элементов ИЛИ-НЕ, как показано на рис. 6.2, в. На рис. 6.2, г показано условное изображение RS- триггера. При анализе работы RS-триггера и при синтезе других триггеров ис- пользуется таблица переходовRS-триггера(табл. 6.2),которая определяет комбинации входных сигналов, необходимых для того или иного перехода триггера, т. е. триггер в момент времени tnнаходится в каком-то состоянии ( Qn=0 или Qn=1), и определяются состояния входов, чтобы триггер перешел в определенное следующее состояние Q 1.n Таблица 6.2

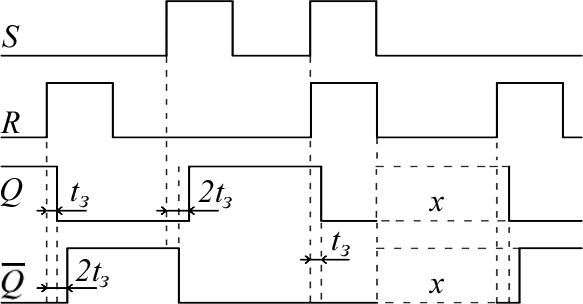

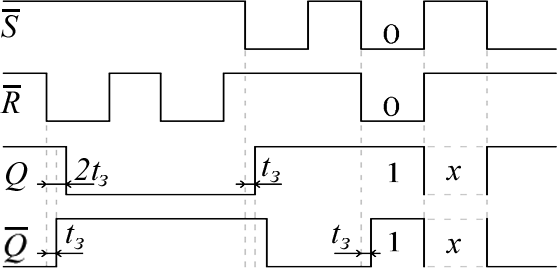

На рис. 6.3 приведены временные диаграммы, поясняющие принцип работы асинхронного RS-триггера (см. рис. 6.2).  Рис. 6.3. Временные диаграммы работы асинхронного RS-триггера Рис. 6.3. Временные диаграммы работы асинхронного RS-триггераДля устойчивого функционирования триггера длительность сигнала на входах Rи Sдолжна быть не меньше времени переключения триггера, t tзn. Информационные сигналы должны поступать на входы поочередно и только после окончания переходных процессов в триггере, тогда максимальная час- тота переключения триггера будет равна f 1 . (6.8) Однако при fmax max 2t3 длительность выходных сигналов не будет превышать tз.ср .Такие сигналы не являются достаточными для надежной передачи ин- формации в логическую цепь, поэтому максимальная рабочая частота триг- гера fp определяется как f 1  p 2t p 2t. (6.9) .ср 6.1.2 Асинхронный RS-триггер на элементах И-НЕ, RS -триггер ( S R -latch) Воспользуемся выражениями (6.6) и (6.7) и реализуем RS-триггер на элементах И-НЕ (рис. 6.4): Qn1  SnQnRn; Qn1  RnQnSn.  а б в г Рис. 6.4. Асинхронный RS-триггер: а, б – построение RS-триггера; в – изображение триггера на элементах И-НЕ; г–условное изображение RS-триггера RS-триггер на элементах И-НЕ (см. рис. 6.4), называется асинхронным триггером с инверсными входами. Характеристическая таблица или таблица истинности такого триггера представлена табл. 6.3, а таблица переходов – табл. 6.4.

Таблица 6.3 Таблица 6.4 На рис. 6.5 приведены временные диаграммы, поясняющие принцип работы асинхронного RS-триггера на элементах И-НЕ.  Рис. 6.5. Временные диаграммы работы RS-триггера | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||