Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

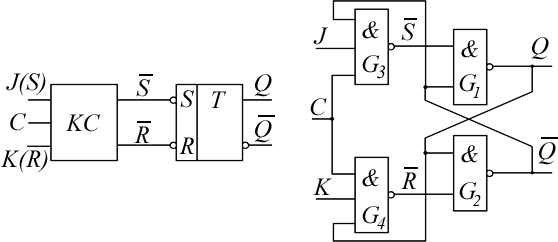

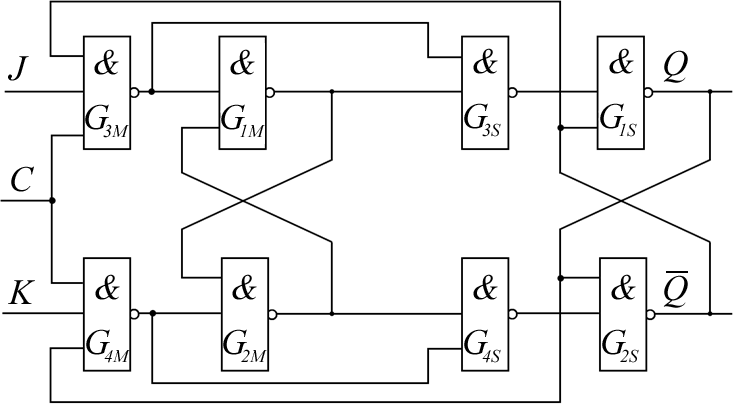

JK-триггерыJK-триггер – это модернизированный RS-триггер, в котором неопреде- ленное состояние RS-триггера доопределено таким образом, что при J=K=1 триггер переключается в противоположное состояние. При этом вход Jсоот- ветствует входу S, а вход K– входу R.  Рассмотрим синтез JK-триггера со статическим управлением, исполь- зуя базовый асинхронный RS-триггер. Блок-схема триггера приведена на рис. 6.10, а. Рассмотрим синтез JK-триггера со статическим управлением, исполь- зуя базовый асинхронный RS-триггер. Блок-схема триггера приведена на рис. 6.10, а.а б Рис. 6.10. Синхронный JK-триггер со статическим управлением Для синтеза JK-триггера со статическим управлением составим табли- цу истинности для функций Sи R(табл. 6.7). Таблица 6.7   Sn Rm CnQnJn CnQnKn

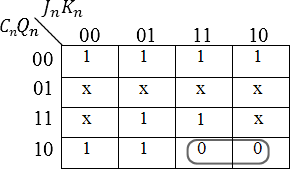

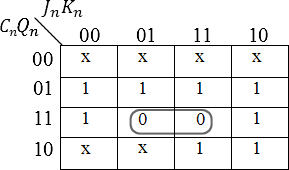

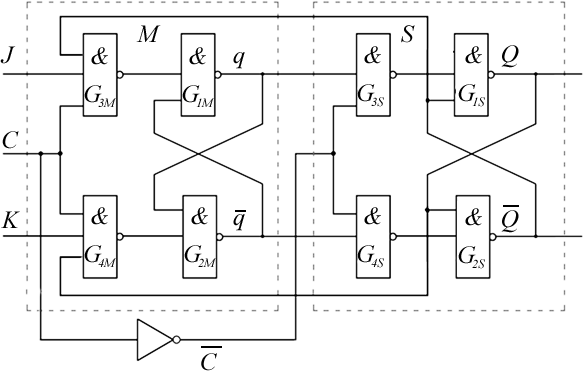

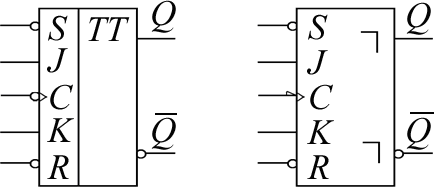

CnQnJn; CnQnKn. Минимизируем функции Snи Rnс помощью карт Карно и преобразу- ем их к форме, удобной для реализации с помощью элементов И-НЕ. Схема триггера приведена на рис. 6.10, б. Рассмотрим работу синхронного JK-триггера со статическим управле- нием, когда J=K=1 и на вход синхронизации поступают синхроимпульсы. Когда на входе Cуровень лог. 0, тогда на выходах логических элементов G3 и G4 уровни лог. 1 и асинхронный триггер на элементах G1 и G2 сохраняет свое состояние. Когда на вход Cпоступает импульс синхронизации, т. е. C=1, то импульс будет передаваться через один из логических элементов G3 или G4 , вход которого, соединенный с выходом триггера, будет в данный мо- мент равен лог. 1. Если Q=1, выход логического элемента G4 становится равным нулю, когда поступает импульс синхронизации, и триггер обнуляет- ся. Если Q=1, выход G3 становится равным нулю при подаче импульса син- хронизации и триггер устанавливается. В любом случае состояние триггера изменяется. Однако когда J=K=1, Q=0 и импульс синхронизации действует на вхо- де,то после временного интервала t,равного времени задержки распро- странения сигнала через два элемента И-НЕ ( G3 и G4 ), выход триггера изме- нится на Q=1. Теперь J=K=1 и Q=1, и после другого временного интервала выход будет изменяться на Q=0. Следовательно, можно сделать вывод, что в течение длительности tu(импульса синхронизации) схема рис. 6.10, б имеет неустойчивое состояние, т. е. находится в автоколебательном режиме, а после окончания импульса синхронизации состояние триггера будет неиз- вестно. Это говорит о том, что синхронный JK-триггер со статическим управлением не может быть реализован на одной элементарной запоминаю- щей ячейке. Казалось, этой ситуации можно было бы избежать, если бы tut T. Однако выполнить это невозможно ввиду очень малого времени задержки распространения сигнала в ИС. Поэтому практически используемыми JK-триггерами являются двух- ступенчатые управляемые синхроимпульсом триггеры и триггеры с динами- ческим управлением. Управляемые синхроимпульсом триггеры строятся по 2-ступенчатой M-S(Master-Slave) конфигурации. JK-триггер M-S типа состоит из каскада двух RS-триггеров с обратной связью с выхода второго на вход первого (рис. 6.11).  Рис. 6.11. Двухступенчатый JK-триггер с инвертором Когда С=1, первый триггер имеет разрешение и выходы qи qзависят от состояния входов J и K. В то же время на второй триггер подается запрет, поскольку C. Когда Сизменяется на низкий уровень, С=0 ( C=1), на первый триггер подается запрет, а на второй триггер – разрешение, поскольку теперь его синхровход C=1. Поэтому выходы Qи Qповторяют состояния на вы- ходах qи qсоответственно. Поскольку второй триггер всегда повторяет со- стояние первого, его назвали S(slave), а первый M(master). В этой схеме входы G3m Q и G4m Qне меняются в течение импульса синхрониза- ции,поэтому JK-триггер не может находиться в автоколебательном режиме. Состояние M-S-триггера изменяется при отрицательном перепаде импульса синхронизации. Имеется другая версия JK-триггера в конфигурации M-S(рис. 6.12)  Рис6.12.Двухступенчатый JK-триггер с запрещающими связями Условное обозначениеJK-триггера показано на рис. 6.13.  а б Рис. 6.13. Условное обозначение JK-триггера |