Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

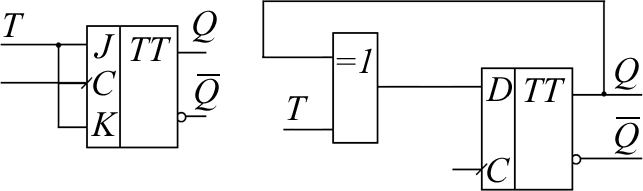

T-триггерыТ-триггер имеет один вход Т(trigger ortoggle). Т-триггер изменяет свое состояние на противоположное с каждым импульсом синхронизации,если T=1 и сохраняет свое состояние, если Т=0. Т-триггеры не производятся в ин- тегральном исполнении, но могут быть легко построены из JK- и D-триггеров. Исходя из определения Т- и JK-триггеров очевидно, что Т-триггер получа- ется из JK-триггера, если входы J и K объединить (рис. 6.15, а). Поэтому Т- триггер иногда рассматривают как одновходовый вариант JK-триггера . Для того чтобы преобразовать D-триггер в Т-триггер, воспользуемся таблицей переходов для обоих триггеров (табл. 6.8). Таблица 6.8

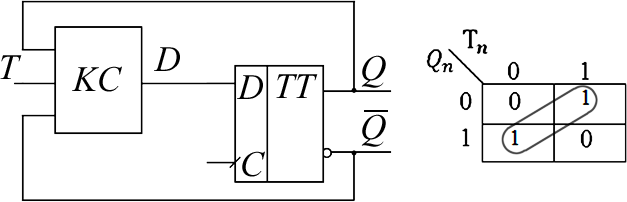

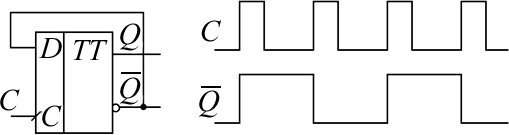

Блок-схема Т-триггера на основе D-триггера показана на рис. 6.14, а.  а б DnQn Tn Рис. 6.14. Блок-схема преобразования D-триггера в Т-триггер Из блок-схемы (см. рис. 6.14) очевидно, что необходимо синтезировать такую КС, чтобы D-триггер функционировал как Т-триггер. ФАЛ, описы- вающая эту КС, имеет входные переменные Tnи Qn, а выходная переменная Dn(см. табл. 6.8). Функция Dn( Qn,Tn) может быть представлена и упрощена с помощью карты Карно (рис. 6.14, б). В соответствии с полученным выражением DnQn Tn (6.10) cхема Т-триггера будет выглядеть, как показано на рис. 6.15, б.  а б Рис. 6.15. Т-триггер на основе J-K-триггера и на основе D-триггера Если вход T=1, то T-триггер меняет свое состояние всякий раз, когда поступает импульс синхронизации. Если переменная Tnв уравнении (6.10) равна 1, то уравнение может быть переписано следующим образом: 1 Dn QnQn. (6.11) Уравнение (6.11) показывает, что схему делителя на 2 можно построить простым соединением Qnс D-входом (рис. 6.16).  а б Рис. 6.16. Схема делителя на 2 и его временные диаграммы Необходимоотметить,чтоТ-триггернеможетбытьпостроенна основе триггера со статическим управлением (latch). |