Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

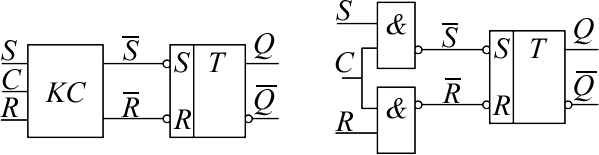

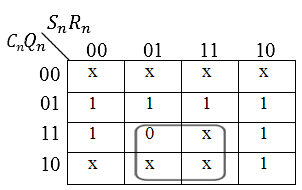

Синхронный RS-триггер (SR-latch) со статическим управлениемАсинхронный RS-триггер является элементарной запоминающей ячей- кой и используется при синтезе других более сложных триггеров. В том чис- ле синхронный RS-триггер со статическим управлением может быть синтези- рован на основе базового асинхронного RS-триггера с инверсными входами. В этом случае блок-схема синхронного RS-триггера со статическим управле- нием состоит из асинхронного RS-триггера и комбинационной схемы (КС), как показано на рис. 6.6, а.  а б Рис. 6.6. Синхронный RS-триггер со статическим управлением Задачей синтеза является определение функции Snи Rnи построение КС, которая соответствующим образом управляет работой асинхронного RS-триггера. Для этого построим таблицу истинности функций Snи Rn(табл. 6.5) и минимизируем эти функции с помощью карт Карно. Таблицу истинности для функций Snи Rn строим на основании таблицы истинности синхронного RS-триггера и таблицы переходов асинхронного RS-триггера.

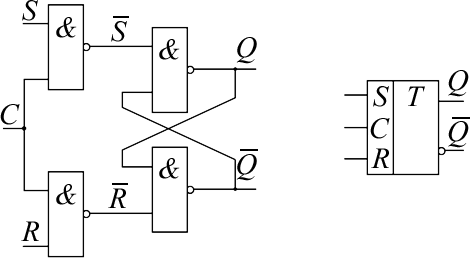

Таблица 6.5  SnCn Sn SnCn;  RnCnRn RnCn. На основании выражений для Sи Rблок-схема (см. рис. 6.6, а) преоб- разуется в логическую схему синхронного триггера со статическим управле- нием (рис. 6.6, б). Полная логическая схема синхронного триггера на эле- ментах И-НЕ и условное обозначение этого триггера показаны на рис. 6.7.  а б Рис. 6.7. Логическая схема и условное обозначение синхронного RS-триггера со статическим управлением |