Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

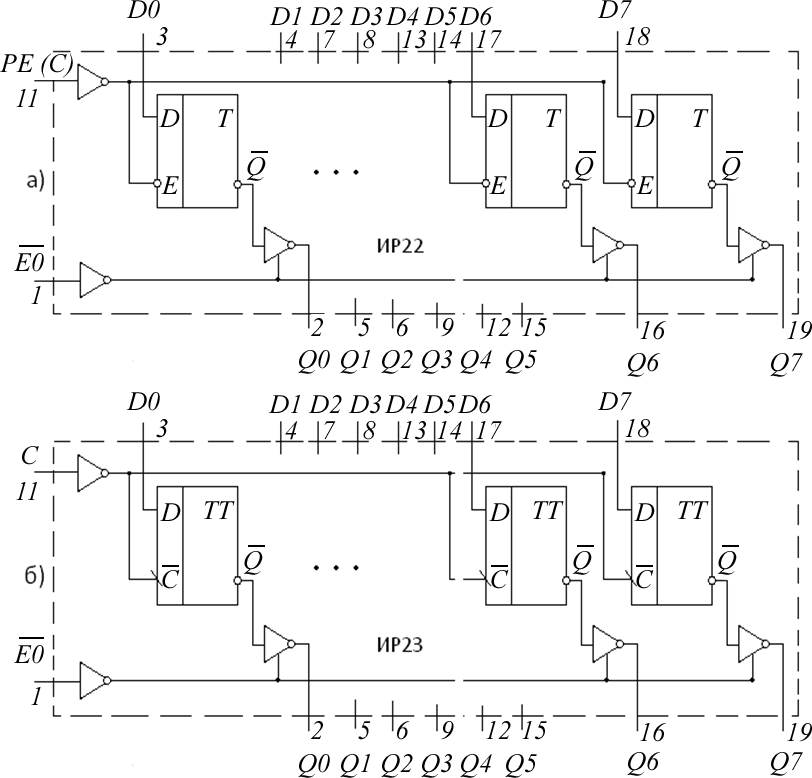

РЕГИСТРЫ И ИХ ПРИМЕНЕНИЕЦельработы: Изучение принципов построения регистров. Исследование режимов работы и применения регистров. ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ Триггер может хранить (запоминать) 1 бит цифровой информации (1 или 0). Его также можно назвать одноразрядным регистром. Группа тригге- ров, предназначенная для хранения двоичной информации (один триггер на каждый бит информации), называется регистром. Регистры находят приме- нение в различных цифровых устройствах, включая микропроцессоры. Данные могут вводиться в регистр (записываться) в последовательной форме (бит за битом) или в параллельной форме (все биты одновременно) и могут выводиться из регистра в последовательной или параллельной форме. Регистры классифицируются в зависимости от того, в какой форме ин- формация вводится в регистр и в какой форме выводится. Существует четыре возможности: Последовательно-последовательный регистр. Последовательно-параллельный регистр. Параллельно-последовательный регистр. Параллельно-параллельный регистр. Регистры стоятся с помощью триггеров(RS, JK, D)и широко представ- лены как ИС средней степени интеграции. Регистры, в которые данные вводятся или выводятся в последователь- ной форме, называются сдвигающими. Биты информации, находящиеся в триггерах регистра, сдвигаются то ли вправо, то ли влево при подаче синхро- импульсов. В некоторых регистрах информация может сдвигаться или впра- во, или влево в зависимости от специального управляющего сигнала. Такие регистры называются реверсивными. Если регистр может работать во всех четырех режимах и также как реверсивный, то такой регистр называется универсальным. Параллельные регистрыПредназначены для запоминания и хранения двоичной информации, поэтому параллельные регистры называют регистрами хранения или реги- страми памяти. Такие регистры осуществляют операции записи и считыва- ния информации параллельным кодом. Параллельные регистры могут ис- пользоваться в качестве буферных регистров, а также для преобразования прямого двоичного кода в обратный код и наоборот. При построении параллельных регистров могут использоваться син- хронные триггеры со статическим управлением (latch), а также синхрон- ные триггеры с динамическим управлением и двухступенчатыеRS-,JK-, D-триггеры.  На рис. 7.1 приведены структуры регистров ИР22 и ИР23. Микросхемы ИР22 и ИР23 – это восьмиразрядные параллельные регистры на D-триггерах. Причем регистр ИР22 построен на D-триггерах со статическим управлением, а ИР23 – с динамическим управлением. На рис. 7.1 приведены структуры регистров ИР22 и ИР23. Микросхемы ИР22 и ИР23 – это восьмиразрядные параллельные регистры на D-триггерах. Причем регистр ИР22 построен на D-триггерах со статическим управлением, а ИР23 – с динамическим управлением.Рис. 7.1. Логическая структура регистров ИР22, ИР23 Регистры ИР22 и ИР23 имеют выходные буферные усилители с тремя состояниями. Третье высокоимпедансное состояние Zможно установить с  помощью вывода разрешения EO(EnableOutput), если подать на него на- помощью вывода разрешения EO(EnableOutput), если подать на него на-пряжение высокого уровня. Выходные буферные усилители обладают высо- кой нагрузочной способностью. Регистры состоят из восьми D-триггеров с входами разрешения парал- лельной записи РЕ(PresetEnable) (для ИР23 – вход С). Если на входе РЕ действует высокий уровень напряжения, то данные от входов D0–D7записы- ваются в триггеры регистра.  Если на вход EOподано напряжение низкого уровня, то данные из Если на вход EOподано напряжение низкого уровня, то данные изD-триггеров регистра пройдут на выходы Q0– Q7. Регистр ИР23 принимает информацию синхронно с положительным перепадом тактового импульса, подаваемого на вход С. В настоящее время выпускается большое количество регистров разно- образного назначения. Однако наиболее универсальными являются регистры, которые могут работать во всех четырех режимах. Примером такого регистра может быть микросхема ИР16. |