Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

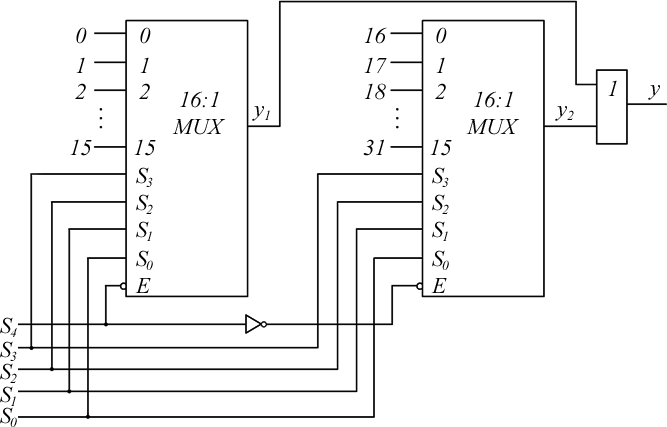

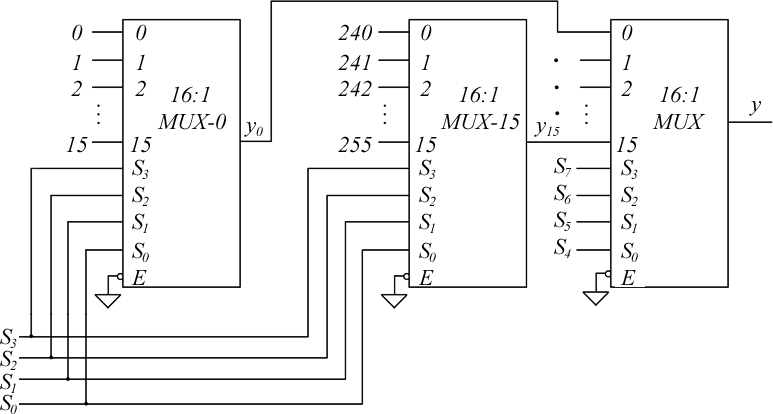

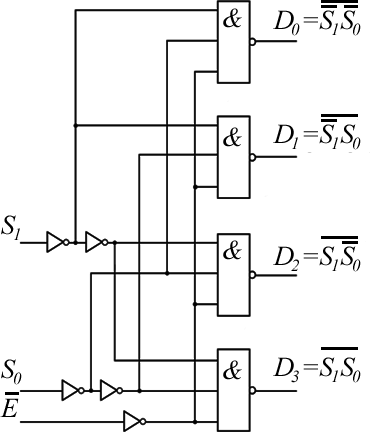

Увеличение размерности мультиплексораМаксимальный размер мультиплексора, выпускаемого промышленно- стью, 16:1. Мультиплексоры с большим числом входов можно построить из мультиплексоров с меньшим числом входов. Используются два метода, ко- торые мы проиллюстрируем следующими примерами. Пример 5.3. Построить мультиплексор размерностью 32:1. Такой мультиплексор можно построить (рис. 5.6), используя два мультиплексо- ра 16:1.  Рис. 5.6. Мультиплексор 32:1 с использованием Рис. 5.6. Мультиплексор 32:1 с использованиемдвух мультиплексоров 16:1  Пример 5.4. Построить мультиплексор размерностью 256:1. Такой мультиплексор можно построить по древовидной схеме, используя 17 муль- типлексоров 16:1, рис. 5.7. Пример 5.4. Построить мультиплексор размерностью 256:1. Такой мультиплексор можно построить по древовидной схеме, используя 17 муль- типлексоров 16:1, рис. 5.7.Рис. 5.7. Мультиплексор 256:1с использованием 17 мультиплексоров 16:1 Декодеры/демультиплексоры и их использование в синтезе комбинационных схемВ интегральном исполнении декодеры (дешифраторы) реализуются с использованием элементов И-НЕ, и поэтому на выходах таких декодеров ге- нерируются минтермы в инверсном виде. Большинство интегральных деко- деров имеют один или несколько стробирующих или разрешающих входов. Схема декодера 2:4 с разрешающим входом, построенная на элементах И-НЕ, показана на рис. 5.8.  Рис. 5.8. Логическая схема декодера 2:4 с разрешающим входом E Таблица истинности декодера 2:4 дана в табл. 5.3. Если разрешающий вход E1, то все выходы декодера равны 1 неза- висимо от значения входов S1 и S0 . Когда разрешающий вход 0, Eсхема работает как декодер с инверсными выходами. Условное обозначение схемы показано на рис. 5.9. Таблица5.3

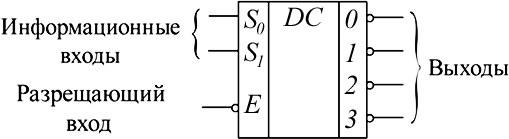

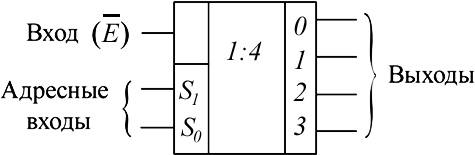

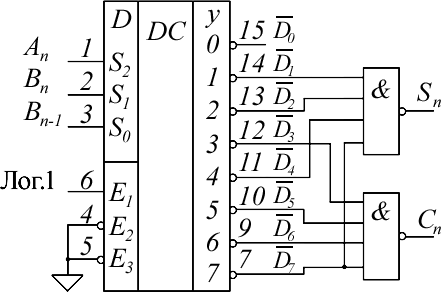

Рис. 5.9. Условное обозначение декодера 2:4 Декодер с разрешающим входом может работать как демультиплексор. Демультиплексор – это комбинационная схема, которая принимает информа- цию на единственный вход и передает эту информацию на один из 2m возможных выходов. Выбор определенного выхода осуществляется с помо- щью адресных входов. Декодер может работать как демультиплексор, если вход Eиспользовать как информационный вход, а информационные входы декодера S1 и S0 – как адресные входы. Условное обозначение демультип- лексора показано на рис. 5.10.  Рис. 5.10. Условное обозначение схемы рис. 5.9, используемой как демультиплексор Информация с единственного входа демультиплексора поступает на один из выходов в зависимости от двоичных значений на адресных входах. Это можно проверить, используя таблицу истинности ( см. табл. 5.3). Поскольку для декодера и демультиплексора используется одна и та же логическая схема, декодер с разрешающим входом называется декоде- ром/демультиплексором.Демультиплексор осуществляет операцию,обрат- ную мультиплексору. Декодеры/демультиплексоры используются в синтезе комбинацион- ных схем. Особенно эти устройства полезны при синтезе КС с несколькими выходами. Декодеры/демультиплексоры в интегральном исполнении воз- можны как 2:4, 3:8 и 4:16 линий. Выходы таких устройств, как правило, имеют низкий активный уровень. Рассмотрим использование декодеров/демультиплексоров в синтезе комбинационных схем. Пример. 5.5.Реализовать схему полного сумматора, используя деко- дер/демультиплексор. Решение. Из таблицы истинности для полного сумматора Sn An Bn Cn1 An Bn Cn1 An Bn Cn1 An Bn Cn1 ; Cn An Bn Cn1 An Bn Cn1 An Bn Cn1 An Bn Cn1. Используя двойную инверсию и закон де Моргана, преобразуем эти выражения:  Sn An Bn Cn1 An Bn Cn1 An Bn Cn1 An Bn Cn1 ; (5.3) Sn An Bn Cn1 An Bn Cn1 An Bn Cn1 An Bn Cn1 ; (5.3) Cn An Bn Cn1 An Bn Cn1 An Bn Cn1 An Bn Cn1 . (5.4) Cn An Bn Cn1 An Bn Cn1 An Bn Cn1 An Bn Cn1 . (5.4)или функция Snможет быть записана как S D1 D2 D4 D7 , а функция Cn может быть записана как C D3 D5 D6 D7 . Для реализации полного сумматора необходимо использовать деко- дер/демультиплексор 3:8 линий, например КР1533ИД7(SN74ALS138). Схема полного сумматора показана на рис. 5.11.  Рис. 5.11. Реализация полного сумматора с использованием декодера/демультиплексора При синтезе КС с использованием мультиплексоров дополнительные элементы не используются, в то время как их необходимо использовать при синтезе КС на основе декодеров/демультиплексоров. Тем не менее декоде- ры/демультиплексоры являются более экономичными при синтезе многовы- ходовых КС. В таких случаях один мультиплексор требуется для реализации каждого выхода, а при использовании декодера/демультиплексора – только дополнительные схемы И-НЕ. |