Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

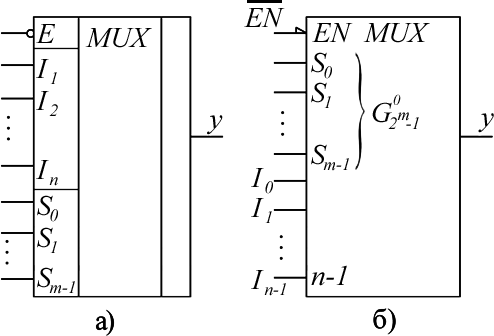

МультиплексорыМультиплексор (или селектор данных) – это комбинационная схема, которая коммутирует один из 2 mвходных сигналов на один выход. Выбор информационного входа, который коммутируется на выход, осуществляется с помощью адресных входов. Условные обозначения мультиплексора по- казаны на рис. 5.1.  Рис. 5.1. Условное обозначение мультиплексора: а – используемое в отечественной справочной литературе; б –рекомендуемое к использованию международным стандартом IEEE Для выбора одного из nвходов, коммутируемого на выход, требуется группа из адресных входов,где 2m .В зависимости от цифрового ко- да на адресных входах один из входов выбирается и соединяется с выходом. Обычно стробируемый (G) или разрешающий (EN) вход используется для каскадного соединения мультиплексоров. Этот вход обычно активный при низком уровне, т. е. разрешает работу мультиплексора, когда сигнал на этом входе низкий, лог. 0. Число информационных входов, коммутируемых на выход Y, со- ставляет 2,4,8,16 . При n 4 мультиплексор имеет размерность 4:1. Это 4-канальный одноразрядный мультиплексор, на выход которого переда- ется один из четырех входных сигналов. Рассмотрим, как построить мульти- плексор 4:1, таблица истинности которого приведена в табл. 5. 1. Таблица 5.1

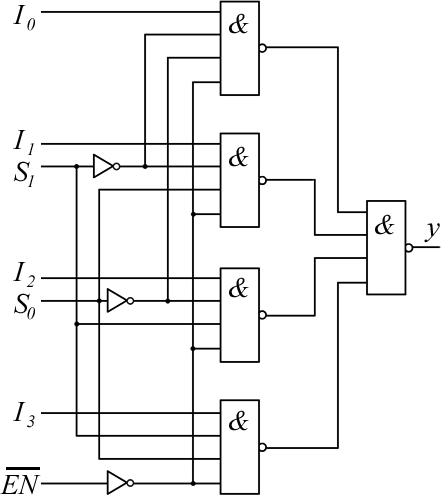

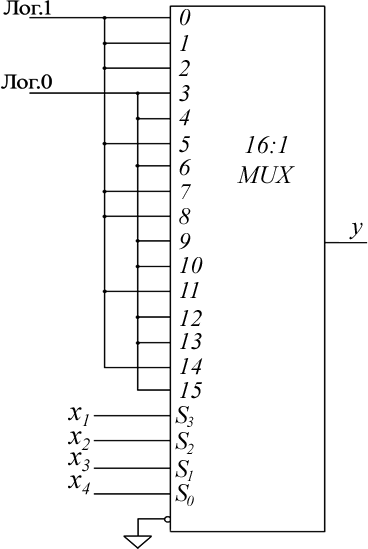

Выход Yможет быть записан как Y (S1 S0 I0 S1 S0 I1 S1S0 I2 S1 S0 I3) . (5.1) Выражение (5.1) преобразуем, используя двойную инверсию и закон де Моргана :  Y S1S0 I0 S1 S0 I1 S1 S0 I2 S1 S0 I3 . (5.2) Выражение (5.2) реализуется, как показано на рис. 5.2.  Рис. 5.2. Логическая схема мультиплексора 4:1 с разрешающим входом EN Промышленностью выпускаются мультиплексоры размерностью 8:1 и 16:1 со стробирующим входом и без него, а также двухразрядные мультип- лексоры 4:1 и четырехразрядные мультиплексоры 2:1. Мультиплексоры могут быть использованы как логические элементы для синтеза комбинационных схем. Использование мультиплексоров дает следующие преимущества: не требуется упрощение ФАЛ; минимизируется число требуемых интегральных схем; синтез КС упрощается. Для реализации КС с использованием мультиплексора требуется пред- ставление ФАЛ таблицей истинности или в СДНФ, или в СКНФ. Синтез КС сводится к следующему Определяется десятичные номера каждого минтерма ФАЛ и входы мультиплексора, соответствующие этим номерам соединяются с лог. 1. Все остальные входы соединяются с лог. 0. Входные переменные ФАЛ подаются на адресные входы. Пример 5.1. Реализовать следующую ФАЛ, используя мультиплексор f( 1, 2 , 3 , 4) m(0,1,2,5,7,8,11,14) . Решение.ФАЛ четырех переменных, поэтому мультиплексор должен быть с четырьмя адресными входами (рис. 5.3).  Рис. 5.3. Реализация ФАЛ f( 1, 2 , 3 , 4) из примера 5.1 | ||||||||||||||||||