Цифровыеустройства. Технология idl

Скачать 3.16 Mb. Скачать 3.16 Mb.

|

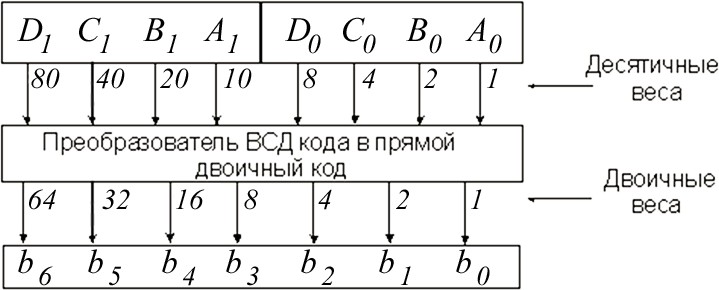

Преобразователь ВСD-кода в прямой двоичный кодРассмотрим схему преобразования ВСD-кода в двоичный код, показан- ную на рис. 4.7. Входами являются две тетрады: 0 СD0 В0 А0 , представляю- щая единицы, и 1 С1DВ1А1, представляющая десятки. Выходом является се- миразрядный двоичный код в6в5в4в3в2в1в0 . На схеме показаны также вес ка-  ждого ВСD-входа и каждого двоичного выхода. Разряды в двоично- десятичном представлении имеют десятичный вес 8,4,2,1 в каждой тетраде, однако каждая тетрада отличается от предыдущей весовым коэффициентом – 10 (одна десятичная цифра от предыдущей). ждого ВСD-входа и каждого двоичного выхода. Разряды в двоично- десятичном представлении имеют десятичный вес 8,4,2,1 в каждой тетраде, однако каждая тетрада отличается от предыдущей весовым коэффициентом – 10 (одна десятичная цифра от предыдущей).Рис. 4.7. Схема преобразования двухразрядного ВСD-кода в прямой двоичный код Десятичные веса каждого бита в двоично-десятичном представлении (рис. 4.7) могут быть представлены двоичными эквивалентами, как приведе- но в табл. 4.3. Используя эти веса, можно осуществить преобразование дво- ично-десятичного кода в двоичный путем двоичного суммирования двоич- ных эквивалентов тех бит, которые в BCD-представлении равны единицам. Таблица4.3

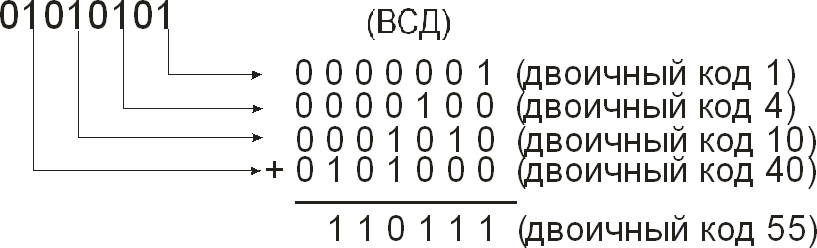

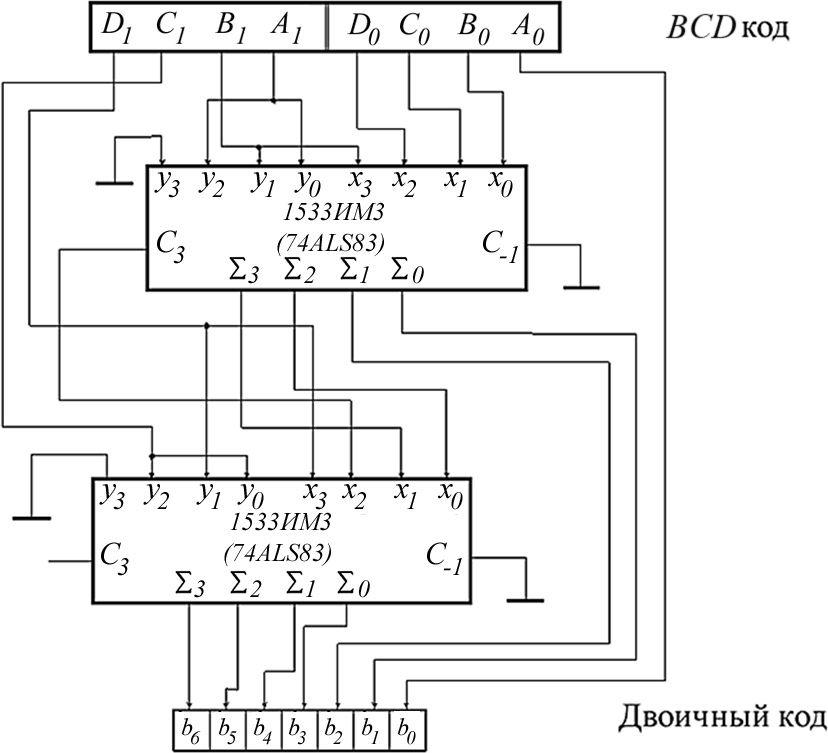

Например, преобразуем 01010101 (двоично-десятичное представление десятичного 55) в двоичный эквивалент. Для этого запишем двоичные экви- валенты для всех «1» в двоично-десятичном представлении, а затем просум- мируем их.  Отсюда следует один из способов реализации преобразователя двоич- но-десятичного ВСD-кода в прямой двоичный с помощью двоичных сумма- торов. На рис. 4.8 показана схемная реализация такого преобразователя с по- мощью двух четырехразрядных двоичных сумматоров 1533ИМ3(74АSL83).  Рис. 4.8. Преобразователь двоично-десятичного в двоичный код Рис. 4.8. Преобразователь двоично-десятичного в двоичный кодПОРЯДОК ВЫПОЛНЕНИЯ ЛАБОРАТОРНОЙ РАБОТЫ Оборудование и компоненты: универсальная лабораторная установка IDL-800, ИС 1533ЛП5(74АLS86) – четыре двухвходовых логических элемен- та ИСКЛЮЧАЮЩЕЕ ИЛИ; ИС 1533ИМ3(74АLS83) – четырехразрядный двоичный сумматор. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||